- •5. Дешифраторы.

- •10. Цифровые компараторы

- •8. Сумматоры

- •9. Вычитатели.

- •11. Перемножители

- •17. Разновидности регистров. Параллельные регистры.

- •15. Счётчики.

- •16. Реверсивные счётчики.

- •18. Сдвиговые регистры.

- •19. Реверсивные регистры.

- •20. Запоминающие устройства. Разновидности, характеристики.

- •21. Структуры зу.

- •23. Пзу и ппзу.

- •25. Озу типа fram

- •26. Плис. Общие понятия. Разновидности.

- •27. Программируемые логические матрицы (pla).

- •28. Программируемая матричная логика (pal), базовые матричные кристаллы (ga).

- •29. Программируемые вентильные матрицы (fpga). Программируемые коммутируемые матричные блоки (cpld)

- •Программируемые вентильные матрицы

- •31. Плис типа «система на кристалле (SoC).

- •32. Цап. Общие положения. Погрешности цап.

- •33. Цап с суммирование токов.

- •34. Цап типа r-2r.

- •35. Сегментированные цап.

- •36. Цифровые потенциометры. Цап прямого цифрового синтеза.

- •37. Ацп. Общие положения. Параметры ацп. Погрешности ацп.

- •38. Разновидности ацп. Параллельные ацп.

- •39. Ацп поразрядного уравновешивания.

- •40. Конвейерные ацп.

1. Цифровой сигнал — сигнал, имеющий только два состояния — «высокое» (1) и «низкое» (0), представляющий собой послед-ть 0 и 1. Цифровой сигнал сложнее передавать на большие расст-я, чем аналоговый сигнал, поэтому его предварительно модулируют на стороне передатчика, и демодулируют на стороне приёмника.

К

основным параметрам логических элементов

относятся: напряжение нуля, напряжение

единицы, быстродействие, граничная

частота, время переключения (0→1 и 1→0

зависит от времени задержки переднего

и заднего

и заднего

фронтов и определяется из выражения

tЗ = (tЗ1+ tЗ2)), максимальные входные токи

при 1 и 0, помехоустойчивость, коэффициент

разветвления (количество входов

элемента). Помехоустойчивость – величина

помехи, которую не чувствует элемент.

фронтов и определяется из выражения

tЗ = (tЗ1+ tЗ2)), максимальные входные токи

при 1 и 0, помехоустойчивость, коэффициент

разветвления (количество входов

элемента). Помехоустойчивость – величина

помехи, которую не чувствует элемент.

В настоящее время при разработке интегральных схем (ИС) наибольшее распространение получили следующие типы логических элементов:

– транзисторно-транзисторная логика (ТТЛ);

– транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ);

– эмиттерно-связанная логика (ЭСЛ);

– интегрально-инжекторная логика (И2Л);

– логика на комплементарных полевых транзисторах (КМОП).

Наиболее распространенными являются ТТЛ (ТТЛШ) и КМОП.

Потенциальный способ представления логического «0» и логической «1» при положительной логике :

инвертор; повторитель; логическое сложение (ИЛИ);

инверсия

суммы (ИЛИ-НЕ); логическое умножение

(И); инверсия произведения (И-НЕ); сложение

по модулю 2 (исключающее ИЛИ,

неравнозначность):

;

;

.

.

Различают следующие статические характеристики ЛЭ:

1. IВХ = f(UВХ) – входная характеристика элемента, характеризующаяся входным сопротивлением логического элемента. Сопротивление RВХ различно при подаче низкого и высокого уровней сигнала обычно при высоком уровне сигнала RВХ больше.

2. UВЫХ = f(IВЫХ) – нагрузочная (выходная) характеристика (рис. 18.5). Её угол наклона определяется выходным сопротивлением ЛЭ.

3. UВЫХ

= f(UВХ)

– переходная

характеристика,

или амплитудная

передаточная характеристика

ЛЭ. Амплитудная передаточная характеристика

инвертирующего ЛЭ ТТЛ-типа с положительной

логикой ( )

)

-------------------------------------------------------------------------------------------

2. Транзисторно-транзисторная логика (ТТЛ) — способ преобразования дискретной информации с помощью электронных устройств, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала.

ТТЛ-транзистор имеет множество эмиттеров. Эти эмиттеры выполняют роль входных диодов, на базу подаётся опорное напр-е единицы кот-е сравн-ся диодами с входным, коллектор транзистора - корпус (реже - питание). Достоинства ТТЛ: высокое быстродействие, надежность, радиационную стойкость. Недостатки: наличие резисторов, большая площадь на кристалле, большая потребляемая мощность, наличие паразитных транз-ов. ТТЛШ-логика отличается от ТТЛ наличием диодов Шоттки в цепях база коллектор, что исключает насыщение транзистора, а также наличием демпфирующих диодов Шоттки на входах для подавления импульсных помех. Основные параметры и характеристики те же что и в ТТЛ, но быстродействие у ТТЛШ в 3-4 раза лучше.

|

Схема на диодах. Схема ТТЛ-элемента с простым инвертором, выполняющая логическую операцию И-НЕ. если на один из входов или на оба подать низкий уровень напр-я, то ток базы тр-ра VT2 будет равен 0, и на коллекторе тр-ра VT2 будет высокий уровень напр-я. Если на оба входа подать высокий уровень напр-я, то через базу VT2 тр-ра будет протекать большой базовый ток и на коллекторе тр-ра VT2 будет низкий уровень напр-я, т. е. данный элемент реализует функцию И-НЕ. |

|

Если на один или оба входа одновр-но подан низкий уровень напр-я, то многоэмиттерный тр-р находится в состоянии насыщения и тр-р VT2 закрыт, а, следовательно, закрыт и тр-р VT4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор VT2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора VT4 и запиранию тр-ра VT3, т. е. реализуется ф-ия И-НЕ. |

Элементы с тремя состояниями и с открытым коллектором. Вентили ТТЛ и КМОП имеют двухтактные выходные схемы: ВЫСОКИЙ или НИЗКИЙ уровень подается на выход через открытый биполярный или МОП-транзистор. Такую схему, которая носит название активной нагрузки, а в ТТЛ называется также столбовым выходом, используют почти все логические элементы. Эта схема обеспечивает низкое выходное сопротивление в обоих состояниях, имеет малое время переключения и обладает более высокой помехоустойчивостью по сравнению с одиночным транзистором, который использует в качестве коллекторной нагрузки пассивный резистор.

В выходной схеме вентиля с открытым коллектором отсутствует транзистор, являющийся активной нагрузкой (рис. 18.10).

Иногда возникает необходимость логического объединения выходов очень большого числа элементов. Тогда используются логические элементы с открытым коллектором. В качестве выходного каскада они содержат эмиттер которого соединен с общей точкой. Выходное напряжение имеет высокий уровень только тогда, когда все выходные транзисторы элементов заперты - реализуется функция ИЛИ.

Недостаток: переход в высокоомное (единичное) состояние из-за паразитных емкостей происходит всегда медленнее, чем в низкоомное (нулевое). Вместо элементов с открытым коллектором используют элементы с трехстабильным выходом. Они содержат обычный двухтактный выходной каскад, который, однако, может быть переведен в особое высокоомное состояние (высокоимпедансное состояние или обрыв). Для управления выходным каскадом служит специальный вывод – разрешение выдачи данных.

-------------------------------------------------------------------------------------------

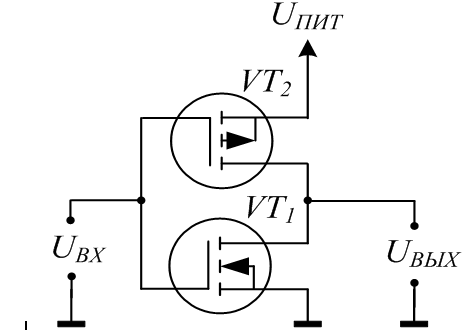

3. КМОП – комплементарная МОП, предполагает одновременное использование МОП транзисторов и с p- и с n-проводимостью. Второй закрытый транзистор – резистор с большим R и не влияет на уровень выходных сигналов. Работа схемы не зависит от уровня Uпит(3-15В). Достоинства: высокая помехоустойчивость, входные (затворные) цепи практически не потребляют тока. Недостатки: низкое быстродействие.

В основе МОП-логики, лежат ключевые схемы на МОП-транзисторах. В них за уровень логического 0 принимается напряжение на открытом транзисторе 0,05 – 0,15 В. За уровень логич. 1 принимают U, близкое к U питания схемы. Большая разница между уровнями 0 и 1 значительно повышает помехоустойчивость схемы по сравнению с логикой ТТЛ.

Простейший элемент – инвертор:

Реализация функции НЕ

В качестве нагрузочного транзистора Т2 используется р - канальный транзистор, а в качестве управляющего Т1, с каналом n -типа. КМОП инвертор работает на полож. логике. Т2 всегда закрыт по току. Мощность КМОП - инвертора меньше нем МОП - инвертора, т.е. от источника напряжения почти не происходит потр. энергии. |

Реализация функции ИЛИ - НЕ

Комплементарные пары: Т1 – Т11 , Т2 – Т22. Функ-ю ИЛИ реализует параллельное соединение n-канапьных тр-ров. Если хотя бы один из тр-ров в последовательной цепочке Т11-Т22 закрыт, то на выходе 0. |

Реализация функции И - НЕ

|

Комплементарные пары: Т1 – Т11 , Т2 – Т22. Функцию И реализует последовательное соединение n-канальных транзисторов. Если хотя бы один из транзисторов в параллельном соединении Т11-Т22 открыт, то на выходе 1 |

4. Шифратор – устройство для преобразования унитарного позиционного (активный сигнал только на одном выходе) кода в параллельный. Шифраторы относятся к комбинационным микросхемам, выходное состояние которых однозначно определяется входным состоянием блока (без памяти).

Обозначение на схеме: CD (coder)

Классический

шифратор имеет m входов и n выходов, и

при подаче сигнала на один из входов

(на один, и не более) на выходе появляется

двоичный код номера возбужденного

входа. Число входов и выходов такого

шифратора связано соотношением m= .

На выходе шифратора устан-ся двоичный

код, соответств-ий десятичному номеру

возбужденного информационного входа.

.

На выходе шифратора устан-ся двоичный

код, соответств-ий десятичному номеру

возбужденного информационного входа.

Cхема шифратора, использующая элементы ИЛИ.

Y1 = X1 + X3 + X5 + X7, Y2 = X2 + X3 + X6 + X7,

Y3 = X4 + X5 + X6 + X7

5. Дешифраторы.

Дешифратор – устройство для преобразования параллельного кода в позиционный унитарный (активный сигнал только на одном выходе). Шифраторы относятся к комбинационным микросхемам, выходное состояние которых однозначно определяется входным состоянием блока (без памяти).

Обозначение на схеме: DC (decoder).

Дешифратор: полный

( ),

неполный (

),

неполный ( )

)

Виды дешифраторов: Линейные, Пирамидальные, Многоступенчатые

Параметры дешифраторов: Время дешифрации, Кол-во используемых логич. элм-ов.

Основные достоинства: использование только двухвходных элементов. Недостаток: низкое быстродействие.

-------------------------------------------------------------------------------------------

6. Мультиплексор – Мультиплексор – устройство, коммутирующее в желаемом порядке информацию, поступающую с нескольких входов. Мультиплексор обладает двумя типами входов: управляющие и информационные.

У мультиплексоров, выпускаемых в виде самостоятельных изделий, число информационных входов не превышает 16. Большее число входов обеспечивается путем наращивания. Два сопособа наращивания: объединение нескольких мультиплексоров в пирамидальную систему, либо последовательным соединением разрешающих входов и внешних логических элементов.

Пирамидальный характер состоит в том, что каждая ступень, начиная с первой, имеет больше входов, чем последующая. Недостатки: Много микросхем, невысокое быстродействие.

Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах.

Рассмотрим функционирование четырехвходового мультиплексора (4→1), который условно изображен в виде коммутатора рис.,а, а состояние его входов D1, D2, D3, D4 и выхода Y приведено на рис. б. Исходя из таблицы, можно записать следующее уравнение:

Четырехвходовый мультиплексор: условное графическое обозначение (а) и его реализация на логических элементах (б)

10. Цифровые компараторы

Цифровые компараторы (от английского compare – сравнивать) выполняют сравнение 2-х чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В завис-ти от схемного исполнения компараторы могут определять рав-во А==В или нерав-ва А<В, А>В. Рез-тат сравнения отображается в виде логич-го сигнала на одноименных вых-ах. Цифровые компараторы применяются для выявления нужного числа в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислит-х устр-ах, а также в адресных селекторах.

A |

B |

F |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Переключательную функцию F позволяют реализовать логические двухвходовые элементы "Исключающее ИЛИ". На рис. 22.8 показан один из вар-ов реализации схемы сравнения.

,

,

![]()

,

,

,

,

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1• F2 • F3 • F4 = 1. Если же F = 0, то А ≠ В.

Нер-во А > В обеспеч-ся (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > B1 (где А4 и В4 – старшие разряды чисел А и В). Если поменять местами Ai и Вi, то будет выполняться неравенство А < В.

Представленные микросхемы являются четырехразрядными компараторами, в которых каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данные микросхемы имеют расширяющие входы А < В, А = В, А >В, что позволяет наращивать разрядность обоих чисел.

-------------------------------------------------------------------------------------------

7. Демультиплексор – устр-во в котором сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам. Выбор выходной линии осуществляется при помощи сигналов, поступающих на адресные входы. Бывают полными и неполными.

Демультиплексоры в виде самостоятельных ИС не изготавливаются, т.к. их функции могут выполняться дешифратором.

Для наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров.

При наличии на адресных шинах А0 и А1 нулей информационный вход X подключен к верхнему выходу DMX и в зависимости от состояния адресных шин А2 и А3 он может быть подключен к одному из выходов DMX1. Так, при А2 = А3 = 0 вход X подключен к Y3. При A0 = 1 и A1 = 0 вход X подключен к DMX2, в зависимости от состояния А2 и А3 вход соединяется с одним из выходов Y4 → Y7 и т. д.

Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы – ИД.

Дешифратор

может быть использован как демультиплексор, т.е. функциональный узел комбинационного типа, позволяющий коммутировать двоичный сигнал из одного в N каналов. При этом номер коммутируемого канала определяется адресным двоичным кодом. Так, комбинация X3, X2, X1, X0 определяет номер выхода дешифратора, который может быть скоммутирован с одним из входов E1 или E2. Например, при подаче E2=0 информация по E1 передается на соответствующий выход дешифратора. Остальные выходы постоянно находятся в состоянии логической единицы. Так, при X3, X2, X1, X0 = 0101 информация со входа «D» поступает на пятый выход дешифратора, причем в случае необходимости второй вход стробирования может быть использован для выборки ИС – дешифратора, например с целью увеличения количества коммутируемых каналов. В этом случае можно поступить так же, как и при увеличении разрядности дешифратора.

Так мультиплексор-демультиплексор

содержит два четырехвходовых мультиплексора 4→1, которые могут использоваться и как демультиплексоры 1→4.

Микросхема содержит один общий инверсный вход разрешения (стробирования) и два общих адресных входа. При логической 1 на входе разрешения выходы отключаются от информационных входов и переходят в высокоимпедансное состояние.

При активизации входа разрешения, т. е. при подаче на него логического 0, происходит соединение одного из информационных входов (в соответствии с кодом на адресных входах) с выходом микросхемы. Поскольку это состояние происходит при помощи двунаправленных ключей на КМОП-транзисторах, то сигнал может передаваться как со входов на выход (режим мультиплексора), так и с выхода нa входы (режим демультиплексора).

-------------------------------------------------------------------------------------------