- •Основы Информационно Вычислительных Комплексов

- •Оглавление

- •Арифметические основы

- •Система счисления.

- •Позиционные системы счисления.

- •Выбор системы счисления.

- •Перевод чисел из одной системы счисления в другую.

- •Перевод чисел из одной системы счисления в другую, когда одно основание является целой степенью другого.

- •Классификация параллельных вс

- •"Фон-Неймановские" и "не-Фон-Неймановские" архитектуры

- •Системы с общей и распределенной памятью

- •Способы межмодульного соединения (комплексирования)

- •"Исторические" модели Векторная вс пс-2000

- •Матричные вс

- •Вс Крей-1 ("Электроника ссбис")

- •Мвк "Эльбрус-2"

- •Проект мвк "Эльбрус-3"

- •Организация памяти вычислительной системы Организация подсистемы памяти в пк

- •Технологии оперативной памяти

- •Вопросы для самоконтроля

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Ввод-вывод информации

- •Состав, классификация и характеристики периферийных устройств Классификация периферийных устройств

- •Устройства ввода Клавиатура

- •Прочие устройства ввода - манипуляторы

- •Устройства вывода Монитор

- •Принтеры

- •Внешние запоминающие устройства Накопители с магнитным носителем

- •Накопители с оптическим носителем

- •Вопросы для самоконтроля

- •Микропроцессорная техника Понятие микропроцессора

- •1.1. Что такое микропроцессор?

- •1.2. Шинная структура связей

- •1.3. Режимы работы микропроцессорной системы

- •1.4. Архитектура микропроцессорных систем

- •1.5. Типы микропроцессорных систем

- •Мультимикропроцессорные вычислительные системы

- •Направление "мини-супер" призвано поддержать персональный компьютер

- •Распределенный и разделяемый вычислительный ресурс второго уровня. Решающие поля

- •Способы распараллеливания

- •2. Рассмотрим задачу счета способом "пирамиды".

- •Тенденции развития микропроцессоров

- •Нанотехнологии

- •Фотоника

- •Вопросы для самоконтроля

- •Пэвм,рабочие станции и серверы:

- •Vliw архитектура

- •Архитектура ia-64

- •Описание ia-64

- •Архитектура е2к

- •2.4.2. Функции памяти

- •2.4.3. Функции устройств ввода/вывода

- •Адресация операндов

- •3.1. Адресация операндов

- •3.1.1. Методы адресации

- •3.1.2. Сегментирование памяти

- •3.1.3. Адресация байтов и слов

- •3.2. Регистры процессора

- •Подключение дополнительных и интерфейсных схем Интерфейсы scsi

- •Интерфейс rs-232c

- •Интерфейс ieee 1284

- •Инфракрасный интерфейс

- •Интерфейс usb

- •Интерфейс ieee 1394 - FireWire

- •Вопросы для самоконтроля

- •Универсальные и специализированные эвм высокой производительности

- •Способы организации высокопроизводительных процессоров. Ассоциативные процессоры. Конвейерные процессоры. Матричные процессоры

- •Ассоциативные процессоры

- •Конвейерные процессоры

- •Матричные процессоры

- •Архитектура специализированных вычислительных комплексов Концепция Вычислительного Комплекса

- •Архитектура комплексов, ориентированных на программное обеспечение Основные характеристики мультипрограммного режима работы эвм

- •Расширенная архитектура приложений

- •Архитектура компьютера

- •С точки зрения программиста

- •Уровни абстракции

- •Создание программ

- •Классификация архитектур

- •Процессоро-ориентированная архитектура

- •Машинная архитектура высокого уровня

- •И это тоже есть!

- •Объекты

- •Имена объектов

- •Объекты os/400 и системные объекты mi

- •Поиск объектов

- •Библиотеки

- •Разделяемые папки

- •Интегрированная файловая система

- •Доступ к объектам

- •Адресация на базе возможностей

- •Разрешение системных указателей

- •Другие типы указателей

- •Характеристики системных объектов

- •Программные объекты

- •Внутри системного объекта

- •Сегментированная память

- •Структура системного объекта

- •Многосегментные объекты

- •Содержимое заголовков

- •Заголовок сегмента

- •Заголовок epa

- •Примеры объектов

- •Машины баз данных Интегрированная база данных

- •База данных без имени

- •Хранилища данных

- •Преобразование оперативных данных в информационные

- •Серверы баз данных

- •Параллельная обработка

- •Многомерные базы данных (mdd)

- •Анализ данных и инструментарий конечных пользователей

- •Управление хранилищем данных

- •Эволюция реляционной базы данных

- •Двуликая база данных

- •Как функционирует база данных

- •Функции субд

- •Описание данных и создание файлов

- •Создание физических файлов и таблиц

- •Создание логических файлов и проекций

- •Словарь данных и каталоги

- •Независимость данных и программ

- •Защита данных

- •Целостность и восстановление данных

- •Системная защита пути доступа smapp

- •Управление транзакциями

- •Триггеры

- •Ссылочная целостность

- •Дисковые системы высокой доступности

- •Другие функции базы данных

- •Хранимые процедуры

- •Поддержка национальных языков

- •Предсказывающий регулятор запросов

- •Повышение производительности базы данных

- •Распределенные базы данных

- •Шлюзы к другим базам данных

- •Трансформация данных с помощью DataPropagator

- •Соединение при помощи OptiConnect

- •Внутренняя реализация функций базы данных

- •Объекты базы данных

- •Области данных

- •Индексы области данных

- •Курсоры

- •Доступ пользователя к данным

- •Журналы slic

- •Управление транзакциями в slic

- •Машинные индексы

- •Двоичный поиск

- •Деревья с двоичным основанием

- •Внутренняя организация дерева с двоичным основанием

- •Защита от несанкционированного доступа

- •Интегрированная защита

- •Уровни защиты

- •Отсутствие защиты (уровень 10)

- •Парольная защита (уровень 20)

- •Защита ресурсов (уровень 30)

- •Защита ос (уровень 40)

- •Защита c2 (уровень 50)

- •Профили пользователей

- •Класс пользователя

- •Объекты, принадлежащие и доступные

- •Права доступа к объектам

- •Привилегированные команды и специальные права

- •Заимствование прав программой

- •Группирование прав

- •Алгоритм поиска прав

- •Дополнительная защита в сетевом мире

- •Подключение пк к as/400

- •Вирусы, черви, троянские кони и другие мерзкие твари

- •Безопасный сервер www

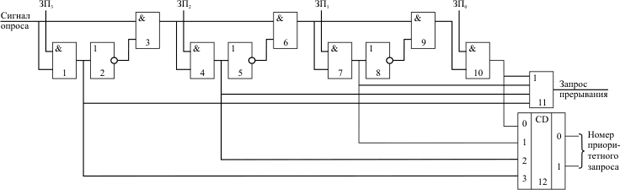

Цепочечная однотактная система определения приоритета запроса прерывания

На рис. 14.3 приведена схема, обеспечивающая получение номера наиболее приоритетного запроса прерывания из присутствующих в компьютере на момент подачи сигнала опроса ("дейзи-цепочка") [7]

Данная схема используется для анализа запросов аппаратных прерываний. Приоритет запросов прерываний (ЗПi) уменьшается с уменьшением номера запроса. В тот момент, когда компьютер должен определить наличие и приоритет внешнего аппаратного прерывания (обычно после окончания выполнения каждой команды), процессор выдает сигнал опроса. Если на входе ЗП3 присутствует сигнал высокого уровня (есть запрос), то на элементе 11 формируется общий сигнал наличия запроса прерывания и дальнейшее прохождение сигнала опроса блокируется. Если ЗП3=0, то анализируется сигнал ЗП2 и так далее. На шифраторе (элемент 12) формируется номер поступившего запроса прерывания.

Этот номер передается в процессор лишь при наличии общего сигнала запроса прерывания.

Такая структура позволяет быстро анализировать наличие сигнала запроса прерывания и определять наиболее приоритетный запрос из нескольких присутствующих в данный момент. Распределение приоритетов запросов прерываний внешних устройств осуществляется путем их физической коммутации по отношению к процессору. Указание приоритетов - жесткое и не может быть программно изменено. Изменение приоритетов возможно только путем физической перекоммутации устройств.

Рис. 14.3. Схема определения номера наиболее приоритетного запроса прерывания

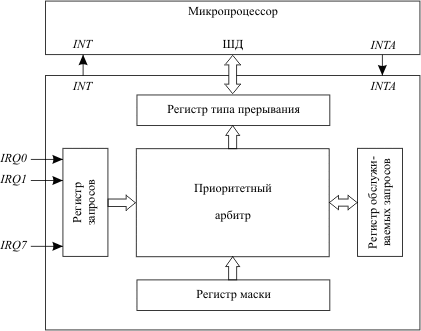

Обработка прерываний в персональной эвм

Микропроцессоры типа х86 имеют два входа запросов внешних аппаратных прерываний:

NMI - немаскируемое прерывание, используется обычно для запросов прерываний по нарушению питания;

INT - маскируемое прерывание, запрос от которого можно программным образом замаскировать путем сброса флага IF в регистре флагов.

Рис. 14.4. Структура контроллера приоритетных прерываний

Единственный вход запроса маскируемых прерываний микропроцессора не позволяет подключить к нему напрямую сигналы запросов от большого числа различных внешних устройств, которые входят в состав современного компьютера: таймера, клавиатуры, "мыши", принтера, сетевой карты и т.д. Для их подключения к одному входу INT микропроцессора используется контроллер приоритетных прерываний (рис. 14.4). Его функции:

восприятие и фиксация запросов прерываний от внешних устройств;

определение незамаскированных запросов среди поступивших запросов;

проведение арбитража: выделение наиболее приоритетного запроса из незамаскированных запросов в соответствии с установленным механизмом назначения приоритетов;

сравнение приоритета выделенного запроса с приоритетом запроса, который в данный момент может обрабатываться в микропроцессоре, формирование сигнала запроса на вход INT микропроцессора в случае, если приоритет нового запроса выше;

передача в микропроцессор по шине данных типа прерывания, выбранного в процессе арбитража, для запуска соответствующей программы - обработчика прерывания; это действие выполняется по сигналу разрешения прерывания INTA от микропроцессора, который выдается в случае, если прерывания в регистре флагов микропроцессора не замаскированы (IF=1).

Переход к соответствующему обработчику прерывания осуществляется (в реальном режиме работы микропроцессора) посредством таблицы векторов прерываний. Эта таблица (рис. 14.5) располагается в самых младших адресах оперативной памяти, имеет объем 1 Кбайт и содержит значения сегментного регистра команд (CS) и указателя команд (IP) для 256 обработчиков прерываний.

Рис. 14.5. Структура таблицы векторов прерываний

Обращение к элементам таблицы осуществляется по 8-разрядному коду - типу прерывания (табл. 14.1).

Таблица 14.1. |

|

Тип прерывания |

Источник прерывания |

0 |

Деление на 0 |

1 |

Пошаговый режим выполнения программы |

2 |

Запрос по входу NMI |

· · · |

|

8 |

Запрос по входу IRQ0 (системный таймер) |

9 |

Запрос по входу IRQ1 (контроллер клавиатуры) |

· · · |

|

11 |

Отсутствие сегмента в оперативной памяти |

· · · |

|

255 |

Пользовательское прерывание |

Различные источники задают тип прерывания по-разному:

программные прерывания вводят его изнутри процессора или содержат его в номере команды INT n;

аппаратные маскируемые прерывания вводят его от контроллера приоритетных прерываний по шине данных;

немаскируемому аппаратному прерыванию назначен тип 2.