- •Основы Информационно Вычислительных Комплексов

- •Оглавление

- •Арифметические основы

- •Система счисления.

- •Позиционные системы счисления.

- •Выбор системы счисления.

- •Перевод чисел из одной системы счисления в другую.

- •Перевод чисел из одной системы счисления в другую, когда одно основание является целой степенью другого.

- •Классификация параллельных вс

- •"Фон-Неймановские" и "не-Фон-Неймановские" архитектуры

- •Системы с общей и распределенной памятью

- •Способы межмодульного соединения (комплексирования)

- •"Исторические" модели Векторная вс пс-2000

- •Матричные вс

- •Вс Крей-1 ("Электроника ссбис")

- •Мвк "Эльбрус-2"

- •Проект мвк "Эльбрус-3"

- •Организация памяти вычислительной системы Организация подсистемы памяти в пк

- •Технологии оперативной памяти

- •Вопросы для самоконтроля

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Ввод-вывод информации

- •Состав, классификация и характеристики периферийных устройств Классификация периферийных устройств

- •Устройства ввода Клавиатура

- •Прочие устройства ввода - манипуляторы

- •Устройства вывода Монитор

- •Принтеры

- •Внешние запоминающие устройства Накопители с магнитным носителем

- •Накопители с оптическим носителем

- •Вопросы для самоконтроля

- •Микропроцессорная техника Понятие микропроцессора

- •1.1. Что такое микропроцессор?

- •1.2. Шинная структура связей

- •1.3. Режимы работы микропроцессорной системы

- •1.4. Архитектура микропроцессорных систем

- •1.5. Типы микропроцессорных систем

- •Мультимикропроцессорные вычислительные системы

- •Направление "мини-супер" призвано поддержать персональный компьютер

- •Распределенный и разделяемый вычислительный ресурс второго уровня. Решающие поля

- •Способы распараллеливания

- •2. Рассмотрим задачу счета способом "пирамиды".

- •Тенденции развития микропроцессоров

- •Нанотехнологии

- •Фотоника

- •Вопросы для самоконтроля

- •Пэвм,рабочие станции и серверы:

- •Vliw архитектура

- •Архитектура ia-64

- •Описание ia-64

- •Архитектура е2к

- •2.4.2. Функции памяти

- •2.4.3. Функции устройств ввода/вывода

- •Адресация операндов

- •3.1. Адресация операндов

- •3.1.1. Методы адресации

- •3.1.2. Сегментирование памяти

- •3.1.3. Адресация байтов и слов

- •3.2. Регистры процессора

- •Подключение дополнительных и интерфейсных схем Интерфейсы scsi

- •Интерфейс rs-232c

- •Интерфейс ieee 1284

- •Инфракрасный интерфейс

- •Интерфейс usb

- •Интерфейс ieee 1394 - FireWire

- •Вопросы для самоконтроля

- •Универсальные и специализированные эвм высокой производительности

- •Способы организации высокопроизводительных процессоров. Ассоциативные процессоры. Конвейерные процессоры. Матричные процессоры

- •Ассоциативные процессоры

- •Конвейерные процессоры

- •Матричные процессоры

- •Архитектура специализированных вычислительных комплексов Концепция Вычислительного Комплекса

- •Архитектура комплексов, ориентированных на программное обеспечение Основные характеристики мультипрограммного режима работы эвм

- •Расширенная архитектура приложений

- •Архитектура компьютера

- •С точки зрения программиста

- •Уровни абстракции

- •Создание программ

- •Классификация архитектур

- •Процессоро-ориентированная архитектура

- •Машинная архитектура высокого уровня

- •И это тоже есть!

- •Объекты

- •Имена объектов

- •Объекты os/400 и системные объекты mi

- •Поиск объектов

- •Библиотеки

- •Разделяемые папки

- •Интегрированная файловая система

- •Доступ к объектам

- •Адресация на базе возможностей

- •Разрешение системных указателей

- •Другие типы указателей

- •Характеристики системных объектов

- •Программные объекты

- •Внутри системного объекта

- •Сегментированная память

- •Структура системного объекта

- •Многосегментные объекты

- •Содержимое заголовков

- •Заголовок сегмента

- •Заголовок epa

- •Примеры объектов

- •Машины баз данных Интегрированная база данных

- •База данных без имени

- •Хранилища данных

- •Преобразование оперативных данных в информационные

- •Серверы баз данных

- •Параллельная обработка

- •Многомерные базы данных (mdd)

- •Анализ данных и инструментарий конечных пользователей

- •Управление хранилищем данных

- •Эволюция реляционной базы данных

- •Двуликая база данных

- •Как функционирует база данных

- •Функции субд

- •Описание данных и создание файлов

- •Создание физических файлов и таблиц

- •Создание логических файлов и проекций

- •Словарь данных и каталоги

- •Независимость данных и программ

- •Защита данных

- •Целостность и восстановление данных

- •Системная защита пути доступа smapp

- •Управление транзакциями

- •Триггеры

- •Ссылочная целостность

- •Дисковые системы высокой доступности

- •Другие функции базы данных

- •Хранимые процедуры

- •Поддержка национальных языков

- •Предсказывающий регулятор запросов

- •Повышение производительности базы данных

- •Распределенные базы данных

- •Шлюзы к другим базам данных

- •Трансформация данных с помощью DataPropagator

- •Соединение при помощи OptiConnect

- •Внутренняя реализация функций базы данных

- •Объекты базы данных

- •Области данных

- •Индексы области данных

- •Курсоры

- •Доступ пользователя к данным

- •Журналы slic

- •Управление транзакциями в slic

- •Машинные индексы

- •Двоичный поиск

- •Деревья с двоичным основанием

- •Внутренняя организация дерева с двоичным основанием

- •Защита от несанкционированного доступа

- •Интегрированная защита

- •Уровни защиты

- •Отсутствие защиты (уровень 10)

- •Парольная защита (уровень 20)

- •Защита ресурсов (уровень 30)

- •Защита ос (уровень 40)

- •Защита c2 (уровень 50)

- •Профили пользователей

- •Класс пользователя

- •Объекты, принадлежащие и доступные

- •Права доступа к объектам

- •Привилегированные команды и специальные права

- •Заимствование прав программой

- •Группирование прав

- •Алгоритм поиска прав

- •Дополнительная защита в сетевом мире

- •Подключение пк к as/400

- •Вирусы, черви, троянские кони и другие мерзкие твари

- •Безопасный сервер www

Технологии оперативной памяти

Современные технологии оперативной памяти (табл. 9.4) в основном используют два схемотехнических решения для повышения быстродействия DRAM:

включение в микросхемы динамической памяти некоторого количества статической памяти;

синхронная работа памяти и ЦП, т.е. использование внутренней конвейерной архитектуры и чередование адресов.

Таблица 9.4. Современные технологии оперативной памяти |

|

CDRAM (Cache DRAM) |

Добавление SRAM (8, 16 Кб) |

EDRAM (Enhanced DRAM ) |

|

SDRAM (Synchronous DRAM) |

3-х ступенчатый конвейер, 2 банка памяти с доступом типа "пинг-понг" |

RDRAM (Rambus DRAM) |

Функционирует по протоколу расщепления транзакций |

EDO (Extended Data Out) DRAM |

Добавлен набор регистров-защелок |

BEDO DRAM (Burst EDO DRAM) |

|

DDR400SDRAM |

Double Data Rate - данные передаются по переднему и заднему фронтам импульса |

FPM DRAM

Данная технология широко использовалась в системах на основе Intel-386 и Intel-486. С появлением МП Pentium была вытеснена EDO DRAM. Ее эффективность обусловлена конвейерной организацией МП. Контроллер памяти позволял выставлять на шину адрес только один раз при чтении пакета из 4 байт, при этом сигнал RAS# удерживается на низком уровне. Типичное время доступа при частоте системной шины 66 МГц - 60 нс (35 нс - внутри строки), что соответствует режиму 5-3-3-3 (5 циклов шины на чтение первого байта строки и по 3 цикла шины при чтении последующих байт).

EDO DRAM

По сравнению с FPM DRAM, в микросхемах памяти данной технологии для каждого банка добавлен регистр-защелка, в котором сохраняются выходные данные. Считывание из него производится внешними схемами вплоть до спада следующего импульса CAS#. Время доступа внутри страницы снижается до 25 нс, повышая производительность на 40%, что соответствует режиму чтения 5-2-2-2.

Установка регистра-защелки практически не увеличивает стоимость микросхемы, однако ее применение дает эффект, соизмеримый с установкой внешнего асинхронного кэша.

BEDO DRAM

Данная технология является развитием конвейерной архитектуры. В структуру памяти, кроме регистра-защелки, был внедрен счетчик адреса колонок для пакетного цикла, что позволяет выставлять адрес колонки только в его начале, а в последующих передачах лишь запрашивать очередные данные. В результате удлинения конвейера выходные данные как бы отстают на один сигнал CAS#, зато следующие появляются без тактов ожидания. При этом стартовый адрес следующего пакета пересылается вместе с последним CAS#-сигналом предыдущего. Если чипсет способен генерировать обращения к памяти в режиме смежных циклов, то можно достичь выигрыша в производительности, соответствующего режиму чтения 5-1-1-1.

SDRAM

Особенностью технологии SDRAM (Synchronous DRAM) является синхронная работа микросхем памяти и процессора. Тактовый генератор, задающий скорость работы микропроцессором, также управляет работой SDRAM. При этом уменьшаются временные задержки в процессе циклов ожидания, и ускоряется поиск данных. Эта синхронизация позволяет контроллеру памяти точно знать время готовности данных. Таким образом, скорость доступа увеличивается благодаря тому, что данные доступны во время каждого такта таймера. Технология SDRAM позволяет использовать множественные банки памяти, функционирующие одновременно, дополнительно к адресации целыми блоками. Микросхемы SDRAM имеют программируемые параметры и свои наборы команд. Длина пакетного цикла чтения-записи может программироваться (1, 2, 4, 8, 256 элементов). Цикл может быть прерван специальной командой без утери данных. Конвейерная организация позволяет инициировать следующий цикл чтения до окончания предыдущего.

SDRAM II (DDR)

Synchronous DRAM II, или DDR (Double Data Rate - удвоенная скорость передачи данных), является развитием SDRAM. Технология DDR основана на тех же принципах, что и SDRAM, однако включает некоторые усовершенствования, позволяющие увеличить быстродействие. DDR дает возможность читать данные по нарастающему и спадающему фронтам тактового сигнала, выполняя два доступа за время одного обращения стандартной SDRAM, что фактически увеличивает скорость доступа вдвое по сравнению с SDRAM, используя при этом ту же частоту. Кроме того, DDR использует DLL (Delay-Locked Loop - цикл с фиксированной задержкой) для выдачи сигнала DataStrobe, означающего доступность данных на выходных контактах. Используя один сигнал DataStrobe на каждые 16 выводов, контроллер может осуществлять доступ к данным более точно и синхронизировать входящие данные, которые поступают из разных модулей, находящихся в одном банке.

RDRAM

В основе технологии RDRAM лежит многофункциональный протокол обмена данными между микросхемами, который позволяет передачу данных по упрощенной шине, работающей на высокой частоте. RDRAM представляет собой интегрированную на системном уровне технологию. Ключевыми элементами RDRAM являются:

модули DRAM, базирующиеся на Rambus;

ячейки Rambus ASIC (RACs);

схема соединения чипов, называемая Rambus Channel.

Rambus, впервые использованный в графических рабочих станциях в 1995 году, использует уникальную технологию RSL (Rambus Signal Logic - сигнальная логика Rambus), позволяющую использовать частоты передачи данных до 600MHz на обычных системах и материнских платах. Rambus использует низковольтные сигналы и обеспечивает передачу данных по обоим фронтам сигнала системного таймера. RDRAM использует 8-битовый интерфейс, в то время как EDO RAM и SDRAM используют 4-, 8- и 16-битовый интерфейс. Технологии Rambus запатентованы, поэтому лицензионные отчисления делают производство микросхем памяти этой технологии достаточно дорогим.

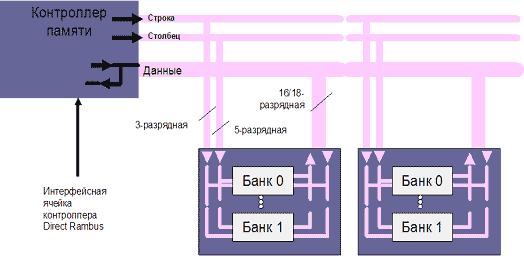

Расширением технологии RDRAM является Direct Rambus. Схемотехника Direct Rambus использует те же уровни сигналов (RSL), но более широкую шину (16 бит), более высокие частоты (выше 800MHz) и улучшенный протокол (эффективность выше на 90%). Однобанковый модуль RDRAM обеспечивает скорость передачи 1,6 Гбайт/с, двухбанковый - 3,2 Гбайт/с. Direct Rambus использует два 8-битных канала для передачи 1,6 Гбайт и 3 канала для получения 2,4 Гбайт (рис. 9.5).

увеличить изображение Рис. 9.5. Архитектура памяти Direct Rambus