- •Основы Информационно Вычислительных Комплексов

- •Оглавление

- •Арифметические основы

- •Система счисления.

- •Позиционные системы счисления.

- •Выбор системы счисления.

- •Перевод чисел из одной системы счисления в другую.

- •Перевод чисел из одной системы счисления в другую, когда одно основание является целой степенью другого.

- •Классификация параллельных вс

- •"Фон-Неймановские" и "не-Фон-Неймановские" архитектуры

- •Системы с общей и распределенной памятью

- •Способы межмодульного соединения (комплексирования)

- •"Исторические" модели Векторная вс пс-2000

- •Матричные вс

- •Вс Крей-1 ("Электроника ссбис")

- •Мвк "Эльбрус-2"

- •Проект мвк "Эльбрус-3"

- •Организация памяти вычислительной системы Организация подсистемы памяти в пк

- •Технологии оперативной памяти

- •Вопросы для самоконтроля

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Ввод-вывод информации

- •Состав, классификация и характеристики периферийных устройств Классификация периферийных устройств

- •Устройства ввода Клавиатура

- •Прочие устройства ввода - манипуляторы

- •Устройства вывода Монитор

- •Принтеры

- •Внешние запоминающие устройства Накопители с магнитным носителем

- •Накопители с оптическим носителем

- •Вопросы для самоконтроля

- •Микропроцессорная техника Понятие микропроцессора

- •1.1. Что такое микропроцессор?

- •1.2. Шинная структура связей

- •1.3. Режимы работы микропроцессорной системы

- •1.4. Архитектура микропроцессорных систем

- •1.5. Типы микропроцессорных систем

- •Мультимикропроцессорные вычислительные системы

- •Направление "мини-супер" призвано поддержать персональный компьютер

- •Распределенный и разделяемый вычислительный ресурс второго уровня. Решающие поля

- •Способы распараллеливания

- •2. Рассмотрим задачу счета способом "пирамиды".

- •Тенденции развития микропроцессоров

- •Нанотехнологии

- •Фотоника

- •Вопросы для самоконтроля

- •Пэвм,рабочие станции и серверы:

- •Vliw архитектура

- •Архитектура ia-64

- •Описание ia-64

- •Архитектура е2к

- •2.4.2. Функции памяти

- •2.4.3. Функции устройств ввода/вывода

- •Адресация операндов

- •3.1. Адресация операндов

- •3.1.1. Методы адресации

- •3.1.2. Сегментирование памяти

- •3.1.3. Адресация байтов и слов

- •3.2. Регистры процессора

- •Подключение дополнительных и интерфейсных схем Интерфейсы scsi

- •Интерфейс rs-232c

- •Интерфейс ieee 1284

- •Инфракрасный интерфейс

- •Интерфейс usb

- •Интерфейс ieee 1394 - FireWire

- •Вопросы для самоконтроля

- •Универсальные и специализированные эвм высокой производительности

- •Способы организации высокопроизводительных процессоров. Ассоциативные процессоры. Конвейерные процессоры. Матричные процессоры

- •Ассоциативные процессоры

- •Конвейерные процессоры

- •Матричные процессоры

- •Архитектура специализированных вычислительных комплексов Концепция Вычислительного Комплекса

- •Архитектура комплексов, ориентированных на программное обеспечение Основные характеристики мультипрограммного режима работы эвм

- •Расширенная архитектура приложений

- •Архитектура компьютера

- •С точки зрения программиста

- •Уровни абстракции

- •Создание программ

- •Классификация архитектур

- •Процессоро-ориентированная архитектура

- •Машинная архитектура высокого уровня

- •И это тоже есть!

- •Объекты

- •Имена объектов

- •Объекты os/400 и системные объекты mi

- •Поиск объектов

- •Библиотеки

- •Разделяемые папки

- •Интегрированная файловая система

- •Доступ к объектам

- •Адресация на базе возможностей

- •Разрешение системных указателей

- •Другие типы указателей

- •Характеристики системных объектов

- •Программные объекты

- •Внутри системного объекта

- •Сегментированная память

- •Структура системного объекта

- •Многосегментные объекты

- •Содержимое заголовков

- •Заголовок сегмента

- •Заголовок epa

- •Примеры объектов

- •Машины баз данных Интегрированная база данных

- •База данных без имени

- •Хранилища данных

- •Преобразование оперативных данных в информационные

- •Серверы баз данных

- •Параллельная обработка

- •Многомерные базы данных (mdd)

- •Анализ данных и инструментарий конечных пользователей

- •Управление хранилищем данных

- •Эволюция реляционной базы данных

- •Двуликая база данных

- •Как функционирует база данных

- •Функции субд

- •Описание данных и создание файлов

- •Создание физических файлов и таблиц

- •Создание логических файлов и проекций

- •Словарь данных и каталоги

- •Независимость данных и программ

- •Защита данных

- •Целостность и восстановление данных

- •Системная защита пути доступа smapp

- •Управление транзакциями

- •Триггеры

- •Ссылочная целостность

- •Дисковые системы высокой доступности

- •Другие функции базы данных

- •Хранимые процедуры

- •Поддержка национальных языков

- •Предсказывающий регулятор запросов

- •Повышение производительности базы данных

- •Распределенные базы данных

- •Шлюзы к другим базам данных

- •Трансформация данных с помощью DataPropagator

- •Соединение при помощи OptiConnect

- •Внутренняя реализация функций базы данных

- •Объекты базы данных

- •Области данных

- •Индексы области данных

- •Курсоры

- •Доступ пользователя к данным

- •Журналы slic

- •Управление транзакциями в slic

- •Машинные индексы

- •Двоичный поиск

- •Деревья с двоичным основанием

- •Внутренняя организация дерева с двоичным основанием

- •Защита от несанкционированного доступа

- •Интегрированная защита

- •Уровни защиты

- •Отсутствие защиты (уровень 10)

- •Парольная защита (уровень 20)

- •Защита ресурсов (уровень 30)

- •Защита ос (уровень 40)

- •Защита c2 (уровень 50)

- •Профили пользователей

- •Класс пользователя

- •Объекты, принадлежащие и доступные

- •Права доступа к объектам

- •Привилегированные команды и специальные права

- •Заимствование прав программой

- •Группирование прав

- •Алгоритм поиска прав

- •Дополнительная защита в сетевом мире

- •Подключение пк к as/400

- •Вирусы, черви, троянские кони и другие мерзкие твари

- •Безопасный сервер www

Проект мвк "Эльбрус-3"

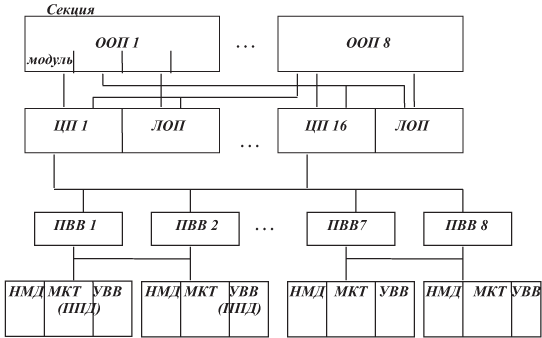

Так как ассемблерный язык исключен из интерфейса пользователя, то аппаратная реализация (она отражена в системе команд — в машинном языке) МВК "Эльбрус-3" значительно отличается от "Эльбрус-2". Структура МВК представлена на рис. 1.15.

Рис. 1.15. Общая схема МВК "Эльбрус-3"

Здесь ООП — общая оперативная память (8 секций (блоков) по 4 модуля; модуль — 32 Мбайт); МКТ — модульные комплексы телеобработки (аналог ППД — в "Эльбрус-2"); ЛОП — локальная оперативная память, 4 — 16 Мбайт.

Принципы, лежащие в основе разработки:

Программная совместимость на уровне ЯВУ (Эль-76 — ЯВУ-ассемблер) с другими моделями "Эльбрус".

Теговая архитектура.

Дальнейшее развитие многопроцессорности на общей ОП, что повышает производительность и структурную надежность. Пиковая производительность одного (из 16) процессора достигает 700 млн. оп/с при такте машины 10 нс.

Архитектура с длинным командным словом обеспечивает микрораспараллеливание между 7 ИУ АЛУ на уровне операций (2 ИУ сложения, 2 — умножения, одно — деления, 2 — логических), а также параллельное обращение по 8 каналам в ЛОП или ОП.

Семь конвейерных и независимых ИУ обеспечивают загрузку процессора работами в каждый такт.

Управление машиной позволяет контролировать каждый такт. Т.е. "длинная" команда выдается каждый такт, непосредственно запуская устройства без дополнительного динамического аппаратного планирования их загрузки.

Оптимизация распределения ресурсов возлагается на высокооптимизирующий транслятор с ЯВУ Эль-76 и с других языков высокого уровня.

Функционально разделенное СОЗУ снижает конфликты при обращении и отражает типы хранимых данных. Оно состоит из ассоциативного буфера команд в 2 тыс. слов, буфера стека в 1 тыс. слов для хранения верхних уровней локальных данных выполняемых процедур, буфера массивов в 512 слов и ассоциативной памяти глобалов (общих данных процедур) в 512 слов.

Организация памяти вычислительной системы Организация подсистемы памяти в пк

Запоминающие устройства (ЗУ) подсистемы памяти ПК можно выстроить в следующую иерархию (табл. 9.1):

Таблица 9.1. Иерархия подсистемы памяти ПК |

|||||||

№ |

Тип ЗУ |

1985 г. |

2000 г. |

||||

Время выборки |

Типичный объем |

Цена / байт |

Время выборки |

Типичный объем |

Цена / байт |

||

1 |

Сверхоперативные ЗУ (регистры) |

0,2 5 нс |

16/32 бит |

$ 3 - 100 |

0,01 1 нс |

32/64/128 бит |

$ 0,1 10 |

2 |

Быстродействующее буферное ЗУ (кэш) |

20 100 нс |

8Кб - 64Кб |

~ $ 10 |

0,5 - 2 нс |

32Кб 1Мб |

$ 0,1 - 0,5 |

3 |

Оперативное (основное) ЗУ |

~ 0,5 мс |

1Мб - 256Мб |

$ 0,02 1 |

2 нс 20 нс |

128Мб - 4Гб |

$ 0,01 0,1 |

4 |

Внешние ЗУ (массовая память) |

10 - 100 мс |

1Мб - 1Гб |

$ 0,002 - 0,04 |

5 - 20 мс |

1Гб - 0,5Тб |

$ 0,001 - 0,01 |

Регистры процессора составляют его контекст и хранят данные, используемые исполняющимися в конкретный момент командами процессора. Обращение к регистрам процессора происходит, как правило, по их мнемоническим обозначениям в командах процессора.

Кэш используется для согласования скорости работы ЦП и основной памяти. В вычислительных системах используют многоуровневый кэш: кэш I уровня (L1), кэш II уровня (L2) и т.д. В настольных системах обычно используется двухуровневый кэш, в серверных - трехуровневый. Кэш хранит команды или данные, которые с большой вероятностью в ближайшее время поступят процессору на обработку. Работа кэш-памяти прозрачна для программного обеспечения, поэтому кэш-память обычно программно недоступна.

Оперативная память хранит, как правило, функционально-законченные программные модули (ядро операционной системы, исполняющиеся программы и их библиотеки, драйверы используемых устройств и т.п.) и их данные, непосредственно участвующие в работе программ, а также используется для сохранения результатов вычислений или иной обработки данных перед пересылкой их во внешнее ЗУ, на устройство вывода данных или коммуникационные интерфейсы.

Каждой ячейке оперативной памяти присвоен уникальный адрес. Организационные методы распределения памяти предоставляют программистам возможность эффективного использования всей компьютерной системы. К таким методам относят сплошную ("плоскую") модель памяти и сегментированную модель памяти. При использовании сплошной модели (flat model) памяти программа оперирует единым непрерывным адресным пространством линейным адресным пространством, в котором ячейки памяти нумеруются последовательно и непрерывно от 0 до 2n-1, где n - разрядность ЦП по адресу. При использовании сегментированной модели (segmented model) для программы память представляется группой независимых адресных блоков, называемых сегментами. Для адресации байта памяти программа должна использовать логический адрес, состоящий из селектора сегмента и смещения. Селектор сегмента выбирает определенный сегмент, а смещение указывает на конкретную ячейку в адресном пространстве выбранного сегмента.

Организационные методы распределения памяти позволяют организовать вычислительную систему, в которой рабочее адресное пространство программы превышает размер фактически имеющейся в системе оперативной памяти, при этом недостаток оперативной памяти заполняется за счет внешней более медленной или более дешевой памяти (винчестер, флэш-память и т.п.) Такую концепцию называют виртуальной памятью. При этом линейное адресное пространство может быть отображено на пространство физических адресов либо непосредственно (линейный адрес есть физический адрес), либо при помощи механизма страничной трансляции. Во втором случае линейное адресное пространство делится на страницы одинакового размера, которые составляют виртуальную память. Страничная трансляция обеспечивает отображение требуемых страниц виртуальной памяти в физическое адресное пространство.

Кроме реализации системы виртуальной памяти внешние ЗУ используются для долговременного хранения программ и данных в виде файлов.

Кэш-память

Кэш-память представляет собой быстродействующее ЗУ, размещенное на одном кристалле с ЦП или внешнее по отношению к ЦП. Кэш служит высокоскоростным буфером между ЦП и относительно медленной основной памятью. Идея кэш-памяти основана на прогнозировании наиболее вероятных обращений ЦП к оперативной памяти. В основу такого подхода положен принцип временной и пространственной локальности программы.

Если ЦП обратился к какому-либо объекту оперативной памяти, с высокой долей вероятности ЦП вскоре снова обратится к этому объекту. Примером этой ситуации может быть код или данные в циклах. Эта концепция описывается принципом временной локальности, в соответствии с которым часто используемые объекты оперативной памяти должны быть "ближе" к ЦП (в кэше).

Для согласования содержимого кэш-памяти и оперативной памяти используют три метода записи:

Сквозная запись (write through) - одновременно с кэш-памятью обновляется оперативная память.

Буферизованная сквозная запись (buffered write through) - информация задерживается в кэш-буфере перед записью в оперативную память и переписывается в оперативную память в те циклы, когда ЦП к ней не обращается.

Обратная запись (write back) - используется бит изменения в поле тега, и строка переписывается в оперативную память только в том случае, если бит изменения равен 1.

Как правило, все методы записи, кроме сквозной, позволяют для увеличения производительности откладывать и группировать операции записи в оперативную память.

В структуре кэш-памяти выделяют два типа блоков данных:

память отображения данных (собственно сами данные, дублированные из оперативной памяти);

память тегов (признаки, указывающие на расположение кэшированных данных в оперативной памяти).

Пространство памяти отображения данных в кэше разбивается на строки - блоки фиксированной длины (например, 32, 64 или 128 байт). Каждая строка кэша может содержать непрерывный выровненный блок байт из оперативной памяти. Какой именно блок оперативной памяти отображен на данную строку кэша, определяется тегом строки и алгоритмом отображения. По алгоритмам отображения оперативной памяти в кэш выделяют три типа кэш-памяти:

полностью ассоциативный кэш;

кэш прямого отображения;

множественный ассоциативный кэш.

Для полностью ассоциативного кэша характерно, что кэш-контроллер может поместить любой блок оперативной памяти в любую строку кэш-памяти (рис. 9.1). В этом случае физический адрес разбивается на две части: смещение в блоке (строке кэша) и номер блока. При помещении блока в кэш номер блока сохраняется в теге соответствующей строки. Когда ЦП обращается к кэшу за необходимым блоком, кэш-промах будет обнаружен только после сравнения тегов всех строк с номером блока.

Одно из основных достоинств данного способа отображения - хорошая утилизация оперативной памяти, т.к. нет ограничений на то, какой блок может быть отображен на ту или иную строку кэш-памяти. К недостаткам следует отнести сложную аппаратную реализацию этого способа, требующую большого количества схемотехники (в основном компараторов), что приводит к увеличению времени доступа к такому кэшу и увеличению его стоимости.

увеличить изображение Рис. 9.1. Полностью ассоциативный кэш 8х8 для 10-битного адреса

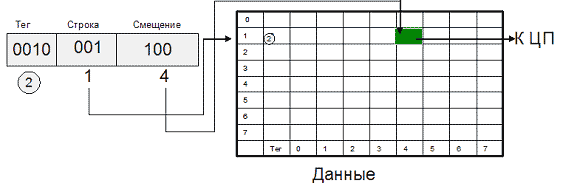

Альтернативный способ отображения оперативной памяти в кэш - это кэш прямого отображения (или одновходовый ассоциативный кэш). В этом случае адрес памяти (номер блока) однозначно определяет строку кэша, в которую будет помещен данный блок. Физический адрес разбивается на три части: смещение в блоке (строке кэша), номер строки кэша и тег. Тот или иной блок будет всегда помещаться в строго определенную строку кэша, при необходимости заменяя собой хранящийся там другой блок. Когда ЦП обращается к кэшу за необходимым блоком, для определения удачного обращения или кэш-промаха достаточно проверить тег лишь одной строки.

Очевидными преимуществами данного алгоритма являются простота и дешевизна реализации. К недостаткам следует отнести низкую эффективность такого кэша из-за вероятных частых перезагрузок строк. Например, при обращении к каждой 64-й ячейке памяти в системе на рис. 9.2 кэш-контроллер будет вынужден постоянно перегружать одну и ту же строку кэш-памяти, совершенно не задействовав остальные.

увеличить изображение Рис. 9.2. Кэш прямого отображения 8х8 для 10-битного адреса

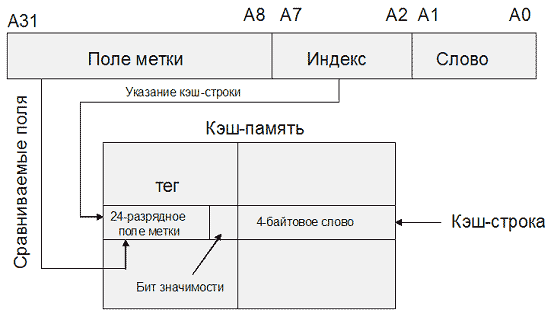

Несмотря на очевидные недостатки, данная технология нашла успешное применение, например, в МП Motorola MC68020, для организации кэша инструкций первого уровня (рис. 9.3). В данном микропроцессоре реализован кэш прямого отображения из 64 строк по 4 байт. Тег строки, кроме 24 бит, задающих адрес кэшированного блока, содержит бит значимости, определяющий действительность строки (если бит значимости 0, данная строка считается недействительной и не вызовет кэш-попадания). Обращения к данным не кэшируются.

увеличить изображение Рис. 9.3. Схема организации кэш-памяти в МП Motorola MC68020

Компромиссным вариантом между первыми двумя алгоритмами является множественный ассоциативный кэш или частично-ассоциативный кэш (рис. 9.4). При этом способе организации кэш-памяти строки объединяются в группы, в которые могут входить 2, 4, : строк. В соответствии с количеством строк в таких группах различают 2-входовый, 4-входовый и т.п. ассоциативный кэш. При обращении к памяти физический адрес разбивается на три части: смещение в блоке (строке кэша), номер группы (набора) и тег. Блок памяти, адрес которого соответствует определенной группе, может быть размещен в любой строке этой группы, и в теге строки размещается соответствующее значение. Очевидно, что в рамках выбранной группы соблюдается принцип ассоциативности. С другой стороны, тот или иной блок может попасть только в строго определенную группу, что перекликается с принципом организации кэша прямого отображения. Для того чтобы процессор смог идентифицировать кэш-промах, ему надо будет проверить теги лишь одной группы (2/4/8/: строк).

увеличить изображение Рис. 9.4. Двухвходовый ассоциативный кэш 8х8 для 10-битного адреса

Данный алгоритм отображения сочетает достоинства как полностью ассоциативного кэша (хорошая утилизация памяти, высокая скорость), так и кэша прямого доступа (простота и дешевизна), лишь незначительно уступая по этим характеристикам исходным алгоритмам. Именно поэтому множественный ассоциативный кэш наиболее широко распространен (табл. 9.2).

Таблица 9.2. Характеристики подсистемы кэш-памяти у ЦП IA-32 |

|||||

|

Intel486 |

Pentium |

Pentium MMX |

P6 |

Pentium 4 |

L1 кэш команд |

|||||

Тип |

4-вх. ассоц. |

2-вх. ассоц. |

4-вх. ассоц. |

4-вх. ассоц. |

8-вх. ассоц. |

Размер строки, байт |

16 |

32 |

32 |

32 |

- |

Общий объем, Кбайт |

8/16 |

8 |

16 |

8/16 |

12Кmops |

L1 кэш данных |

|||||

Тип |

Общий с кэш инструкций |

2-вх. ассоц. |

4-вх. ассоц. |

2/4-вх. ассоц. |

4-вх. ассоц. |

Размер строки, байт |

32 |

32 |

32 |

64 |

|

Общий объем, Кбайт |

8 |

16 |

8/16 |

8 |

|

L2 кэш |

|||||

Тип |

Внешний |

внешний 4-вх. ассоц. |

4-вх. ассоц. |

8-вх. ассоц. |

|

Размер строки, байт |

32 |

32 |

64 |

||

Общий объем, Кбайт |

256/512 |

128-2048 |

256/512 |

||

Примечания: В Intel-486 используется единый кэш команд и данных первого уровня. В Pentium Pro L1 кэш данных - 8 Кбайт 2-входовый ассоциативный, в остальных моделях P6 - 16 Кбайт 4-входовый ассоциативный. В Pentium 4 вместо L1 кэша команд используется L1 кэш микроопераций (кэш трассы).

Для организации кэш-памяти можно использовать принстонскую архитектуру (смешанный кэш для команд и данных, например, в Intel-486). Это очевидное (и неизбежное для фон-неймановских систем с внешней по отношению к ЦП кэш-памятью) решение не всегда бывает самым эффективным. Разделение кэш-памяти на кэш команд и кэш данных (кэш гарвардской архитектуры) позволяет повысить эффективность работы кэша по следующим соображениям:

Многие современные процессоры имеют конвейерную архитектуру, при которой блоки конвейера работают параллельно. Таким образом, выборка команды и доступ к данным команды осуществляется на разных этапах конвейера, а использование раздельной кэш-памяти позволяет выполнять эти операции параллельно.

Кэш команд может быть реализован только для чтения, следовательно, не требует реализации никаких алгоритмов обратной записи, что делает этот кэш проще, дешевле и быстрее.

Именно поэтому все последние модели IA-32, начиная с Pentium, для организации кэш-памяти первого уровня используют гарвардскую архитектуру.

Критерием эффективной работы кэша можно считать уменьшение среднего времени доступа к памяти по сравнению с системой без кэш-памяти. В таком случае среднее время доступа можно оценить следующим образом:

Tср = (Thit x Rhit) + (Tmiss x (1 Rhit))

где Thit - время доступа к кэш-памяти в случае попадания (включает время на идентификацию промаха или попадания), Tmiss - время, необходимое на загрузку блока из основной памяти в строку кэша в случае кэш-промаха и последующую доставку запрошенных данных в процессор, Rhit - частота попаданий.

Очевидно, что чем ближе значение Rhit к 1, тем ближе значение Tср к Thit. Частота попаданий определяется в основном архитектурой кэш-памяти и ее объемом. Влияние наличия и отсутствия кэш-памяти и ее объема на рост производительности ЦП показано в табл. 9.3.

Таблица 9.3. Размер и эффективность кэш-памяти |

||

Размер кэш-памяти |

Частота попаданий, % |

Рост производительности, % |

Нет кэш-памяти, DRAM с 2 TW |

- |

0 |

16 Кб |

81 |

35 |

32 Кб |

86 |

38 |

64 Кб |

88 |

39 |

128 Кб |

89 |

39 |

Нет кэш-памяти, SRAM без TW |

- |

47 |