- •1.Способи адресації

- •3.Пряма адресація пам'яті. .

- •6. Сторінкова пам'ять.

- •7.Сегмента адресація.

- •8. Опосередкована адресація з масштабуванням

- •9.Адресація по базі з сувом.

- •10.Адресація по базі з індексуванням

- •11. Адресація по базі з індексуванням та масштабуванням

- •12.Вирівнювання даних та коду.

- •13. Регістри загального призначення

- •14. Сегментні регістри.

- •15.Індексні регістри.

- •16. Спеціальні регістри

- •17. Флаги ознак.

- •18. Регистры управления (Control Registers)

- •19.20. Стек, регітсри стека.

- •22. Флаг нуля zf

- •23. Флаг знака sf

- •25. Флаг четности.

- •26. Флаг полупереносу.

- •27. Флаг трассировки.

- •28. Флаг напрямку.

- •29. Флаг переривание.

- •35. Арифметические команды

- •36. Команди блочної обробки даних

- •37. Команды ввода и вывода

- •38. Команды управления флагами

- •39. Команда пересылки данных: возможности и ограничения

- •40. Команди керування

- •41. Стек математичного співпроцесора

- •42.Команди пересилки співпроцесора

- •43. Арифметические команды сопроцессора

- •46. Різновиди чисел

- •47. Способи округлення

- •48.Трансцендентні команди

- •49. Команди завантаження констант співпроцесора

- •50. Порівняння чисел з плаваючою комою

- •51. Структура жёсткого диска

- •58. Структура каталогов Linux

- •59. Структура ufs

- •60. Суперблок. Ufs

- •61. Индексный дескриптор ufs

- •62. Основні механізми передачі параметрів

- •63. Основні місця передачі параметрів

- •64. Вкладені обчислення

- •65. Різновиди комбінацій сегментів

- •66. Порядок завантаження сегментів, директиви

- •67. Оптимізація обчислень

- •68. Математична оптимізація

- •69. Алгоритмічна оптимізація

- •70 .Низькорівнева оптимізація

- •71. Основні методи алгоритмічної оптимізації

- •72. Основні рекомендації низького рівня

- •74. Особенности архитектуры процессоров Pentium Pro и Pentium II

- •76. Конвеєр fpu

- •77. Принципи роботи кешу

- •79. Регистры управления (Control Registers)

- •80. Індексні регістри дескрипторів

- •81. Віртуалізація пам’яті

- •82. Переривання, маскування та обробка.

- •84. Кеш з зворотнім записом

- •85. Кеш з відкладеним записом

- •86. Наскрізний кеш

- •87. Кеш читання

- •88. Повністю асоціативний кеш

- •91. Структура кешу

- •92. Теги, призначення

- •93. Конвеєри mmx та sse

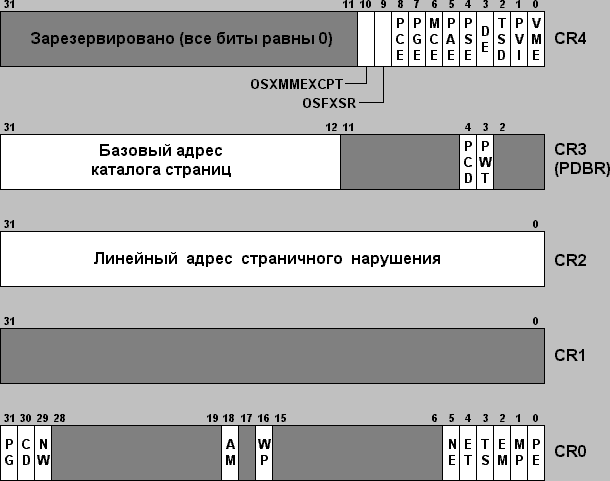

18. Регистры управления (Control Registers)

Регистры управления CR0, CR1, CR2, CR3 и CR4 определяют поведение процессора и характеристики текущей задачи. Для быстрого перехода к описанию флагов используйте их обозначения на рисунке.

|

CR0 - содержит системные флаги управления, управляющие поведением и состоянием процессора. |

|

CR1 - зарезервирован. |

|

CR2 - содержит линейный адрес команды, вызвавшей страничное нарушение. |

|

CR3 - содержит физический адрес начала каталога страниц и два флага: PCD и PWT. Этот регистр также называется PDBR (Page-Directory Base Register), он хранит 20 старших бит адреса каталога страниц (младшие подразумеваются равными 0, т.к. каталог страниц должен быть выровнен на границу страницы). Биты PCD и PWT управляют кэшированием каталога страниц во внутреннем кэше данных процессора, но не управляют TLB-кэшированием. При использовании расширения физического адреса, регистр CR3 содержит базовый адрес таблицы PDP (Page Directory Pointer). |

|

CR4 - содержит набор флагов, разрешающих использование некоторых архитектурных расширений. |

Регистры управления можно прочитать или загрузить только с помощью команды MOV. В защищёном режиме работа с регистрами управления позволена только программам с нулевым уровнем привилегий.

При загрузке значения в регистр управления, зарезервированные биты должны всегда иметь те значения, которые были получены при чтении.

Флаги регистров управления имеют следующие функции:

PG |

Трансляция страниц (Paging), 31-й бит в CR0. Разрешает страничное преобразование, если установлен, иначе - запрещает. Когда страничное преобразование разрешено, все линейные адреса используются как физические. Флаг PG не действует, если не установлен флаг PE (0-й бит в CR0), тем не менее, установка флага PG при сброшенном PE вызывает генерацию исключения общей защиты (#GP). Подробно механизм страничного преобразования обсуждается в разделе "Управление памятью". |

||||||||

CD |

Отключение кэша (Cache Disable), 30-й бит в CR0. Когда флаги CD и NW сброшены, разрешено кэширование всей памяти во внутренних и внеших кэшах. Когда флаг CD установлен, кэширование ограничено (см. таблицу). Чтобы запретить процессору доступ к его кэшам, флаг CD должен быть установлен и кэши объявлены недостоверными. Дополнительно об этом см. раздел "Управление кэшами". |

||||||||

NW |

Отмена сквозной записи (Not Write-through), 29-й бит в CR0. Когда флаги NW и CD сброшены, обратная запись (write-back) для Pentium 4, P6 family и Pentium или сквозная запись (write-through) для Intel486 разрешена для записей, не попавших в кэш (см. таблицу о действиях флагов NW и CD). |

||||||||

AM |

Проверка выравнивания (Alignment Mask), 18-й бит в CR0. Когда установлен, разрешает автоматическую проверку выравнивания, иначе - запрещает. Проверка выравнивания выполняется только при следующих условиях:

|

||||||||

WP |

Защита от записи (Write Protect), 16-й бит CR0. Когда установлен, запрещает системным процедурам запись в пользовательские страницы с доступом только для чтения (когда флаг WP сброшен - разрешает). |

||||||||

NE |

Численная ошибка (Numeric Error), 5-й бит в CR0. Когда установлен, активизирует внутрипроцессорный механизм сообщений об ошибках x87 FPU, когда сброшен - механизм сообщений об ошибках x87 FPU PC-типа. При сброшенном флаге NE, немаскируемая ошибка x87 FPU приводит к генерации прерывания сразу же после следующей команды x87 FPU или команд WAIT/FWAIT. |

||||||||

ET |

Тип расширения (Extension Type), 4-й бит в CR0. Зарезервирован в процессорах Pentium 4, семейства P6 и Pentium и для них всегда установлен. В процессорах Intel386 и Intel486 этот флаг, если установлен, определяет наличие поддержки команд процессора Intel 387 DX (математического сопроцессора). |

||||||||

TS |

Переключение задач (Task Switched), 3-й бит в CR0. Устанавливается процессором каждый раз при переключении задач; сбрасывается только программно. Процессор проверяет, установлен ли этот флаг, при выполнении команд модулей x87 FPU, MMX, SSE и SSE2. Использование этого флага позволяет не менять текущий контекст модулей x87 FPU, MMX, SSE и SSE2, пока к ним не произойдёт обращение.

|