- •1. Общие сведения об электронных ключах

- •2. Схемы электронных ключей на полевых транзисторах

- •4. Применение электронных ключей

- •3. Транзисторно-транзисторные лэ ( ттл ).

- •80286 - Однокристальный 16-разрядный мп;

- •3.3.4. Команды переходов

- •50. Программируемое устройство последовательного ввода/вывода информации (усапп)

3. Транзисторно-транзисторные лэ ( ттл ).

О снова

- многоэлементный транзистор (аналогично

диодной сборке в ДТЛ).

снова

- многоэлементный транзистор (аналогично

диодной сборке в ДТЛ).

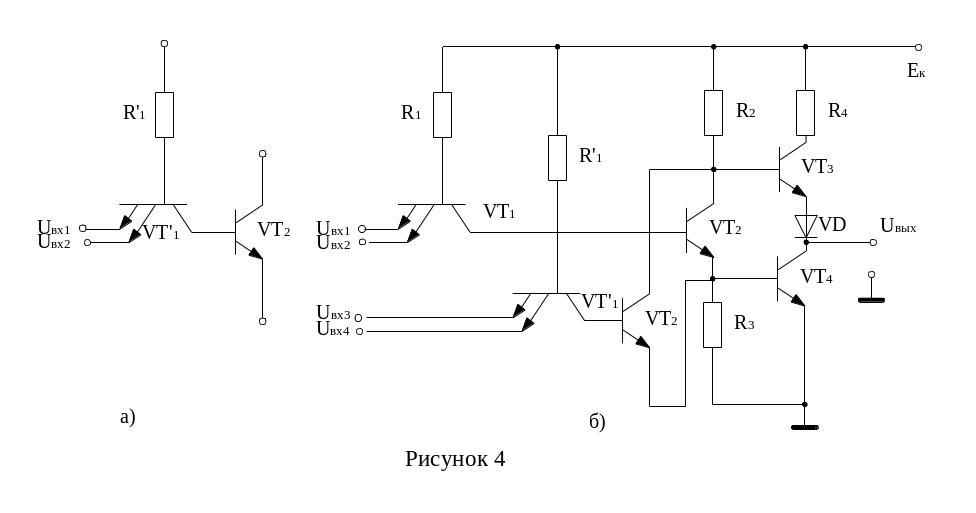

Рис. 4. Базовый элемент ТТЛ

Когда на всех входах Uвх = U1вх, все эмиттерные переходы закрыты и транзистор VT1 включен инверсно.

Его ток Iк проходит через базу VT2 и открывает его; Uвых становится равным U0вых.

Если хотя бы один эмиттер открыт (Uвх = U0вх), ток через R1 идет в эмиттер. VT2 закрывается и Uвых = U1вых.

Выполняется логическая функция И-НЕ.

Для снижения входных токов уменьшают коэффициент усиления тока VT1 в инверсном режиме включения b1 до 0,005 ... 0,05, удаляя контакт базы от эмиттерных областей (в структуре транзистора).

Достоинства ТТЛ :

- занимают мало места;

- высокое быстродействие.

Простейший базовый элемент ТТЛ, в соответствии с рисунком 2а, за счет использования многоэмиттерного транзистора, объединяющего свойства диода и транзисторного усилителя, позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы.

Б азовый

элемент ТТЛ также выполняет логическую

операцию И-НЕ. При низком уровне сигнала

(логический 0) хотя бы на одном из выходов

многоэмиттерного транзистора VT1

последний находится в состоянии

насыщения, а VT2

закрыт. На выходе схемы существует

высокий уровень напряжения (логическая

единица). При высоком уровне сигнала на

всех входах VT1

работает в активном инверсном режиме,

а VT2 находится в

состоянии насыщения. Описанный здесь

базовые элемент ТТЛ, несмотря на прощеную

технологию изготовления, не нашел

широкого применения из-за низкой

помехоустойчивости, малой нагрузочной

способностью и малого быстродействия

при работе на емкостную нагрузку. Его

целесообразно использовать лишь при

разработке микросхем с открытым

коллектором, в соответствии с рисунком

2б, для включения внешних элементов

индикации, когда не требуется высокая

помехоустойчивость и большая нагрузочная

способность.

азовый

элемент ТТЛ также выполняет логическую

операцию И-НЕ. При низком уровне сигнала

(логический 0) хотя бы на одном из выходов

многоэмиттерного транзистора VT1

последний находится в состоянии

насыщения, а VT2

закрыт. На выходе схемы существует

высокий уровень напряжения (логическая

единица). При высоком уровне сигнала на

всех входах VT1

работает в активном инверсном режиме,

а VT2 находится в

состоянии насыщения. Описанный здесь

базовые элемент ТТЛ, несмотря на прощеную

технологию изготовления, не нашел

широкого применения из-за низкой

помехоустойчивости, малой нагрузочной

способностью и малого быстродействия

при работе на емкостную нагрузку. Его

целесообразно использовать лишь при

разработке микросхем с открытым

коллектором, в соответствии с рисунком

2б, для включения внешних элементов

индикации, когда не требуется высокая

помехоустойчивость и большая нагрузочная

способность.

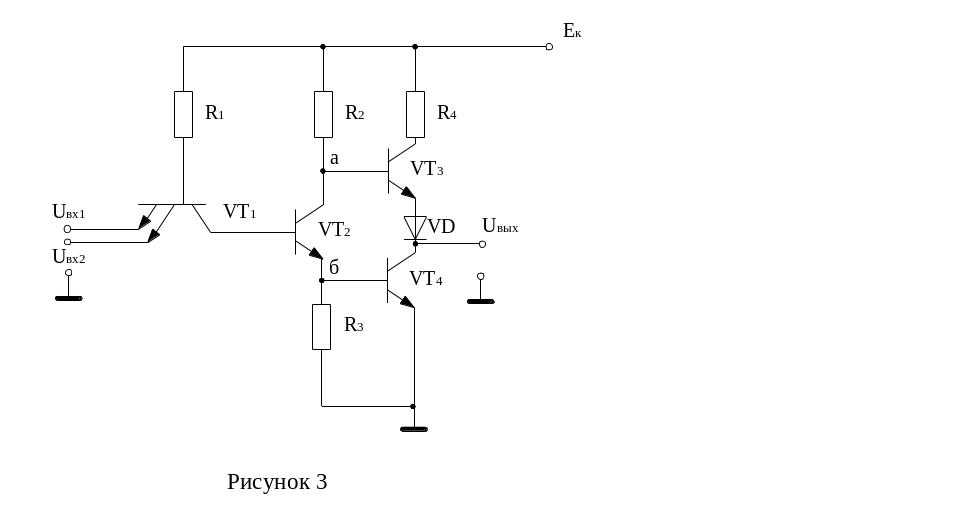

Улучшенными параметрами по сравнения с предыдущей схемой обладает базовый элемент ТТЛ, в соответствии с рисунком 3. Однако объединение выходов в схеме не допустимо.

В ТТЛ-схеме со сложным инвертором постоянная заряда нагрузочной емкости существенно уменьшается, так как емкость Сн заряжается через выходное сопротивление Rвых 3 << R2 транзистора VT3, работающего в схеме эмиттерного повторителя. За счет этого ТТЛ-схема со сложным инвертором имеет большее быстродействие по сравнению с ТТЛ-схемой, в соответствии с рисунком 2а.

Схема базового элемента со сложным инвертором лежит в основе разработок большинства серий интегральных микросхем ТТЛ. Для расширения функциональных возможностей элемента промышленностью выпускают так называемые расширители по ИЛИ, в соответствии с рисунком 4а, которые представляют собой часть структуры ТТЛ и подключаются к точкам а и б элемента, в соответствии с рисунком 2. Полученная при этом логическая схема, в соответствии с рисунком 4б, реализует функцию И-ИЛИ-НЕ. На выходе схемы устанавливается логический нуль, если на всех выходах VT1 поступают сигналы, соответствующие логической единице. При всех остальных комбинациях сигналов на выходах схемы выходное напряжение соответствует логической единице.

Повысить быстродействие ТТЛ-схем можно, применив в схеме базового элемента, в соответствии с рисунком 3, вместо обычных транзисторов транзисторы Шотки, работающие в активном режиме. Тем самым сокращается время переключения транзисторов схемы за счет исключения времени рассасывания носителей заряда в базе транзистора при их запирании. Логические ИМС, выполненные на базе транзисторов Шотки, называются микросхемами ТТЛШ.

18 |

Импульсные устройства. (СУММАТОР ПО МОДУЛЮ 2). |

Многоразрядный сумматор по модулю 2 – функциональный узел , предназначенный для определения суммы по модулю 2 количества единиц в многоразрялном коде. Например , имеем двоичный код

А = 1 0 1 1 0 0 1 1 ;

Сумма по модулю 2 этого числа

Smod2 = M2 ( A) = 1

Многоразрядные сумматоры по модулю 2 используются в цифровых устройствах в системах контроля правильности выполнения операций передачи, хранения и приема информации, а также и вычислительных операций.

Пусть имеется некоторый многоразрядный двоичный код :

X = { X1 X2 X3… XN } , тогда сумма по модулю 2

M2 (X) = X1 Е X2 Е X3 Е…Е XN

Способы получения М2(Х) последовательного и параллельного многоразрядных кодов различны.

Для последовательного многоразрядного кода М2(Х) получается с помощью триггера со счетным входом.

Получение суммы по модулю 2 для многоразрядного параллельного кода осуществляется с помощью комбинационных схем. Существует две основные комбинационные схемы многоразрядных сумматоров по модулю 2: последовательная и пирамидальная. Принцип построения обеих схем удобно пояснить посредством расставления скобок в выражении. Сумматор по модулю 2 последовательного действия строится в соответствии с логическим выражением:

M2 (X) = (…( ( ( X1 Е X2 ) Е X3 ) Е X4 ) … Е XN )

В схеме используется (N-1) одноразрядных сумматоров по модулю 2 . Если через t1 обозначить задержку одноразрядного сумматора по модулю 2 , то время срабатывания для этой схемы

ТМ2 посл = t1 (N-1)

Многоразрядный сумматор по модулю 2 пирамидального типа строится в соответствии с логическим выражением

М2 (Х) = ( ( Х1 Е Х2 ) Е ( Х3 Е Х4 ) ) Е ( ( Х5 Е Х6 ) Е …

Время срабатывания для пирамидального сумматора по модулю 2:

TM2пир = t1 Ч lg2N

Пирамидальная схема многоразрядного сумматора по модулю 2 обладает более высоким быстродействием и применяется чаще. В настоящее время выпускаются специальные интегральные микросхемы , реализующие операции суммирования по мод 2 многоразрядного кода.

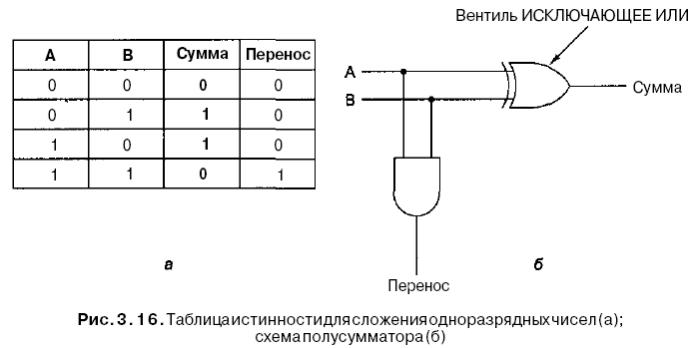

Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. На рисунке 1 приведена таблица истинности этого сумматора. Ее можно получить исходя из правил суммирования в двоичной арифметике. Предполагается, что читатель знаком с основами двоичной арифметики. Более подробно операции над двоичными числами будут рассмотрены позднее.

Рисунок

1. Таблица истинности сумматора по модулю

2.

Рисунок

1. Таблица истинности сумматора по модулю

2.

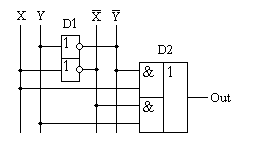

В соответствии с принципами построения произвольной таблицы истинности, рассмотренными в предыдущей главе, получим схему сумматора по модулю 2. Эта схема приведена на рисунке 2.

Р исунок

2. Принципиальная схема, реализующая

таблицу истинности сумматора по модулю

2.

исунок

2. Принципиальная схема, реализующая

таблицу истинности сумматора по модулю

2.

Сумматор по модулю 2 (для двоичной арифметики его схема совпадает со схемой исключающего "ИЛИ") изображается на схемах как показано на рисунке 3.

Р исунок

3. Изображение схемы, выполняющей

логическую функцию исключающего "ИЛИ".

исунок

3. Изображение схемы, выполняющей

логическую функцию исключающего "ИЛИ".

Сумматор по модулю 2 выполняет суммирование без учета переноса. В полном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена на рисунке 4.

19 |

Импульсные устройства. (ПОЛУСУММАТОР). |

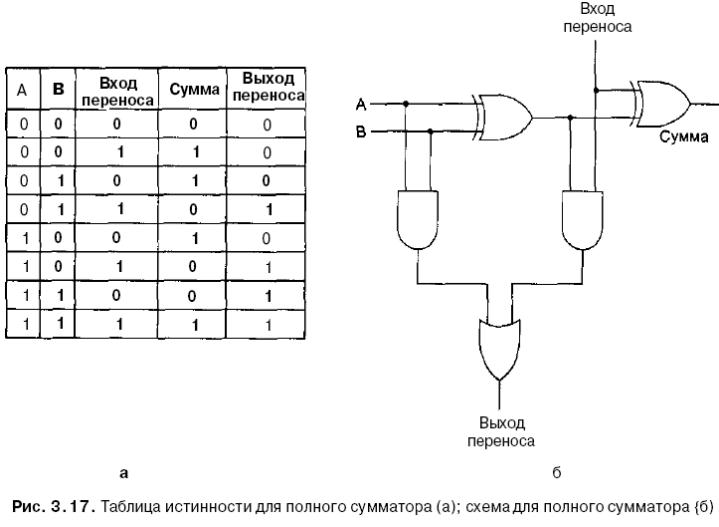

Компьютер, который не умеет складывать целые числа, практически немыслим. Следовательно, схема для выполнения операций сложения является существенной частью любого процессора. Таблица истинности для сложения одноразрядных целых чисел показана на рис. 3.16, а. Здесь имеется два результата: сумма входных переменных А и В и перенос на следующую (левую) позицию. Схема для вычисления бита суммы и бита переноса показана на рис. 3.16,б. Такая схема обычно называется полусумматором.

20 |

Импульсные устройства. (ПОЛНЫЙ СУММАТОР). |

П олусумматор

подходит для сложения битов нижних

разрядов двух многобитовых слов. Но он

не годится для сложения битов в середине

слова, потому что не может осуществлять

перенос в эту позицию. Поэтому необходим

полный сумматор (рис. 3.17). Из схемы должно

быть ясно, что полный сумматор состоит

из двух

олусумматор

подходит для сложения битов нижних

разрядов двух многобитовых слов. Но он

не годится для сложения битов в середине

слова, потому что не может осуществлять

перенос в эту позицию. Поэтому необходим

полный сумматор (рис. 3.17). Из схемы должно

быть ясно, что полный сумматор состоит

из двух

полусумматоров. Сумма равна 1, если нечетное число переменных А, В и Вход переноса принимает значение 1 (то есть если единице равна или одна из переменных, или все три). Выход переноса принимает значение 1, если или А и В одновременно равны 1 (левый вход в вентиль ИЛИ), или если один из них равен 1, а Вход переноса также равен 1. Два полусумматора порождают и биты суммы, и биты переноса.

21 |

Импульсные устройства. (МНОГОРАЗРЯДНЫЙ СУММАТОР). |

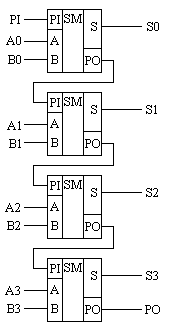

Для того чтобы получить многоразрядный сумматор, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Схема соединения одноразрядных сумматоров для реализации четырехразрядного сумматора приведена на рисунке 10.

Рисунок 10. Принципиальная схема многоразрядного двоичного сумматора.

Одноразрядные сумматоры практически никогда не использовались, так как почти сразу же были выпущены микросхемы многоразрядных сумматоров. Полный двоичный четырехразрядный сумматор изображается на схемах как показано на рисунке 11.

Рисунок 11. Изображение полного двоичного многоразрядного сумматора на схемах.

Е стественно,

в приведенной на рисунке 10 схеме

рассматриваются только принципы работы

двоичных сумматоров. В реальных схемах

никогда не допускают последовательного

распространения переноса через все

разряды многоразрядного сумматора. Для

увеличения скорости работы двоичного

сумматора применяется отдельная схема

формирования переносов для каждого

двоичного разряда. Таблицу истинности

для такой схемы легко получить из

алгоритма суммирования двоичных чисел,

а затем применить хорошо известные нам

принципы построения цифровой схемы по

произвольной таблице истинности.

стественно,

в приведенной на рисунке 10 схеме

рассматриваются только принципы работы

двоичных сумматоров. В реальных схемах

никогда не допускают последовательного

распространения переноса через все

разряды многоразрядного сумматора. Для

увеличения скорости работы двоичного

сумматора применяется отдельная схема

формирования переносов для каждого

двоичного разряда. Таблицу истинности

для такой схемы легко получить из

алгоритма суммирования двоичных чисел,

а затем применить хорошо известные нам

принципы построения цифровой схемы по

произвольной таблице истинности.

На этом пока закончим рассмотрение принципов работы сумматора, более сложные операции будут рассмотрены позднее, а пока для дальнейшего понимания работы операционного блока процессора необходимо научиться переключать двоичные числа на входах и выходе сумматора. Это позволяют сделать мультиплексоры и демультиплексоры, основной частью которых является дешифратор.

22 |

Импульсные устройства. (ДЕШИФРАТОРЫ). |

В левом нижнем углу схемы находится

двухразрядный декодер, который порождает

сигналы включения для четырех операций.

Выбор операции определяется сигналами

управления Fo и F1. В зависимости от

значений Fo и F1 выбирается одна из четырех

линий разрешения, и тогда выходной

сигнал выбранной функции проходит через

последний вентиль ИЛИ.

левом нижнем углу схемы находится

двухразрядный декодер, который порождает

сигналы включения для четырех операций.

Выбор операции определяется сигналами

управления Fo и F1. В зависимости от

значений Fo и F1 выбирается одна из четырех

линий разрешения, и тогда выходной

сигнал выбранной функции проходит через

последний вентиль ИЛИ.

Дешифраторы - это достаточно широкое понятие. В цифровой и вычислительной технике нередко применяются различные методы шифрования и последующей дешифровки данных. Устройства, применяемые в этом случае для шифрования, называются шифраторами, а устройства, применяемые для дешифровки, называются, соответственно, дешифраторами. Наверно правильно будет называть его: "Простой линейный дешифратор". Его назначение - преобразовать двоичный код в линейный. Рассмотрим это подробнее.

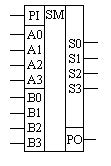

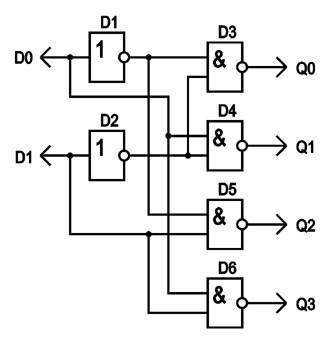

На вход дешифратора подается двоичное число, имеющее N двоичных разрядов (не менее двух). Для этого дешифратор имеет N специальных входов. Дешифратор так же имеет несколько выходов. Их количество никогда не превышает 2 в степени N. Почему, узнаем чуть позже. Выходной сигнал появляется лишь на том выходе дешифратора, номер которого соответствует двоичному числу на его входе. Рассмотрим это подробнее на примере. На рис. 1. приведена внутренняя схема дешифратора формата 2/4 (то есть два входа, четыре выхода).

Это минимальный дешифратор (меньше двух входов быть не может). На вход D0 подается младший разряд двух разрядного двоичного числа, а на вход D1 - старший разряд. Внутри дешифратора каждый из входных сигналов инвертируется. В результате получаются четыре сигнала: два прямых и два инвертированных. Затем эти сигналы подаются на выходные элементы "2И-НЕ" (D3 - D6). На каждый выходной элемент приходит один сигнал от D0, и один от D1, но каждый из них либо прямой, либо инверсный. Разводка сигналов сделана так, что при нужном сочетании сигналов на входе дешифратора на обоих входах соответствующего выходного элемента присутствуют логические единицы. Результат работы такого дешифратора хорошо понятен из его таблицы истинности:

D1 D0 Q3 Q2 Q1 Q0

0 0 1 1 1 0

0 1 1 1 0 1

1 0 1 0 1 1

1 1 0 1 1 1

Посмотрим внимательно на таблицу. Что мы можем увидеть?

1. Сигналы на входах D0 и D1 принимают все возможные комбинации значений. Этих комбинаций четыре (2 в степени 2). Ровно столько же имеется выходов у дешифратора. Для каждой комбинации - один выход. Такой дешифратор называется полным дешифратором. Если число выходов дешифратора меньше, чем число возможных комбинаций входных сигналов, то такой дешифратор называется неполным.

2. Если на входы дешифратора подано некое двоичное число, то на том его выходе, номер которого соответствует этому числу, появляется сигнал логического нуля. На остальных выходах устанавливается сигнал логической единицы. Это значит, что рассматриваемый дешифратор имеет инверсные выходы. В общем случае возможен дешифратор с прямыми выходами. У них на всех выходах ноль, а на активном выходе единица. Но так уж сложилось, что на практике применяются исключительно дешифраторы с инверсными выходами.

Основное предназначение дешифратора - выбирать (активизировать) одно из нескольких цифровых устройств по их номеру. Например, к описанному выше дешифратору можно подключить четыре микросхемы, имеющие вход выбора микросхемы CS (Chip Select). К каждому выходу дешифратора подключается вход CS одной из микросхем. Входы CS микросхем всегда выполняются таким образом, что при высоком логическом уровне на этом входе, микросхема отключается. При низком уровне на входе CS микросхема становится активной. Подав на вход дешифратора код номера нужной микросхемы, мы включим ее, а остальные окажутся выключенными.

23 |

Импульсные устройства. (МУЛЬТИПЛЕКСОРЫ). |

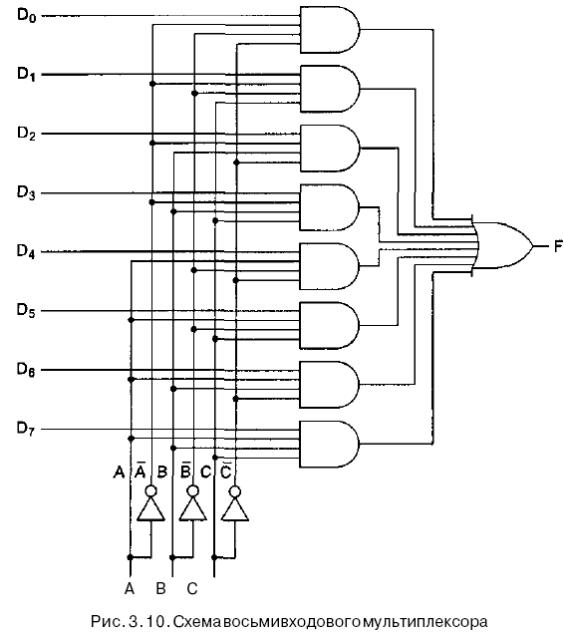

Н а

цифровом логическом уровне мультиплексор

представляет собой схему с 2" входами,

одним выходом и п линиями управления,

которые выбирают один из входов. Выбранный

вход соединяется с выходом. На рис. 3.10

изображена схема восьмивходового

мультиплексора. Три линии управления

А, В и С кодируют 3-бит-

а

цифровом логическом уровне мультиплексор

представляет собой схему с 2" входами,

одним выходом и п линиями управления,

которые выбирают один из входов. Выбранный

вход соединяется с выходом. На рис. 3.10

изображена схема восьмивходового

мультиплексора. Три линии управления

А, В и С кодируют 3-бит-

ное число, которое указывает, какая из восьми линий входа должна соединяться с вентилем ИЛИ и, следовательно, с выходом. Вне зависимости от того, какое значение будет на линиях управления, семь вентилей И будут всегда выдавать на выходе 0, а оставшийся может выдавать или 0, или 1 в зависимости от значения выбранной линии входа. Каждый вентиль И запускается определенной комбинацией линий управления. Схема мультиплексора показана на рис. 3.10. Если к этому добавить источник питания и «землю», то мультиплексор можно запаковать в корпус с 14 выводами.

Мы уже видели, как мультиплексор может использоваться для выбора одного из нескольких входов и как он может реализовать таблицу истинности. Его также можно использовать в качестве преобразователя параллельного кода в последовательный. Если подать 8 битов данных на линии входа, а затем переключать линии управления последовательно от 000 до 111 (это двоичные числа), 8 битов поступят на линию выхода последовательно. Обычно такое преобразование осуществляется при вводе информации с клавиатуры, поскольку каждое нажатие клавиши определяет 7- или 8-битное число, которое должно передаваться последовательно по телефонной линии.

Противоположностью мультиплексора является демультиплексор, который соединяет единственный входной сигнал с одним из 2" выходов в зависимости от значений п линий управления. Если бинарное значение линий управления равно к, то выбирается выход к.

24 |

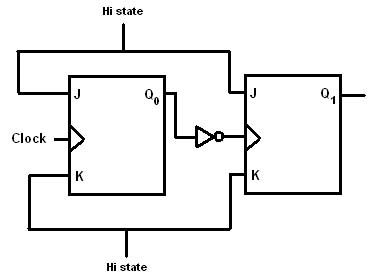

Импульсные устройства. (ТРИГГЕРЫ). |

Многие схемы выбирают значение на определенной линии в определенный момент времени и запоминают его. В такой схеме, которая называется триггером, переход состояния происходит не тогда, когда синхронизирующий сигнал равен 1, а во время перехода синхронизирующего сигнала с 0 на 1 (нарастающий фронт) или с 1 на 0 (задний фронт). Следовательно, длина синхронизирующего импульса не имеет значения, поскольку переходы происходят быстро. Подчеркнем еще раз различие между триггером и защелкой. Триггер запускается фронтом сигнала, а защелка запускается уровнем сигнала. Обратите внимание, что в литературе эти термины часто путаются. Многие авторы используют термин «триггер», когда речь идет о защелке, и наоборот.

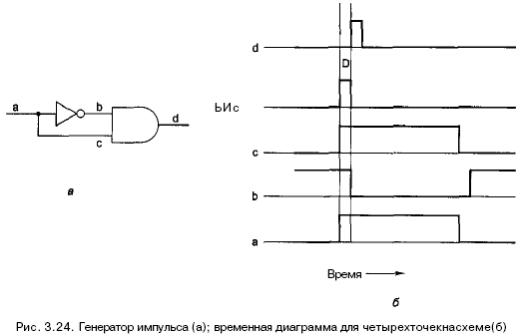

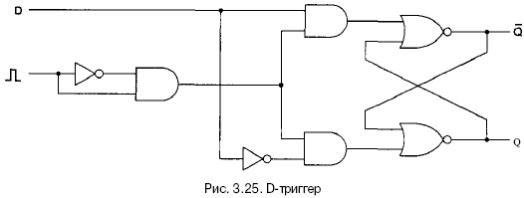

С уществует

несколько подходов к разработке

триггеров. Например, если бы существовал

способ генерирования очень короткого

импульса на нарастающем фронте

синхронизирующего сигнала, этот импульс

можно было бы подавать в D-защелку. В

действительности такой способ существует.

Соответствующая схема показана на рис.

3.24, а.

уществует

несколько подходов к разработке

триггеров. Например, если бы существовал

способ генерирования очень короткого

импульса на нарастающем фронте

синхронизирующего сигнала, этот импульс

можно было бы подавать в D-защелку. В

действительности такой способ существует.

Соответствующая схема показана на рис.

3.24, а.

На первый взгляд может показаться, что выход вентиля И всегда будет нулевым, поскольку функция И от любого сигнала с его инверсией дает 0, но на самом деле ситуация несколько более тонкая. При прохождении сигнала через инвертор

происходит небольшая, но все-таки не нулевая задержка. Данная схема работает именно благодаря этой задержке. Предположим, что мы измеряем напряжение в четырех точках а, b, с и d. Входовый сигнал в точке a представляет собой длинный

синхронизирующий импульс (см. нижний график на рис. 3.24, б). Сигнал в точке b показан над ним. Отметим, что этот сигнал инвертирован и подается с некоторой задержкой. Время задержки зависит от типа инвертора и обычно составляет несколько наносекунд.

Сигнал в точке c тоже подается с задержкой, но эта задержка обусловлена только временем прохождения сигнала (со скоростью света). Если физическое расстояние между а и c, например, 20 микрон, тогда задержка на распространение сигнала составляет 0,0001 нс, что, конечно, незначительно по сравнению со временем, которое требуется для прохождения сигнала через инвертор. Таким образом, сигнал в точке c практически идентичен сигналу в точке а.

К огда

входные сигналы b и с подвергаются

операции И, в результате получается

короткий импульс, длина которого (Д)

равна вентильной задержке инвертора

(обычно 5 нс и меньше). Выходной сигнал

вентиля И — данный импульс, сдвинутый

из-за задержки вентиля И (см. верхний

график на рис. 3 24, б). Этот временной

сдвиг означает только то, что D-защелка

активизируется с определенной задержкой

после нарастающего фронта синхронизирующего

импульса. Он никак не влияет на длину

импульса. В памяти со временем цикла в

50 нс импульс в 5 нс (который сообщает,

когда нужно выбирать линию D) достаточно

короткий, и в этом случае полная схема

может быть такой, какая изображена на

рис. 3.25. Следует упомянуть, что такая

схема триггера проста для понимания,

но на практике обычно используются

более сложные триггеры.

огда

входные сигналы b и с подвергаются

операции И, в результате получается

короткий импульс, длина которого (Д)

равна вентильной задержке инвертора

(обычно 5 нс и меньше). Выходной сигнал

вентиля И — данный импульс, сдвинутый

из-за задержки вентиля И (см. верхний

график на рис. 3 24, б). Этот временной

сдвиг означает только то, что D-защелка

активизируется с определенной задержкой

после нарастающего фронта синхронизирующего

импульса. Он никак не влияет на длину

импульса. В памяти со временем цикла в

50 нс импульс в 5 нс (который сообщает,

когда нужно выбирать линию D) достаточно

короткий, и в этом случае полная схема

может быть такой, какая изображена на

рис. 3.25. Следует упомянуть, что такая

схема триггера проста для понимания,

но на практике обычно используются

более сложные триггеры.

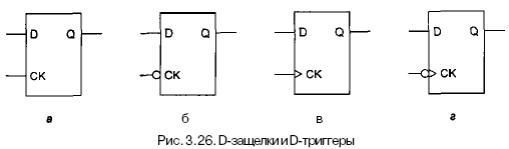

Стандартные изображения защелок и триггеров показаны на рис 3 26. На рис.3 26, а изображена защелка, состояние которой загружается тогда, когда синхронизирующий сигнал СК (от слова clock) равен 1, в противоположность защелке, изображенной на рис. 3.26,б, у которой синхронизирующий сигнал обычно равен 1, но переходит на 0, чтобы загрузить состояние из D. На рис. 3.26, виг изображены триггеры. То, что это триггеры, а не защелки, показано с помощью уголка при синхронизирующем входе. Триггер на рис. 3.26, в изменяет состояние на возрастающем фронте синхронизирующего импульса (переход от 0 к 1), тогда как триггер на рис 3.26, г изменяет состояние на заднем фронте (переход от 0 к 1). Многие (хотя не все) защелки и триггеры также имеют выход У, а у некоторых есть два дополнительных входа. Set (установка) или Preset (предварительная установка) и Reset (сброс) или Clear (очистка). Первый вход (Set или Preset) устанавливает Q=l, а второй (Reset или Clear) — Q=0.

25 |

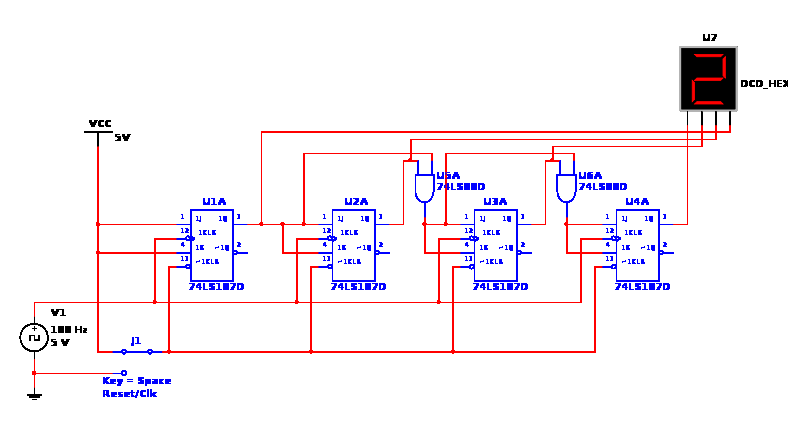

Импульсные устройства. (СЧЕТЧИКИ). |

С чётчик

числа импульсов — устройство, на выходах

которого получается двоичный

(двоично-десятичный) код, определяемый

числом поступивших импульсов. Счётчики

могут строиться на T-триггерах. Основной

параметр счётчика — модуль счёта —

максимальное число единичных сигналов,

которое может быть сосчитано счётчиком.

Счётчики обозначают через СТ (от англ.

counter).

чётчик

числа импульсов — устройство, на выходах

которого получается двоичный

(двоично-десятичный) код, определяемый

числом поступивших импульсов. Счётчики

могут строиться на T-триггерах. Основной

параметр счётчика — модуль счёта —

максимальное число единичных сигналов,

которое может быть сосчитано счётчиком.

Счётчики обозначают через СТ (от англ.

counter).

26 |

Импульсные устройства. (РЕГИСТРЫ). |

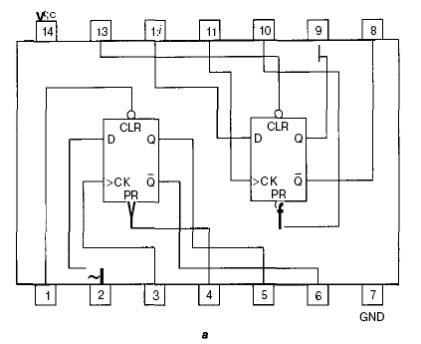

Существуют различные конфигурации триггеров. На рисунке 3.27, а изображена схема, содержащая два независимых D-триггера с сигналами предварительной установки и очистки. Хотя эти два триггера находятся на одной микросхеме с 14 выводами, они не связаны между собой. Совершенно по-другому устроен восьмиразрядный триггер, изображенный на рис. 3.27, б. Здесь, в отличие от предыдущей схемы, у восьми триггеров нет выхода (J и линий предварительной установки и все синхронизирующие линии связаны вместе и управляются выводом 11. Сами триггеры того же типа, что на рис. 3.26, г, но инвертирующие входы аннулируются инвертором, связанным с выводом 11, поэтому триггеры запускаются при переходе от 0 к 1. Все восемь сигналов очистки также объединены, поэтому когда вывод 1 переходит в состояние 0, все триггеры также переходят в состояние 0. Если вам не понятно, почему вывод 11 инвертируется на входе, а затем инвертируется снова при каждом сигнале СК, то ответ прост: входной сигнал не имеет достаточной

мощности, чтобы запустить все восемь триггеров; входной инвертор на самом деле используется в качестве усилителя. Одна из причин объединения линий синхронизации и линий очистки в микросхеме на рис. 3.27, б – экономия выводов. С другой стороны, микросхема данной конфигурации несколько отличается от восьми несвязанных триггеров. Эта микросхема используется в качестве одного 8-разрядного регистра. Две такие микросхемы могут работать параллельно, образуя 16-разрядный регистр. Для этого нужно связать соответствующие выводы 1 и 11.

27 |

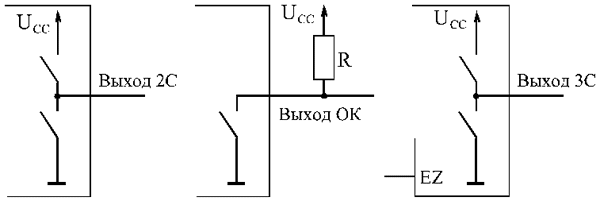

Импульсные устройства. (ОРГАНИЗАЦИЯ ВЫХОДОВ МИКРОСХЕМ). |

Выходы микросхем принципиально отличаются от входов тем, что учет их особенностей необходим даже на первом и втором уровнях представления.

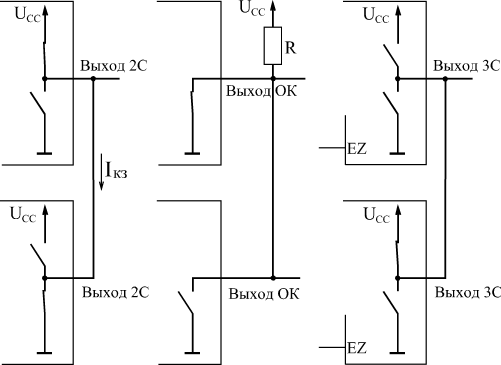

Существуют три разновидности выходных каскадов, существенно различающиеся как по своим характеристикам, так и по областям применения:

стандартный выход или выход с двумя состояниями (обозначается 2С, 2S или, реже, ТТЛ, TTL);

выход с открытым коллектором (обозначается ОК, OC);

выход с тремя состояниями или (что то же самое) с возможностью отключения (обозначается 3С, 3S).

Стандартный выход 2С имеет всего два состояния: логический нуль и логическая единица, причем оба они активны, то есть выходные токи в обоих этих состояниях (IOL и IOH) могут достигать заметных величин. На первом и втором уровнях представления такой выход можно считать состоящим из двух выключателей, которые замыкаются по очереди (рис. 1.9), причем замкнутому верхнему выключателю соответствует логическая единица на выходе, а замкнутому нижнему — логический нуль.

Р ис.

1.9. Три типа выходов цифровых микросхем

ис.

1.9. Три типа выходов цифровых микросхем

Выход с открытым коллектором ОК тоже имеет два возможных состояния, но только одно из них (состояние логического нуля) активно, то есть обеспечивает большой втекающий ток IOL. Второе состояние сводится, по сути, к тому, что выход полностью отключается от присоединенных к нему входов. Это состояние может использоваться в качестве логической единицы, но для этого между выходом ОК и напряжением питания необходимо подключить нагрузочный резистор R (так называемый pull-up) величиной порядка сотен Ом. На первом и втором уровнях представления такой выход можно считать состоящим из одного выключателя (рис. 1.9), замкнутому состоянию которого соответствует сигнал логического нуля, а разомкнутому — отключенное, пассивное состояние. Правда, от величины резистора R зависит время переключения выхода из нуля в единицу, что влияет на задержку tLH, но при обычно используемых номиналах резисторов это не слишком важно.

Наконец, выход с тремя состояниями 3С очень похож на стандартный выход, но к двум состояниям добавляется еще и третье — пассивное, в котором выход можно считать отключенным от последующей схемы. На первом и втором уровнях представления такой выход можно считать состоящим из двух переключателей (рис. 1.9), которые могут замыкаться по очереди, давая логический нуль и логическую единицу, но могут и размыкаться одновременно. Это третье состояние называется также высокоимпедансным или Z-состоянием. Для перевода выхода в третье Z-состояние используется специальный управляющий вход, обозначаемый OE (Output Enable — разрешение выхода) или EZ (Enable Z-state).

Почему же помимо стандартного выхода (2С) были предложены еще два типа выходов (ОК и 3С)? Дело в том, что выходы, имеющие помимо активных еще и пассивное состояние, очень удобны для объединения их между собой. Например, если на один и тот же вход надо по очереди подавать сигналы с двух выходов (рис. 1.10), то выходы 2С для этого не подходят, а вот выходы ОК и 3С — подходят.

При объединении двух или более выходов 2С вполне возможна ситуация, при которой один выход стремится выдать сигнал логической единицы, а другой — сигнал логического нуля. Легко заметить, что в этом случае через верхний замкнутый ключ выхода, выдающего единицу, и через нижний замкнутый ключ выхода, выдающего нуль, пойдет недопустимо большой ток короткого замыкания Iкз. Это аварийная ситуация, при которой уровень получаемого выходного логического сигнала точно не определен — он может восприниматься последующим входом и как нуль, и как единица. Конфликтующие выходы могут даже выйти из строя, нарушив работу микросхем и схемы в целом.

Зато в случае объединения двух выходов ОК такого конфликта в принципе произойти не может. Даже если ключ одного выхода замкнут, а другого — разомкнут, аварийной ситуации не произойдет, так как недопустимо большого тока не будет, а на объединенном выходе будет сигнал логического нуля. А при объединении двух выходов 3С аварийная ситуация хоть и возможна (если оба выхода одновременно находятся в активном состоянии), но ее легко можно предотвратить, если организовать схему так, что в активном состоянии всегда будет находиться только один из объединенных выходов 3С.

Р ис.

1.10. Объединение выходов цифровых

микросхем

ис.

1.10. Объединение выходов цифровых

микросхем

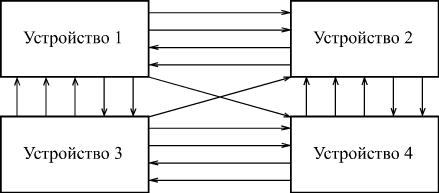

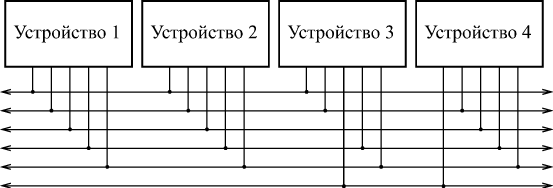

Объединение выходов цифровых микросхем совершенно необходимо также при шинной (или, как еще говорят, магистральной) организации связей между цифровыми устройствами. Шинная организация связей применяется, например, в компьютерах и в других микропроцессорных системах. Суть ее сводится к следующему.

При классической организации связей (рис. 1.11) все сигналы между устройствами передаются по своим отдельным линиям (проводам). Каждое устройство передает свои сигналы всем другим независимо от других устройств. В этом случае обычно получается очень много линий связи, к тому же правила обмена сигналами по этим линиям (или протоколы обмена) чрезвычайно разнообразны.

Р ис.

1.11. Классическая организация связей

ис.

1.11. Классическая организация связей

Рис. 1.12. Шинная организация связей

При шинной же организации связей (рис. 1.12) все сигналы между устройствами передаются по одним и тем же линиям (проводам), но в разные моменты времени (это называется временным мультиплексированием). В результате количество линий связи резко сокращается, а правила обмена сигналами существенно упрощаются. Группа линий (сигналов), используемая несколькими устройствами, как раз и называется шиной. Понятно, что объединение выходов в этом случае совершенно необходимо — ведь каждое устройство должно иметь возможность выдавать свой сигнал на общую линию. К недостаткам шинной организации относится прежде всего невысокая (по сравнению с классической структурой связей) скорость обмена сигналами. При простых структурах связи она может быть избыточна.

Но вернемся к типам выходов цифровых микросхем.

На третьем уровне представления (электрическая модель) необходимо уже учитывать, что выходные ключи (рис. 1.9) представляют собой не простые тумблеры (как на первых двух уровнях представления), а транзисторные ключи со своими специфическими параметрами. Однако в большинстве случаев достаточно знать, какой ток может выдать данный выход при логическом нуле (IOL) и при логической единице (IOH). Величины этих токов не должны превышать суммы токов всех входов, подключенных к данному выходу (соответственно IIL и IIH). Количеством входов, которое можно подключить к одному выходу, определяется коэффициент разветвления или нагрузочную способность микросхемы. Существуют микросхемы с обычной нагрузочной способностью и с повышенной нагрузочной способностью (больше обычной в два раза и более). Выходы 3С, как правило, имеют повышенную нагрузочную способность (то есть обеспечивают большие выходные токи). Выходы 2С и ОК могут быть как с обычной, так и с повышенной нагрузочной способностью.

Также на третьем уровне представления (электрическая модель) необходимо учитывать выдаваемые выходом микросхемы величины выходных напряжений UOL и UOH. Выходы ОК могут быть рассчитаны как на обычное выходное напряжение логической единицы (UOH = UCC = 5 В), так и на повышенное напряжение логической единицы (до 30 В). В последнем случае внешний резистор этого выхода (см. рис. 1.9) подключается к источнику повышенного напряжения.

Только в сложных случаях, например, при переводе логического элемента в линейный режим за счет обратных связей, нужен учет других параметров входных и выходных каскадов. Но в этих редких случаях гораздо проще и надежнее не считать ничего самому, а воспользоваться стандартными схемами включения микросхем или подобрать режимы работы и номиналы внешних элементов (резисторов, конденсаторов) непосредственно на макете проектируемого устройства. В отличие от расчетов, такой подход даст полную гарантию работоспособности выбранного решения.

29 |

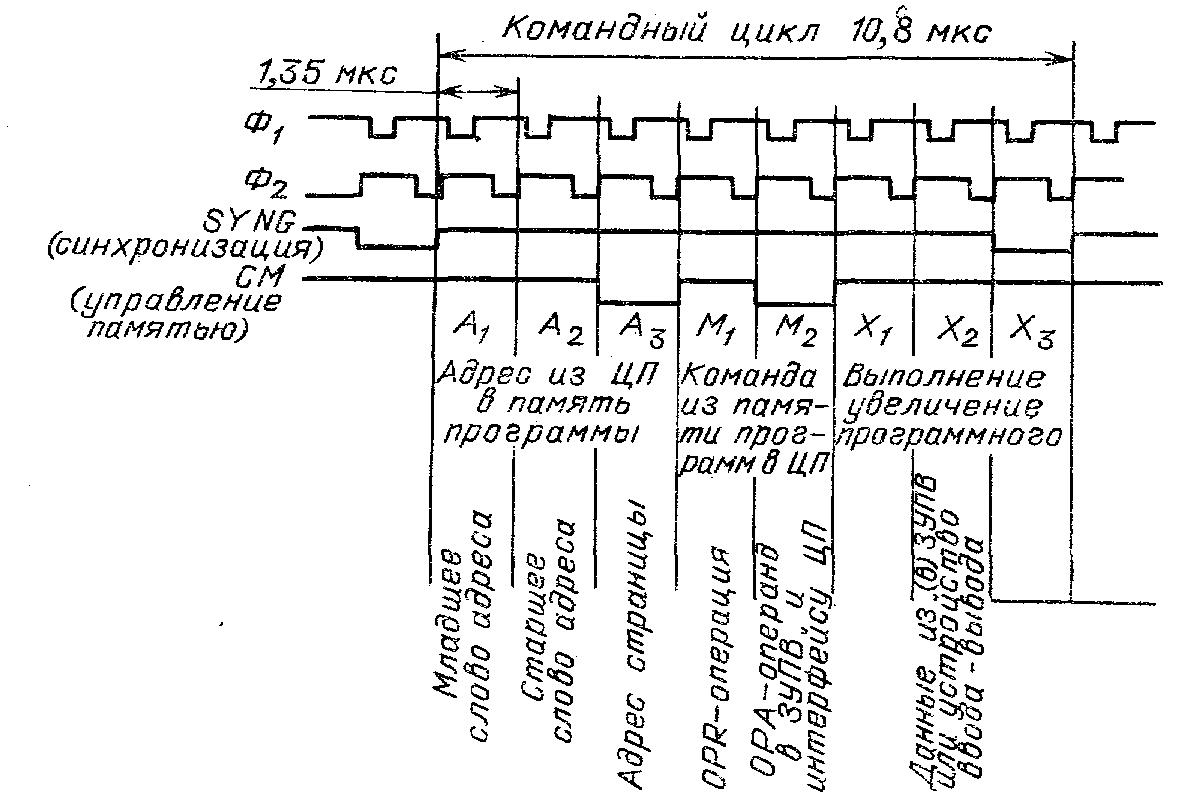

Примеры выполнения команд в ЭВМ. Одноцикловые команды. |

О дноцикловая

операция выполняется по тактам следующим

образом. В течение 3-х тактов Л^аЛз ЦП

выдает по шине данных адрес в ПЗУ в

виде 3-х полубайтов. По этому адресу

выбирается микросхема и в ней — одно

слово из 8 бит. В течение тактов М\, М-г.

по 4-битовой шине данных в ЦП на регистр

команд выдается 8-битовая команда. В

тактах Х\, Ху, Хз производится выполнение

команды, причем один операнд берется

из аккумулятора, второй — из ОЗУ,

результат остается в аккумуляторе. Во

время этих же тактов производится

увеличение на 1 содержимого счетчика

команд, чем подготавливается выборка

команды для следующего цикла.

дноцикловая

операция выполняется по тактам следующим

образом. В течение 3-х тактов Л^аЛз ЦП

выдает по шине данных адрес в ПЗУ в

виде 3-х полубайтов. По этому адресу

выбирается микросхема и в ней — одно

слово из 8 бит. В течение тактов М\, М-г.

по 4-битовой шине данных в ЦП на регистр

команд выдается 8-битовая команда. В

тактах Х\, Ху, Хз производится выполнение

команды, причем один операнд берется

из аккумулятора, второй — из ОЗУ,

результат остается в аккумуляторе. Во

время этих же тактов производится

увеличение на 1 содержимого счетчика

команд, чем подготавливается выборка

команды для следующего цикла.

Если выполняется команда ввода-вывода, то в течение такта Х-2 происходит обмен данными между аккумулятором ЦП и внешним устройством ВУ по 4-м линиям ввода-вывода ПЗУ.

30 |

Программно доступные регистры (программная модель ЭВМ, 8-и разрядный). |

Программно-доступные восьмиразрядные регистры используются для ввода и вывода. Максимальное число регистров для ввода данных составляет 256, для вывода данных — столько же.

Команды микропроцессора используют только те элементы данных, обработка которых осуществляется непосредственно микропроцессором, т. е. восьми- и шестнадцатибитовые. Восьмибитовые данные — это восемь бит (один байт), которые хранятся в РОН или ячейке памяти и обрабатываются микропроцессором как одно целое.

Шестнадцатибитовые данные — это 16 бит (два байта) данных, которые могут храниться в шестнадцатиразрядном регистре или в двух последовательных ячейках памяти и обрабатываются микропроцессором как одно целое, причем в памяти старшие восемь бит записываются по адресу на единицу большему, чем адрес младших. При адресации шестнадцатибитовых данных указывается адрес младшей ячейки памяти, содержащей эти данные.

Операнды команд могут храниться в программно-доступных регистрах микропроцессора или в памяти МПС. Для указания операнда в регистре используются: регистровая адресация и регистровая неявная адресация.

Регистр процессора — сверхбыстрая память внутри процессора, предназначенная прежде всего для хранения промежуточных результатов вычисления (регистр общего назначения/регистр данных) или содержащая данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д. (специальные регистры).

Регистр представляет собой цифровую электронную схему, служащую для временного хранения двоичных чисел. В процессоре имеется значительное количество регистров, большая часть которых используется самим процессором и недоступна программисту. Например, при выборке из памяти очередной команды она помещается в регистр команд. Программист обратиться к этому регистру не может. Имеются так же регистры, которые в принципе программно доступны, но обращение к ним осуществляется из программ операционной системы (например управляющие регистры и теневые регистры дескрипторов сегментов). Этими регистрами пользуются в основном разработчики операционных систем.

Доступ к значениям, хранящимся в регистрах как правило в несколько раз быстрее, чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1-4 Гб[1], суммарная «ёмкость» регистров общего назначения/данных для процессора Intel 80x86 16 битов * 4 = 64 бита (8 байт)).

x86

IP (англ. Instruction Pointer) — регистр, обозначающий смещение следующей команды относительно кодового сегмента.

IP — 16-битный (младшая часть EIP)

EIP — 32-битный аналог

Сегментные регистры — Регистры указывающие на сегменты.

CS,DS,SS,ES,FS,GS

CS — указатель на кодовый сегмент. Связка CS:IP указывает на адрес в памяти следующей команды.

Регистры данных — служат для хранения промежуточных вычислений.

RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, R8 — R15 — 64-битные

EAX, EBX, ECX, EDX, EBP, ESI, EDI, ESP — 32-битные (extended AX)

AX, BX, CX, DX — 16-битные

AH, AL, BH, BL, CH, CL, DH, DL — 8-битные (половинки 16-ти битных регистров)

например, AH - high AX - старшая половинка 8 бит

AL - low AX - младшая половинка 8 бит

RAX RBX RCX RDX

—— EAX —— EBX —— ECX —— EDX

—— —— AX —— —— BX —— —— CX —— —— DX

—— —— AH AL —— —— BH BL —— —— CH CL —— —— DH DL

Регистр флагов EFLAGS — содержит текущее состояние процессора.

Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. По типу приёма и выдачи информации различают 2 типа регистров:

С последовательным приёмом и выдачей информации — сдвиговые регистры.

С параллельным приёмом и выдачей информации — параллельные регистры.

Сдвиговые регистры представляют собой последовательно соединённую цепочку триггеров. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

По назначению регистры различаются на:

аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

флаговые — хранят признаки результатов арифметических и логических операций;

общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

индексные — хранят индексы исходных и целевых элементов массива;

указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека);

сегментные — хранят адреса и селекторы сегментов памяти;

управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Счётчик команд

IP (англ. Instruction Pointer) — регистр, содержащий адрес-смещение следующей команды, подлежащей исполнению, относительно кодового сегмента CS в процессорах семейства x86.

Регистр IP связан с CS в виде CS:IP, где CS является текущим кодовым сегментом, а IP — текущим смещением относительно этого сегмента.

Регистр IP является 16-разрядным регистром-указателем. Кроме него, в состав регистров этого типа входят SP (англ. Stack Pointer — указатель стека) и BP (англ. Base Pointer — базовый указатель).

Принцип работы

Например, CS содержит значение 2CB5[0]H, в регистре IP хранится смещение 123H.

Адрес следующей инструкции, подлежащей исполнению вычисляется путем суммирования адреса в CS (сегменте кода) со смещением в регистре IP:

2CB50H + 123H = 2CC73H

Таким образом, адрес следующей инструкции для исполнения равен 2CC73H.

При выполнении текущей инструкции процессор автоматически изменяет значение в регистре IP, в результате чего регистровая пара CS:IP всегда указывает на следующую подлежащую исполнению инструкцию.

EIP

Начиная с процессора 80386 была введена 32-разрядная версия регистра-указателя — EIP. В данном случае IP является младшей частью этого регистра (первые 16 разрядов). Принцип работы EIP в целом схож с работой регистра IP. Основная разница состоит в том, что в защищённом режиме, в отличие от реального режима, регистр CS является селектором (селектор указывает не на сам сегмент в памяти, а на его дескриптор сегмента в таблице дескрипторов).

RIP

В 64-разрядных процессорах используется свой регистр-указатель инструкций — RIP.

Младшей частью этого регистра является регистр EIP.

На основе RIP в 64-разрядных процессорах введён новый метод адресации RIP-relative. В остальном работа RIP аналогична работе регистра EIP.

31 |

Структурная схема 16-и разрядного процессора (Intel). |

П ервый

16-разрядный процессор i8086 фирма Intel

выпустила в 1978 году. Частота - 5 Мгц,

производительность - 0,33 MIPS для инструкций

с 16-битными операндами (позже появились

процессоры 8 и 10 МГц). Технология 3 мкм,

29 000 транзисторов. Адресуемая память 1

Мбайт. Через год появился i8088 - тот же

процессор, но с 8-разрядной шиной данных.

С него началась история IBM PC, неразрывно

связанная со всем дальнейшим развитием

процессоров Intel. 16-разрядный МП i8086 явился

дальнейшим развитием линии однокристальных

МП, начатой i8080. Наряду с увеличением

разрядности в i8086 реализован ряд новых

архитектурных решений: 1) расширена

система команд (по набору операций и

способам адресации); 2) архитектура МП

ориентирована на мультипроцессорную

работу. Разработана группа вспомогательных

БИС (контроллеров и специализированных

процессоров) для организации

мультимикропроцессорных систем различной

конфигурации; 3) начато движение в сторону

совмещения во времени выполнения

различных операций. МП включает два

параллельно работающих устройства 4)

обработки данных и связи с магистралью,

что позволяет совместить во времени

процессы обработки информации и передачи

ее по магистрали; 5) введена новая (по

сравнению с i8080) организация памяти,

которая далее использовалась во всех

старших моделях семейства INTEL - сегментация

памяти. Для сохранения преемственности

модели с i8080 в i8086 предусмотрено два

режима работы - "минимальный" и

"максимальный", причем в минимальном

режиме i8086 работает просто как достаточно

быстрый 16-разрядный i8080 с расширенной

системой команд (архитектура МПС на

базе i8086-min напоминает архитектуру на

базе i8080). Максимальный режим ориентирован

на работу i8086 в составе мультимикропроцессорных

систем, в которых, помимо нескольких

центральных процессоров i8086, могут

функционировать специализированные

процессоры ввода/вывода i8089, сопроцессоры

"плавающей арифметики" i8087.

Центральный процессор – поддерживает

собственный командный цикл, выполняет

программу, хранящуюся в системной

памяти, по сбросу системы управление,

как правило, передается центральному

процессору (или одному из ЦП, если их

несколько в системе). Специализированный

процессор – поддерживает собственный

командный цикл, выполняет программу,

хранящуюся в системной памяти, но

инициализируется только по команде ЦП,

по окончании выполнения программы

сообщает ЦП о завершении работы.

Сопроцессор не поддерживает собственный

командный цикл, выполняет команды,

выбираемые для него ЦП из общего потока

команд. По сути дела сопроцессор является

расширением ЦП.

ервый

16-разрядный процессор i8086 фирма Intel

выпустила в 1978 году. Частота - 5 Мгц,

производительность - 0,33 MIPS для инструкций

с 16-битными операндами (позже появились

процессоры 8 и 10 МГц). Технология 3 мкм,

29 000 транзисторов. Адресуемая память 1

Мбайт. Через год появился i8088 - тот же

процессор, но с 8-разрядной шиной данных.

С него началась история IBM PC, неразрывно

связанная со всем дальнейшим развитием

процессоров Intel. 16-разрядный МП i8086 явился

дальнейшим развитием линии однокристальных

МП, начатой i8080. Наряду с увеличением

разрядности в i8086 реализован ряд новых

архитектурных решений: 1) расширена

система команд (по набору операций и

способам адресации); 2) архитектура МП

ориентирована на мультипроцессорную

работу. Разработана группа вспомогательных

БИС (контроллеров и специализированных

процессоров) для организации

мультимикропроцессорных систем различной

конфигурации; 3) начато движение в сторону

совмещения во времени выполнения

различных операций. МП включает два

параллельно работающих устройства 4)

обработки данных и связи с магистралью,

что позволяет совместить во времени

процессы обработки информации и передачи

ее по магистрали; 5) введена новая (по

сравнению с i8080) организация памяти,

которая далее использовалась во всех

старших моделях семейства INTEL - сегментация

памяти. Для сохранения преемственности

модели с i8080 в i8086 предусмотрено два

режима работы - "минимальный" и

"максимальный", причем в минимальном

режиме i8086 работает просто как достаточно

быстрый 16-разрядный i8080 с расширенной

системой команд (архитектура МПС на

базе i8086-min напоминает архитектуру на

базе i8080). Максимальный режим ориентирован

на работу i8086 в составе мультимикропроцессорных

систем, в которых, помимо нескольких

центральных процессоров i8086, могут

функционировать специализированные

процессоры ввода/вывода i8089, сопроцессоры

"плавающей арифметики" i8087.

Центральный процессор – поддерживает

собственный командный цикл, выполняет

программу, хранящуюся в системной

памяти, по сбросу системы управление,

как правило, передается центральному

процессору (или одному из ЦП, если их

несколько в системе). Специализированный

процессор – поддерживает собственный

командный цикл, выполняет программу,

хранящуюся в системной памяти, но

инициализируется только по команде ЦП,

по окончании выполнения программы

сообщает ЦП о завершении работы.

Сопроцессор не поддерживает собственный

командный цикл, выполняет команды,

выбираемые для него ЦП из общего потока

команд. По сути дела сопроцессор является

расширением ЦП.

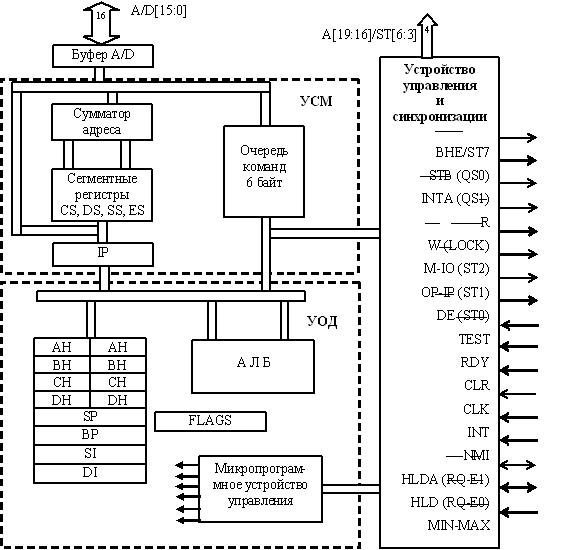

Внутренняя структура

Структурная схема МП i8086 представлена на рис. МП включает в себя три основных устройства : • УОД - устройство обработки данных; • УСМ - устройство связи с магистралью; • УУС - устройство управления и синхронизации. УОД предназначено для выполнения команд и включает в себя 16-разрядное АЛУ, системные регистры и другие вспомогательные схемы; блок регистров (РОН, базовые и индексные) и блок микропрограммного управления. УСМ обеспечивает формирование 20-разрядного физического адреса памяти и 16-разрядного адреса ВУ, выбор команд из памяти, обмен данными с ЗУ, ВУ, другими процессорами по магистрали. УСМ включает в себя сумматор адреса, блок регистров очереди команд и блок сегментных регистров. УУС обеспечивает синхронизацию работы устройств МП, выработку управляющих сигналов и сигналов состояния для обмена с другими устройствами, анализ и соответствующую реакцию на сигналы других устройств МПС. МП может работать в одном из двух режимов - "минимальном" (min) и "максимальном" (max). Минимальный режим предназначен для реализации однопроцессорной конфигурации МПС с организацией, подобной МПС на базе i8080, но с увеличенным адресным пространством, более высоким быстродействием и значительно расширенной системой команд. Максимальная конфигурация предполагает наличие в системе нескольких МП и специального блока арбитра магистрали (используется интерфейс Multibus). На внешних выводах МП i8086 широко используется принцип мультиплексирования сигналов - передача разных сигналов по общим линиям с разделением во времени. Кроме того, одни и те же выводы могут использоваться для передачи разных сигналов в зависимости от режима (min - max). Ниже приводится описание внешних выводов МП i8086. При описании выводов косой чертой разделены сигналы, появляющиеся на выводе в разные моменты машинного цикла. В круглых скобках указаны сигналы, характерные только для максимального режима. Символ \ после имени сигнала - знак его инверсии.

A/D[15:0] - младшие [15:0] разряды адреса / данные; A[19:16]/ST[6:3] - старшие [19:16] разряды адреса / сигналы состояния; BHE\/ST[7] - разрешение передачи старшего байта данных / сигнал состояния; STB(QS0) - строб адреса (состояние очереди команд); R\ - чтение; W\/(LOCK\) - запись (блокировка канала); M-IO\(ST2\) - память - внешнее устройство (состояние цикла); OP-IP\(ST1\) - выдача-прием (состояние цикла); DE\(ST0\) - разрешение передачи данных (сост. цикла); TEST\ - проверка; RDY - готовность; CLR - сброс; CLC - тактовый сигнал; INT - запрос внешнего прерывания; INTA\(QS1) - подтверждение прерывания (состояние очереди команд); NMI - запрос немаскируемого прерывания; HLD(RQ\/E0) - запрос ПДП (запрос / подтверждение доступа к магистрали); NLDA(RQ\/E1) - подтверждение ПДП (запрос / подтверждение доступа к магистрали); MIN/MAX\ - потенциал задания режима (1-min, 0-max). Сигналы состояния ("статуса") используются для отображения внутреннего состояния МП. Некоторые группы статусных сигналов используются только в максимальном режиме.

32 |

Обслуживание внешних устройств методом аппаратных прерываний. |

Подсистема прерываний - совокупность аппаратных и программных средств, обеспечивающих реакцию программы на события, происходящие вне программы. Такие события возникают, как правило, случайно и асинхронно по отношению к программе и требуют прекращения (чаще временного) выполнения текущей программы и переход на выполнение другой программы (подпрограммы), соответствующей возникшему событию.

Внутренние и внешние прерывания

Различают внутренние и внешние (по отношению к процессору) события, требующие реакции подсистемы прерываний. К внутренним событиям относятся переполнение разрядной сетки при выполнении арифметических операций, попытка деления на 0, извлечение корня четной степени из отрицательного числа и т.п., появление несуществующего кода команды, обращение программы в область памяти, для нее не предназначенную, сбой при выполнении передачи или операции в АЛУ и многое другое. Внутренние прерывания должны обеспечиваться развитой системой аппаратного контроля процессора, поэтому они не получили широкого распространения в простых 8- и 16-разрядных МП. Внешние прерывания могут возникать во внешней по отношению к процессору среде и отмечать как аварийные ситуации (кончилась бумага на принтере, температура в реакторе превысила допустимый уровень, исполнительный орган робота дошел до предельного положения и т.п.), так и нормальные рабочие события, которые происходят в случайные моменты времени (нажатие клавиши на клавиатуре, исчерпан буфер принтера или ВЗУ и т.п.). Во всех этих случаях требуется прервать выполнение текущей программы и перейти на выполнение другой программы (подпрограммы), обслуживающей это событие. С точки зрения реализации внутренние и внешние прерывания функционируют одинаковым образом, хотя при работе подсистемы с внешними прерываниями возникают дополнительные проблемы идентификации источника прерывания. Поэтому ниже будут рассмотрены внешние прерывания. Анализ состояния внешней среды можно осуществлять путем программного сканирования - считывания через определенные промежутки времени слов состояния всех возможных источников прерываний, выделения признаков отслеживаемых событий и переход (при необходимости) на прерывающую подпрограмму. Однако, такой способ не обеспечивает для большинства применений приемлемого времени реакции системы на события, особенно при необходимости отслеживания большого числа событий. К тому же при коротком цикле сканирования большой процент процессорного времени тратится на проверку (чаще безрезультатную) состояния внешней среды. Гораздо эффективней организовать взаимодействие с внешней средой таким образом, чтобы всякое изменение состояния среды, требующее реакции МПС, вызывало появление на специальном входе МП сигнала прерывания текущей программы. Организация прерываний должна быть обеспечена определенными аппаратными и программными средствами, которые мы и называем "подсистемой прерываний".

Функции подсистемы прерываний и их реализация

П одсистема

прерываний должна обеспечивать выполнение

следующих функций: 1) обнаружение

изменения состояния внешней среды

(запрос на прерывание); 2) идентификация

источника прерывания; 3) разрешение

конфликтной ситуации в случае

одновременного возникновения нескольких

запросов (приоритет запросов); 4)

определение возможности прерывания

текущей программы (приоритет программ);

5) фиксация состояния прерываемой

(текущей) программы; 6) переход к программе,

соответствующей обслуживаемому

прерыванию; 7) возврат к прерванной

программе после окончания работы

прерывающей программы. Рассмотрим

варианты реализации в МПС перечисленных

выше функций. (1) Фиксация изменения

состояния внешней среды может

осуществляться различными средствами:

двоичными датчиками, компараторами,

схемами формирования состояний и т.п.

Будем полагать, что все эти средства

формируют в конечном итоге логические

сигналы запроса на прерывание z, причем

для определенности будем считать, что

активное состояние этого сигнала

передается уровнем логической единицы

(H - уровень). Количество источников

запросов в МПС может быть различно, в

том числе и довольно велико. Дефицит

внешних выводов МП исключает возможность

передачи запросов от ВУ по "собственным"

линиям интерфейса. Обычно на одну линию

запроса подключается несколько источников

прерываний (по функции ИЛИ), а иногда и

все источники системы - на единственный

вход (как в i8080).

одсистема

прерываний должна обеспечивать выполнение

следующих функций: 1) обнаружение

изменения состояния внешней среды

(запрос на прерывание); 2) идентификация

источника прерывания; 3) разрешение

конфликтной ситуации в случае

одновременного возникновения нескольких

запросов (приоритет запросов); 4)

определение возможности прерывания

текущей программы (приоритет программ);

5) фиксация состояния прерываемой

(текущей) программы; 6) переход к программе,

соответствующей обслуживаемому

прерыванию; 7) возврат к прерванной

программе после окончания работы

прерывающей программы. Рассмотрим

варианты реализации в МПС перечисленных

выше функций. (1) Фиксация изменения

состояния внешней среды может

осуществляться различными средствами:

двоичными датчиками, компараторами,

схемами формирования состояний и т.п.

Будем полагать, что все эти средства

формируют в конечном итоге логические

сигналы запроса на прерывание z, причем

для определенности будем считать, что

активное состояние этого сигнала

передается уровнем логической единицы

(H - уровень). Количество источников

запросов в МПС может быть различно, в

том числе и довольно велико. Дефицит

внешних выводов МП исключает возможность

передачи запросов от ВУ по "собственным"

линиям интерфейса. Обычно на одну линию

запроса подключается несколько источников

прерываний (по функции ИЛИ), а иногда и

все источники системы - на единственный

вход (как в i8080).

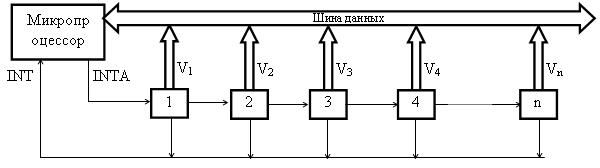

Рис. 5.1. Организация векторного прерывания

Различают два типа входов запросов на прерывания - радиальные и векторные. Процессор анализирует состояние входов запросов в конце каждого машинного цикла. (2) Получив запрос на прерывание, процессор должен идентифицировать его источник, т.е. в конечном счете, определить начальный адрес обслуживающей это прерывание программы. Способ идентификации зависит от типа входа, на который поступил запрос. Каждый радиальный вход связан с определенным адресом памяти, по которому размещается указатель на обслуживающую программу или сама программа. Если на радиальный вход поступает несколько запросов, то необходимо осуществить программную идентификацию источника путем последовательного (в порядке убывания приоритетов) опроса всех возможных источников прерывания. Этот способ не требует дополнительных аппаратных затрат и одновременно решает проблему приоритета запросов (3), однако время реакции системы на запрос может оказаться недопустимо велико, особенно при большом числе источников прерываний. Гораздо чаще в современных МПС используется т.н. "векторная" подсистема прерываний (Рис. 5.1). В такой системе микропроцессор, получив запрос на векторном входе INT, выдает на свою выходную линию сигнал подтверждения прерывания INTA, поступающий на все возможные источники прерывания. Источник, не выставивший запроса, никак не реагирует на сигнал INTA. Источник, выставивший запрос, получая сигнал INTA, выдает на системную шину данных "вектор прерывания" – свой номер или адрес обслуживающей программы или, чаще, адрес памяти, по которому расположен указатель на обслуживающую программу. Время реакции МПС на запрос векторного прерывания минимально (1..3 машинных цикла) и не зависит от числа источников. (3) Для исключения конфликтов при одновременном возникновении нескольких запросов на векторном входе ответный сигнал INTA подается на источники запросов не параллельно, а последовательно – в порядке убывания приоритетов запросов. Источник, не выставлявший запроса, транслирует сигнал INTA со своего входа на выход, а источник, выставивший запрос, блокирует дальнейшее распространение сигнала INTA. Таким образом, только один источник, выставивший запрос, получит от процессора сигнал INTA и выдаст по нему свой вектор на шину данных. Более гибко решается проблема организации приоритетов запросов при использовании в МПС специальных контроллеров прерываний (см. ниже). Конфликты на радиальном входе исключаются самим порядком программного опроса источников. (4) Прерывание в общем случае может возникать не только при решении "фоновой" задачи, но и в момент работы другой прерывающей программы, причем не всякую прерывающую программу допустимо прерывать любым запросом. В фоновой задаче так же могут встречаться участки, при работе которых прерывания (все или некоторые) недопустимы. В общем случае в каждый момент времени работы процессора должно быть выделено подмножество запросов, которым разрешено прерывать текущую программу. В МПС эта задача решается на нескольких уровнях. В процессоре обычно предусматривается программно-доступный флаг разрешения/запрещения прерывания, значение которого определяет возможность или невозможность всех прерываний. Для создания более гибкой системы приоритетов программ на каждом источнике прерываний может быть предусмотрен специальный программно-доступный триггер разрешения формирования запроса. В таком случае возможно формирование произвольного подмножества разрешенных в данный момент источников прерываний. В МП: машинный такт - машинный цикл - командный цикл. Рассмотрим возможность прерывания программы по окончанию различных процессов. Учитывая, что прерванная программа должна быть запущена по окончании работы прерывающей с того места, где она была прервана, подсистема прерываний МПС должна обеспечить фиксацию полного состояния прерываемой программы на момент прерывания. При прерывании после текущего машинного такта требуется запоминать не только состояние всех регистров процессора (программно-доступных и системных), но и состояние первичного управляющего автомата. Реализация процедуры фиксации состояния и последующего восстановления потребует значительных затрат дополнительного оборудования и/или времени. Значительный объем информации требуется запоминать и при прерывании программы после текущего машинного цикла (выбранный фрагмент или всю команду, выбранные операнды или сформированные адреса). Поэтому в большинстве МП прерывание может осуществляться после выполнения очередной команды. Состояние программы в этом случае характеризуется содержимым счетчика команд (адрес следующей команды), а так же содержимым РОН и регистра флагов. Процедура перехода к прерывающей программе и последующего возврата из нее может быть полностью идентична действиям, выполняемым по командам ВЫЗОВ и ВОЗВРАТ. Состояние программного счетчика (а иногда и регистра флагов или PSW) аппаратно фиксируется в стеке, а значение РОНов - при необходимости программно в самом тексте прерывающей программы. Учитывая, что большинство команд МП являются короткими, время реакции МПС на запрос прерывания при анализе запросов по завершению текущего командного цикла не бывает большим.

33 |

Обслуживание внешних устройств методом прямого доступа к памяти |

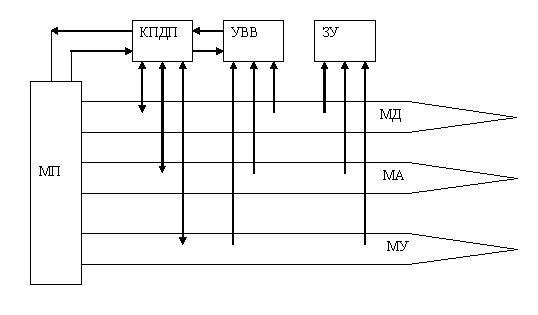

К ПДП

служит для организации обмена данных

между устройствами минуя процессор.

Контроллер используется в МПС если

необходимо переслать большой объем

информации. Его применение увеличивает

быстродействие обмена информации.

Функции КПДП: 1. получение запросов на

режим ПДП от УВВ 2. формирование сигнала

запроса захвата магистрали на входе МП

3. информирование МП о завершении обмена

4. определение приоритета устройств в

случае поступления одновременно

нескольких запросов и информирование

выбранного устройства о начале обмена

5. задания необходимого числа обращений

к устройству. Обмен данными между

устройствами с использованием ПДП:

устройство ввода и память; между памятью

и устройством вывода; между двумя

областями памяти. Принцип работы КПДП.

МП с КПДП взаимодействует при помощи

сигналов запроса захвата магистрали

МП и сигнала подтверждения захвата

магистрали. Получив сигнал запроса от

устройства, КПДП выдает процессору

сигнал запроса захвата. Процессор

заканчивает текущую команду, отключается

от магистралей (Кеш память) и формирует

сигнал подтверждения захвата магистрали.

Получив магистраль, КПДП определяет

устройство, запрос которого имеет

наивысший приоритет и выдает ему сигнал

подтверждающий прием информации от

устройства. За время выдачи этого сигнала

производится одно обращение к магистралям.

КПДП будет повторять обращение до тех

пор, пока устройство не снимет запрос

обмена. КПДП заканчивает обращение,

отключается от магистрали, информирует

об этом МП сигналом запроса захвата и

его снятием. МП подключается к магистралям

и продолжает работу.

ПДП

служит для организации обмена данных

между устройствами минуя процессор.

Контроллер используется в МПС если

необходимо переслать большой объем

информации. Его применение увеличивает

быстродействие обмена информации.

Функции КПДП: 1. получение запросов на

режим ПДП от УВВ 2. формирование сигнала

запроса захвата магистрали на входе МП

3. информирование МП о завершении обмена

4. определение приоритета устройств в

случае поступления одновременно

нескольких запросов и информирование

выбранного устройства о начале обмена

5. задания необходимого числа обращений

к устройству. Обмен данными между

устройствами с использованием ПДП:

устройство ввода и память; между памятью

и устройством вывода; между двумя

областями памяти. Принцип работы КПДП.

МП с КПДП взаимодействует при помощи

сигналов запроса захвата магистрали

МП и сигнала подтверждения захвата

магистрали. Получив сигнал запроса от

устройства, КПДП выдает процессору

сигнал запроса захвата. Процессор

заканчивает текущую команду, отключается

от магистралей (Кеш память) и формирует

сигнал подтверждения захвата магистрали.

Получив магистраль, КПДП определяет

устройство, запрос которого имеет

наивысший приоритет и выдает ему сигнал

подтверждающий прием информации от

устройства. За время выдачи этого сигнала

производится одно обращение к магистралям.

КПДП будет повторять обращение до тех

пор, пока устройство не снимет запрос

обмена. КПДП заканчивает обращение,

отключается от магистрали, информирует

об этом МП сигналом запроса захвата и

его снятием. МП подключается к магистралям

и продолжает работу.

34 |

Адресное пространство памяти 16-и разрядного процессора |

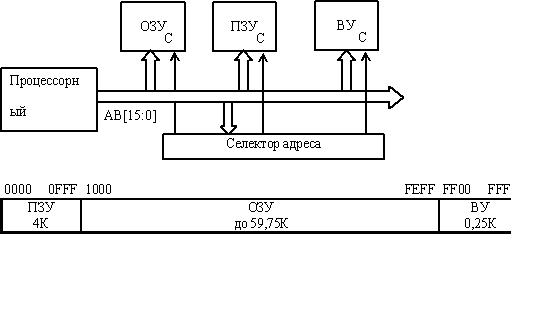

Распределение адресного пространства

О бъем

адресного пространства МПС с интерфейсом

"Общая шина" определяется главным

образом разрядностью шины адреса и,

кроме того, номенклатурой управляющих

сигналов интерфейса. Управляющие сигналы

могут определять тип объекта, к которому

производится обращение (ОЗУ, ВУ, стек,

специализированные ПЗУ и др.). В случае,

если МП не выдает сигналов, идентифицирующих

пассивное устройство (или они не

используются в МПС), - для селекции

используются только адресные линии.

Число адресуемых объектов составляет

в этом случае 2k, где k - разрядность шины

адреса. Будем называть такое адресное

пространство "единым". Иногда

говорят, что ВУ в едином адресном

пространстве "отображены на память",

т.е. адреса ВУ занимают адреса ячеек

памяти. Пример организации селекции

устройств в едином адресном пространстве

МПС на базе i8080 и распределение адресного

пространства показаны на Рис. 7.1 и Рис.

7.2 соответственно. При небольших объемах

памяти в МПС целесообразно использовать

некоторые адресные линии непосредственно

в качестве селектирующих (Рис. 7.3), что

позволяет уменьшить объем оборудования

МПС за счет исключения селектора адреса.

При этом, однако, адресное пространство

используется крайне неэффективно. При

использовании информации о типе

устройства, к которому идет обращение,

можно одни и те же адреса назначать для

разных устройств, осуществляя селекцию

с помощью управляющих сигналов. Так,

большинство МП выдают в той или иной

форме информацию о типе обращения. В

результате в большинстве интерфейсов

присутствуют отдельные управляющие

линии для обращения к памяти и вводу/

выводу, реже - стеку или специализированному

ПЗУ. В результате суммарный объем

адресного пространства МПС может

превышать величину 2k.

бъем

адресного пространства МПС с интерфейсом

"Общая шина" определяется главным

образом разрядностью шины адреса и,

кроме того, номенклатурой управляющих

сигналов интерфейса. Управляющие сигналы

могут определять тип объекта, к которому

производится обращение (ОЗУ, ВУ, стек,

специализированные ПЗУ и др.). В случае,

если МП не выдает сигналов, идентифицирующих

пассивное устройство (или они не

используются в МПС), - для селекции

используются только адресные линии.

Число адресуемых объектов составляет

в этом случае 2k, где k - разрядность шины

адреса. Будем называть такое адресное

пространство "единым". Иногда

говорят, что ВУ в едином адресном

пространстве "отображены на память",

т.е. адреса ВУ занимают адреса ячеек

памяти. Пример организации селекции

устройств в едином адресном пространстве

МПС на базе i8080 и распределение адресного

пространства показаны на Рис. 7.1 и Рис.

7.2 соответственно. При небольших объемах

памяти в МПС целесообразно использовать

некоторые адресные линии непосредственно

в качестве селектирующих (Рис. 7.3), что

позволяет уменьшить объем оборудования

МПС за счет исключения селектора адреса.

При этом, однако, адресное пространство

используется крайне неэффективно. При

использовании информации о типе

устройства, к которому идет обращение,

можно одни и те же адреса назначать для

разных устройств, осуществляя селекцию

с помощью управляющих сигналов. Так,

большинство МП выдают в той или иной

форме информацию о типе обращения. В

результате в большинстве интерфейсов

присутствуют отдельные управляющие

линии для обращения к памяти и вводу/

выводу, реже - стеку или специализированному

ПЗУ. В результате суммарный объем

адресного пространства МПС может

превышать величину 2k.

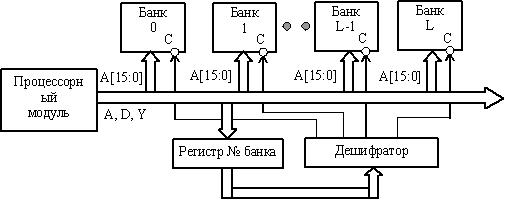

Диспетчер памяти

При необходимости расширить объем

памяти за пределы адресного пространства

можно воспользоваться т.н. "диспетчером

памяти". В простейшем случае он представляет собой

программно-доступный регистр, который

должен располагаться в пространстве

ввода/вывода. В него заносится номер

активного в данный момент банка памяти,

причем объем банка может равняться

объему адресного пространства МП (2k).

Очевидно, в каждый момент времени

процессору доступен только один банк.

При необходимости перехода в другой

банк памяти МП должен предварительно

выполнить программную процедуру (часто

всего одну команду) перезагрузки

содержимого номера банка. Сказанное

иллюстрируется Рис. 7.44. К развитию этой

идеи можно отнести механизм сегментации

памяти в 16- и 32-разрядных МП фирмы INTEL.

простейшем случае он представляет собой

программно-доступный регистр, который

должен располагаться в пространстве

ввода/вывода. В него заносится номер

активного в данный момент банка памяти,

причем объем банка может равняться

объему адресного пространства МП (2k).

Очевидно, в каждый момент времени

процессору доступен только один банк.

При необходимости перехода в другой

банк памяти МП должен предварительно

выполнить программную процедуру (часто

всего одну команду) перезагрузки

содержимого номера банка. Сказанное

иллюстрируется Рис. 7.44. К развитию этой

идеи можно отнести механизм сегментации

памяти в 16- и 32-разрядных МП фирмы INTEL.

Запоминающие устройства

Память может быть внутренней и внешней. Внешней называют память на магнитных, оптических дисках, лентах и т.п. Внутренняя память выполняется, чаще всего, на микросхемах. Внутренняя или основная память может быть двух типов: оперативное запоминающее устройство (ОЗУ) или ЗУ с произвольной выборкой (ЗУПВ) и постоянное ЗУ (ПЗУ). ОЗУ, кроме того, обозначается - (RAM, Random Access Memory), а ПЗУ - (ROM, Read Only Memory). Получила также распространение Флэш(Flash) память, имеющая особенности и ОЗУ и ПЗУ и энергонезависимая память (Nonvolatile - NV) на батарейках. Последнее название условно, так как ПЗУ и Флэш память, также энергонезависимы. В ОЗУ коды в соответствии с решаемыми задачами постоянно изменяются и полностью пропадают при выключении питания. В ПЗУ хранятся управляющие работой ЭВМ стандартные программы, константы, таблицы символов и другая информация, которая сохраняется и при выключении компъютера. ОЗУ подразделяются на статическую память (SRAM), динамическую (DRAM), регистровую (RG). ПЗУ могут быть: масочными - запрограммированными на заводе изготовителе (ROM), однократно-программируемыми пользователем ППЗУ (PROM или OTP), многократно-программируемыми (репрограммируемыми) пользователем РПЗУ с ультрафиолетовым стиранием (EPROM) или c электрическим стиранием (EEPROM). Широкое распространение нашли также программируемые логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т.д.) с большим выбором логических элементов и устройств на одном кристалле. В зависимости от типа ЗУ элементом памяти (ЭП) может быть: триггер, миниатюрный конденсатор, транзистор с "плавающим затвором", плавкая перемычка (или ее отсутствие). Упорядоченный набор ЭП образует ячейку памяти (ЯП) . Количество элементов памяти в ячейке (длина слова) обычно кратно 2n (1,4,8,16, 32,64..), причем величины свыше 8-ми достигаются, обычно, группировкой микросхем с меньшим количеством ЭП. Количество ЭП в ЯП иногда называется длиной слова. Основными характеристиками микросхем памяти являются: информационная емкость, быстродействие и энергопотребление. Емкость ЗУ чаще всего выражается в единицах кратных числу 210 = 1024 = 1K. Для длины слова равной биту (одному двоичному разряду) или байту (набору из восьми бит) эта единица называется килобит или килобайт и обозначается Kb или KB. Каждой из двух в степени "n" ячеек памяти однозначно соответствует "n"- разрядное двоичное число, называемое адресом ЯП. Например, адресом 511-ой ячейки будет число 1 1111 1111(BIN) = 511(DEC) = 1FF(HEX). В программах адреса употребляются в 16-ном формате. Емкость ЗУ часто выражается произведением двух чисел 2n * m, где 2n - число ячеек памяти, а m - длина слова ячейки, например 8K * 8 (м/с 537РУ17), т.е. 8192 ячейки размером в один байт. В некоторых справочниках для этой же микросхемы приводится обозначение емкости одной цифрой 64Kбит, что никак не отражает внутреннюю организацию этой микросхемы, такую же емкость могут иметь м/с с организацией 16K * 4, 64K * 1 и т.д.

35 |

Организация прерываний в 16-разрядном процессоре. |

Контроллер приоритетов прерываний

В нешние

устройства, включенные в подсистему

прерываний, должны реализовать несколько

функций, связанных с работой в этой

подсистеме - формирование запроса,

анализ ответа процессора, выдачу вектора

прерывания. Кроме того, в подсистеме

необходимо обеспечить дисциплину

обслуживания запросов. Перечисленные

функции могут быть реализованы на

специальных устройствах - контроллерах

прерываний, которые выпускаются в виде

БИС в составе многих микропроцессорных

комплектов. Параллельный арбитраж

осуществляется с помощью специального

устройства-арбитра (в этом случае

используется КПП). Основные функции

КПП: 1. получить запросы прерываний от

устройств и сформировать сигнал запроса

прерывания на входе МП. 2. установка и

смена приоритетов при одновременном

поступлении запросов 3. маскирования

запросов по команде процессора 4. сообщить

МП начальный адрес подпрограммы

обслуживания прерываний в соответствии

с тем, какой запрос будет удовлетворен.

Взаимодействие МП с КПП осуществляется

с помощью сигналов запроса прерываний

от КПП и подтверждения прерывания по

МУ. При поступлении запроса прерывания

от УВВ КПП, в случае если запрос не

маскирован, выдает сигнал запроса

прерывания основной программы на МП.

МП завершает выполнение текущей команды,

в стеке запоминается адрес возврата в

подпрограмму. Сигналом подтверждения

прерывания по МУ запрашивается вектор

прерывания от КПП. КПП выставляет на МД

адрес подпрограммы обслуживания

прерывания или вектор прерывания

(информация по которой можно найти адрес

начала подпрограммы обслуживания

устройства). После сообщения МП вектора

прерывания снимается запрос прерывания

от КПП, выполняется подпрограмма

обслуживания, снимается сигнал запроса

от УВВ.

нешние

устройства, включенные в подсистему

прерываний, должны реализовать несколько

функций, связанных с работой в этой

подсистеме - формирование запроса,

анализ ответа процессора, выдачу вектора

прерывания. Кроме того, в подсистеме

необходимо обеспечить дисциплину

обслуживания запросов. Перечисленные

функции могут быть реализованы на

специальных устройствах - контроллерах

прерываний, которые выпускаются в виде

БИС в составе многих микропроцессорных

комплектов. Параллельный арбитраж

осуществляется с помощью специального

устройства-арбитра (в этом случае

используется КПП). Основные функции

КПП: 1. получить запросы прерываний от