- •Системы счисления

- •Комбинационные схемы и цифровые автоматы. Классификация цифровых автоматов

- •Типовые элементы компьютера

- •Виды представления двоичной информации

- •Основные технические характеристики

- •Цифровые автоматы. Триггер

- •Двухступенчатый rs-триггер

- •Регистры

- •Счетчики

- •Комбинационные схемы. Дешифратор

- •Мультиплексор

- •Сумматор

- •Четвертьсумматор

- •Полусумматор

- •Полный сумматор

- •Функциональная схема эвм. Принципы Фон-Неймана

- •Функциональные блоки типовой эвм. Основные характеристики

- •Системная шина

- •Характеристики процессора

- •Режимы процессора

- •Принтеры. Классификация

- •«Архитектура типового микропроцессора»

- •Понятие конвейера и конвейерной обработки.

- •Многомашинные и многопроцессорные вычислительные системы

- •Классификация вычислительных систем

- •Классификация компьютеров. Персональные эвм

- •Классификация компьютеров. Рабочая станция

- •Классификация компьютеров. Серверы

- •Классификация компьютеров. Мейнфреймы (отличия от сервера)

- •Системная магистраль

- •Шина данных, управления, адреса

- •Системные шины. Системные локальные шины. Шины расширений

- •Периферийная шина. Универсальные последовательные периферийные шины

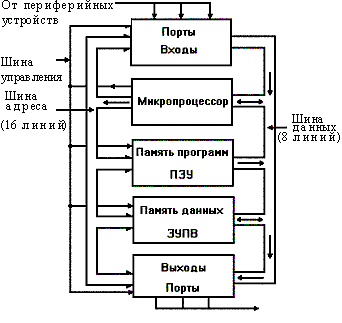

«Архитектура типового микропроцессора»

ЭВМ содержит все 5 основных блоков цифровой машины: устройство ввода информации, управляющее устройство (УУ), арифметико-логическое устройство (АЛУ) (входящие в состав микропроцессора), запоминающие устройства (ЗУ) и устройство вывода информации.

Микропроцессор координирует работу всех устройств цифровой системы с помощью шины управления (ШУ). Помимо ШУ имеется 16-разрядная адресная шина (ША), которая служит для выбора определенной ячейки памяти, порта ввода или порта вывода. По 8-разрядной информационной шине или шине данных (ШД) осуществляется двунаправленная пересылка данных к микропроцессору и от микропроцессора. Важно отметить, что МП может посылать информацию в память ЭВМ или к одному из портов вывода, а также получать информацию из памяти или от одного из портов ввода.

Постоянное запоминающее устройство (ПЗУ) в ЭВМ содержит некоторую программу (на практике программу инициализации ЭВМ). Программы могут быть загружены в запоминающее устройство с произвольной выборкой (ЗУПВ) и из внешнего запоминающего устройства (ВЗУ). Это программы пользователя.

Микропроцессор выполняет следующие функции:

- выборку команд программы из основной памяти;

- дешифрацию команд;

- выполнение арифметических, логических и других операций, закодированных в командах;

- управление пересылкой информации между регистрами и основной памятью, между устройствами ввода/вывода;

- отработку сигналов от устройств ввода/вывода;

- управление и координацию работы основных узлов МП.

Понятие конвейера и конвейерной обработки.

Конвейер — это способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени), технология, используемая при разработке компьютеров и других цифровых электронных устройств.

Идея заключается в разделении обработки компьютерной инструкции на последовательность независимых стадий с сохранением результатов в конце каждой стадии. Это позволяет управляющим цепям процессора получать инструкции со скоростью самой медленной стадии обработки, однако при этом намного быстрее, чем при выполнении эксклюзивной полной обработки каждой инструкции от начала до конца.

Многие современные процессоры управляются тактовым генератором. Процессор внутри состоит из логических элементов и ячеек памяти — триггеров. Когда приходит сигнал от тактового генератора, триггеры приобретают своё новое значение и логике требуется некоторое время для декодирования новых значений. Затем приходит следующий сигнал от тактового генератора, триггеры принимают новые значения, и так далее. Разбивая последовательности логических элементов на более короткие и помещая триггеры между этими короткими последовательностями уменьшают время, необходимое логике для обработки сигналов. В этом случае длительность одного такта процессора может быть соответственно уменьшена.

Например, простейший конвейер RISC-процессоров можно представить пятью стадиями с наборами триггеров между стадиями:

получение инструкции;

декодирование инструкции и чтение регистров;

выполнение;

доступ к памяти;

запись в регистр;

Процессоры с конвейером внутри устроены так, что обработка инструкций разделена на последовательность стадий, предполагая одновременную обработку нескольких инструкций на разных стадиях. Результаты работы каждой из стадий передаются через ячейки памяти на следующую стадию, и так — до тех пор, пока инструкция не будет выполнена. Подобная организация процессора, при некотором увеличении среднего времени выполнения каждой инструкции, тем не менее обеспечивает значительный рост производительности за счёт высокой частоты завершения выполнения инструкций.