- •1)Организация питания эвм. Роль заземления аппаратуры.

- •2)Особенности архитектуры cis, risc микропроцессоров.

- •3)Источники бесперебойного питания. Структурные схемы OnLine и StandBy ups.

- •4)Команды процессора, цикл выполнения команд

- •5)Архитектура компьютера. Основные компоненты эвм - их роль и взаимодействие.

- •6)Организация хранения данных во внешних магнитных дисках

- •7)Электронные компоненты, применяемые в эвм. Триггер. Регистр, мультиплексор, коммутатор, счетчик, сумматор, компаратор.

- •9)Назначение bios. Основные разделы bios.

- •10) Типы файловых систем внешних магнитных дисков. Влияние размера кластера на работу диска.

- •11) Физические принципы записи информации в магнитных дисках. Эффект суперпармагнетизма.

- •12)Устройство ввода информации - мышь. Принципы функционирования.

- •Оптические мыши первого поколения

- •Оптические мыши второго поколения

- •Лазерные мыши

- •Индукционные мыши

- •Инерционные мыши

- •Гироскопические мыши

- •Мыши с mems-датчиками

- •13)Команды эвм. Машинные коды и команды ассемблера. Функциональные группы команд.

- •Достоинства языка ассемблера

- •Недостатки языка ассемблера

- •14) Организация raid массивов. Основная цель организации и способы реализации.

- •15) Электронные компоненты, применяемые в эвм. Триггер. Регистр, мультиплексор, коммутатор, счетчик, сумматор, компаратор.

- •16) Типы файловых систем внешних магнитных дисков

- •17)Стадии выполнения команды с точки зрения взаимодействия процессора и памяти.

- •Конвейерная архитектура

- •Параллельная архитектура

- •18)Интерфейсы рс. Основные группы сигналов и их назначение.

- •19)Динамическая память. Принцип функционирования sdram, ddr sdram, ddr2 sdram. Основные параметры.

- •20) Арбитраж в интерфейсах. Основные типы арбитража и способы выполнения..

- •21) Понятие кэш-памяти. Принцип функционирования.

- •22)Стандарт rs-232. Принцып обмена информацией. Режимы обмена данными.

- •23)Виртуальная память. Принцип работы.

- •24)Параллельный порт рс. Основные регистры. Способ организации обмена информацией.

- •25)Программные и аппаратные прерывания.

- •26)Дисковые накопители. Принцип функционирования. Типы разметки поверхности магнитного диска. Параметры диска.

- •27)Cd-rom. Dvd-rom br диски. Принципы функционирования.

- •28)2D и 3d графические ускорители. Эффекты, реализуемые на аппаратном уровне в 3d графическом процессоре.

- •29)Принцип функционирования crt мониторов. Основные типы, особенности и характеристики. Достоинства и недостатки

- •30)Функционирование компьютера с точки зрения взаимодействия с данными..

- •31)Электронные компоненты, применяемые в эвм. Триггер. Регистр, мультиплексор, коммутатор, счетчик, сумматор, компаратор.

- •32)Звуковые контроллеры. Блок-схема. Принципы функционирования

- •33)Последовательная шина usb. Принципы функционирования.

- •34. Конвейерная архитектура процессора. Принцип функционирования. Факторы снижающие эффективность конвейерной архитектуры.

- •35. Принципы функционирования струйных принтеров.

- •36. Параллельная архитектура

- •37Принципы функционирования лазерных принтеров.

- •38. Суперскалярная архитектура.

- •39. Стандарты mpeg

- •40. Кэш. Цели и задачи. Способы замещения данных.

- •41)Организация кластера эвм. Преимущества кластерной организации многомашинного комплекса

- •42)Триггер. Таблица истинности. Одно и двухпортовая ячейка статической памяти.

- •43. Основные характеристики динамической памяти. Тайминги.

- •44. Принцип функционирования жидкокристаллического монитора. Типы жидкокристаллических мониторов. Особенности и характеристики. Достоинства и недостатки.

- •45. Принцип функционирования плазменного монитора. Особенности и характеристики. Достоинства и недостатки

- •46)Организация хранения данных на магнитных дисках

- •47)Методы повышения надежности магнитных дисков

- •48)Основные особенности системной шины pci. Сравнение с pci-express.

- •49. Организация прерываний.

- •50. Адресация пк в защищенном режиме.

- •51. Архитектура системы команд стекового типа

- •52. Архитектура системы команд аккумуляторного типа

- •53. Архитектура системы команд регистрового типа

- •54. Преобразование логического адреса в физический

- •55. Преобразование логического адреса в линейный

- •56)Режимы работы процессора с архитектурой х86

- •57. Принципы функционирования dlp Проекторов. Преимущества и недостатки.

- •58. Основные этапы развития вычислительной техники

55. Преобразование логического адреса в линейный

Преобразование логического адреса в линейный

Логический адрес состоит из двух элементов: селектор сегмента и относительный адрес (смещение). Селектор сегмента может быть либо непосредственно в коде команды, либо в одном из сегментных регистров. Смещение также может быть либо непосредственно в коде команды, либо вычисляться на основе значений регистров общего назначения.

Для вычисления линейного адреса процессор:

-

использует селектор сегмента для нахождения дескриптора сегмента;

-

анализирует дескриптор сегмента, контролируя права доступа (сегмент доступен с текущего уровня привилегий) и предел сегмента (смещение не превышает предел)

-

добавляет смещение к базовому адресу сегмента и получает линейный адрес.

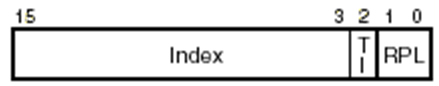

Селектор - это 16-битный идентификатор сегмента.

Он содержит индекс дескриптора в дескрипторной таблице, бит определяющий, к какой дескрипторной таблице производится обращение (LDT или GDT), а также запрашиваемые права доступа к сегменту.

Индекс выбирает один из 8192 дескрипторов в таблице дескрипторов. Процессор умножает значение этого индекса на восемь (длину дескриптора) и добавляет результат к базовому адресу таблицы дескрипторов. Таким образом получается линейный адрес требуемого дескриптора.

TI - индикатор таблицы определяет таблицу дескрипторов, на которую ссылается селектор: TI=0 означает глобальную дескрипторную таблицу (GDT), а TI=1 - используемую в настоящий момент локальную дескрипторную таблицу (LDT).

RPL - запрашиваемый уровень привилегий (Requested Privilege Level). Используется механизмом защиты.

Дескрипторные таблицы - это массивы памяти переменной длины, содержащие восьмибайтные элементы - дескрипторы.

Дескрипторная таблица может иметь длину от 8 байт до 64Кбайт и в каждой таблице может быть до 8192 дескрипторов.

Старшие 13 битов селектора используются как индекс в таблице дескрипторов. Эти таблицы обслуживает ОС, поэтому команды загрузки таблицы являются привилегированными командами.

Существуют две обязательных дескрипторных таблицы - глобальная дескрипторная таблица (Global Descriptor Table - GDT) и дескрипторная таблица прерывания (Interrupt Descriptor Table - IDT),- а также до 8191 локальных дескрипторных таблиц (Local Descriptor Table - LDT), из которых в один момент времени процессору доступна только одна.

Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR. Регистры GDTR и IDTR - 6-байтные, они содержат 32 бита линейного базового адреса дескрипторной таблицы и 16 бит предела таблицы.

Дескриптор - это 8-байтная единица описательной информации, распознаваемая устройством управления памятью в защищенном режиме, хранящаяся в дескрипторной таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел сегмента и права доступа к сегменту.

В защищенном режиме сегменты могут начинаться с любого линейного адреса (который называется базовым адресом сегмента) и иметь любой предел вплоть до 4Гбайт.

------------------------Накрайняк нижеследующее выкинуть нах---------------------

Базовый адрес сегмента (Base Address) определяет место сегмента внутри линейного 4Гбайтного адресного пространства. Процессор объединяет три фрагмента базового адреса для формирования одного 32-разрядного значения.

Предел сегмента (Segment Limit) определяет размер сегмента. Задает максимальное (для сегментов стека - минимальное) смещение в сегменте, обращение по которому не вызывает нарушения общей защиты.

G - бит гранулярности (Granularity) определяет размер единиц, в которых интерпретируется поле предела. Если G=0, то граница интерпретируется в байтах, иначе в единицах по 4Кбайт.

D - размер по умолчанию (Default size). Задает разрядность данных по умолчанию : D=0 - 16 бит, D=1 - 32 бит.

AVL (available) - может использоваться по усмотрению системного программиста.

P - бит присутствия (Present). Если P =0, то данный дескриптор не может быть использован при трансляции адресов.

DPL - уровень привилегий дескриптора (Descriptor Privilege Level) используется механизмом защиты.

S - бит системного дескриптора (System): определяет, является ли данный сегмент системным (S=0) или же сегментом кода/данных (S=1).

Тип дескриптора (Type). Интерпретация этого поля зависит от вида дескриптора.