- •1.Архитектура ядра микроконтроллера aTmega 128.

- •2.Блок предделителя таймеров/счётчиков микроконтроллеров семейства aTmega и принцип его работы.

- •1.Организация памяти в микроконтроллере aTmega 128.

- •2.Работа таймеров/счётчиков т0 (т2) в режиме Normal(Суммирующий счётчик).

- •1.Регистры микроконтроллера aTmega128 используемые при обращении к памяти программ и памяти данных? Их формат.

- •2.Управление размещением таблицы прерываний в микроконтроллерах aTmega64,128.

- •1.Регистровый файл микроконтроллера aTmega128.

- •2.Регистр управления предделителем таймеров/счётчиков и его формат.

2.Блок предделителя таймеров/счётчиков микроконтроллеров семейства aTmega и принцип его работы.

Блоки предделителей предназначены для формирования тактовых сигналов таймеров/счетчиков clkT0, clkT1, clkT2, clkT3. В состав каждого блока входят собственно 10-разрядный предделитель и выходной мультиплексор (селектор тактового сигнала), а для таймеров, имеющих возможность работы в асинхронном режиме, - еще и входной мультиплексор исходного тактового сигнала.

Следует иметь в виду, что все таймеры/счетчики каждой модели семейства, не имеющие асинхронного режима работы, используют один и тот же 10-разрядный предделитель. Соответственно в моделях ATmega64x и ATmegal28x это таймеры/счетчики Tl, T2 и ТЗ' в моделях ATmegal62x - ТО, Tl и ТЗ; в остальных моделях - ТО и Т1. При этом управление тактовым сигналом каждого таймера/счетчика осуществляется индивидуально.

Следует понимать, что предделители работают независимо от таймеров/счетчиков. Следствием этого является, в частности, неопределенный промежуток времени (1..JV+1 тактов исходного сигнала, где TV-коэффициент деления предделителя) между разрешением таймера/счетчика и первым его отсчетом при работе совместно с предделителем.

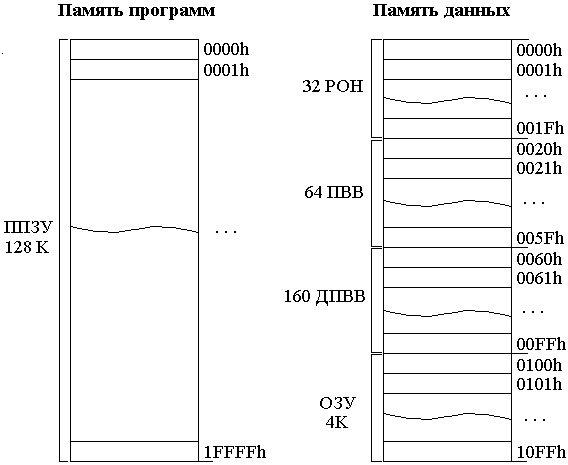

1.Организация памяти в микроконтроллере aTmega 128.

Память программ представляет собой электрически стираемое перепрограммируемое постоянное запоминающее устройство (ППЗУ) объемом 128 Кбайт, выполненное по технологии FLASH-памяти. Данная память предназначена для хранения команд, управляющих функционированием микроконтроллера, а также для хранения констант, не меняющих своих значений в ходе выполнения программы. Так, как длина команды составляет 16 бит, то память программ имеет 16-разрядную организацию. Для адресации памяти программ используется 16-разрядный регистр программный счетчик PС (Program Counter). Программа исполняется последовательно. Для управления ходом выполнения программы существуют команды перехода, изменяющие соответствующим образом значение РС.

Память данных организована по принципу совмещенной архитектуры ввода/вывода и разделена на 3 части: регистровая память; память портов (регистров) ввода/вывода; статическое ОЗУ (SRAM). Все части расположены в едином адресном пространстве. Пространство ввода/вывода состоит из 64 адресов портов 0000h-003Fh, предназначенных для взаимодействия с внутренними и внешними по отношению к микроконтроллеру устройствами. Порты ввода/вывода отображаются на область памяти данных с адресами 0020h-005Fh и допускают возможность обращения к ним как к ячейкам памяти.

2.Работа таймеров/счётчиков т0 (т2) в режиме Normal(Суммирующий счётчик).

Это наиболее простой режим работы таймеров/счетчиков. А в тайме-ре/счетчике ТО моделей ATmega8x и ATmegal63x это вообще единственной режим. В этом режиме счетный регистр функционирует как обычный суммирующий счетчик. По каждому импульсу тактового сигнала clkTO (clkT2) осуществляется инкремент счетного регистра. При переходе через значение $FF возникает переполнение, и счет продолжается со значения $00. В том же такте сигнала clkTO (clkT2), в котором обнуляется регистр TCNTO (TCNT2), устанавливается в «1» флаг переполнения TOV0

(TOV2). В таймерах/счетчиках исполнений 2 и 3 при равенстве счетного регистра и регистра сравнения устанавливается флаг прерывания OCF0 (OCF2) и, если разряд OCIE0 (OCIE2) регистра TIMSKустановлен в «1», генерируется прерывание. Наряду с установкой флага при равенстве счетного регистра и регистра сравнения может изменяться состояние вывода ОС0 (ОС2) микроконтроллера. Каким образом оно будет изменяться, определяется разрядами СОМ01:СОМ00 (СОМ21:СОМ20) регистра TCCRO (TCCR2) При необходимости состояние вывода ОС0 (ОС2) может быть изменено принудительно, записью лог. 1 в разряд FOC0 (FOC2) регистра TCCR0 (TCCR2). Прерывание при этом не генерируется.