- •Раздел 1. Микропроцессорные системы управления.

- •Раздел 2. Микроконтроллерные системы управления.

- •Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

- •1. Микропроцессорные системы управления

- •1.1. Принципы построения и основы работы

- •Вопросы и задания

- •1.2. Элементная база мпсу

- •Вопросы и задания

- •1.3. Оперативные запоминающие устройства.

- •Вопросы и задания

- •1.4. Постоянные запоминающие устройства.

- •Вопросы и задания

- •1.5. Архитектура микропроцессора типа кр580вм80

- •Вопросы и задания

- •1.6. Типы машинных циклов и слово состояния

- •Вопросы и задания

- •1.7. Командные циклы чтения/записи

- •Вопросы и задания

- •1.8. Командный цикл подтверждения прерывания.

- •1.9. Принципиальные электрические схемы

- •Вопросы и задания

- •1.10. Интерфейс мпсу с изолированной системой шин

- •Вопросы и задания

- •1.11. Интерфейс мпсу с общей системой шин

- •1.12. Организация обслуживания запросов прерывания

- •Вопросы и задания

- •1.13. Программируемый контроллер

- •Вопросы и задания

- •1.14. Программируемый контроллер прерываний

- •Вопросы и задания

- •1.15. Программируемый интервальный таймер

- •Вопросы и задания

- •1.16. Мпсу с вводом-выводом аналоговой информации

- •Вопросы и задания

- •1.17. Выходные каскады мпсу

- •Вопросы и задания

- •2. Микроконтроллерные системы управления

- •2.1. Архитектура микроконтроллера к1816ве51

- •Вопросы и задания

- •2.2. Принципиальная электрическая схема порта

- •2.3. Схемы подключения внешней памяти к мк51

- •Вопросы и задания

- •2.4. Интерфейс мк51 с большим числом

- •Вопросы и задания

- •2.5. Таймер/счетчики мк51.

- •Вопросы и задания

- •2.6. Система прерываний мк51. Использование прерываний в программах

- •Вопросы и задания

- •2.7. Основы организации

- •Допустимые различия скорости приемо-передачи

- •2.8. Организация мультиконтроллерных систем

- •Программы инициализации станции и абонентов

- •Программы станции и абонента в сеансе "станция→абонент"

- •2.9. Микроконтроллерная система управления

- •3. Вопросы эксплуатации микропроцессорных устройств

- •3.1. Отладка аппаратных средств мпсу

- •Вопросы и задания

- •3.2. Отладка программного обеспечения мпсу

- •Вопросы и задания

- •3.3. Методы обеспечения помехоустойчивости мпсу

- •Вопросы и задания

- •1. Группа команд пересылок

- •2. Группа команд инкремента-декремента

- •3. Группа арифметических команд

- •4. Группа логических команд

- •5. Группа команд сдвига

- •6. Группа команд передачи управления

- •7. Группа команд работы со стеком

- •8. Группа команд ввода-вывода и управления микропроцессором

- •1. Группа команд пересылок

- •2. Группа команд арифметических операций

- •3. Группа команд логических операций

- •4. Группа команд операций с битами

- •5. Группа команд передачи управления

- •Дворак Николай Маркович микропроцессорные устройства

- •В высших учебных заведениях 3-4 уровней

- •98309, Г. Керчь, ул. Орджоникидзе, 82

- •98309, Г. Керчь, ул. Орджоникидзе, 82

МИНИСТЕРСТВО АГРАРНОЙ ПОЛИТИКИ УКРАИНЫ

КЕРЧЕНСКИЙ ГОСУДАРСТВЕННЫЙ

МОРСКОЙ ТЕХНОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ

МИКРОПРОЦЕССОРНЫЕ

УСТРОЙСТВА

УЧЕБНОЕ ПОСОБИЕ

Допущено

Министерством аграрной политики Украины как

учебное пособие для подготовки специалистов

по специальности 7.092201 "Электрические

системы и комплексы транспортных средств"

в высших учебных заведениях 3-4 уровней

аккредитации Минагрополитики Украины

Керчь

2006

УДК 681.322:681.58

Рецензенты:

доктор технических наук, профессор В.М. Захарченко

(Одесская национальная морская академия)

кандидат технических наук, доцент А.А. Катюха

(Таврическая государственная агротехническая академия)

Дворак Н.М.

Микропроцессорные устройства: Учебное пособие. - Керчь: Издательский центр КГМТУ, 2006. – 151 с.

Табл.. 8. Ил.. 134

Курс лекций предназначен для студентов направления "Электромеханика" по специальности 7.092201 "Электрические системы и комплексы транспортных средств" по специализации 7.092201.02 "Эксплуатация судовых автоматизированных систем".

В лекциях рассмотрены вопросы построения и эксплуатации микропроцессорных систем управления на основе микропроцессорного комплекта КР580 и микроконтроллера К1816ВЕ51.

Материал лекций может быть использоваться как студентами, которые получают базовое образование по указанной специальности, так и слушателями отделения переподготовки ФПК, которые получают новую специальность, а также судовыми электриками и электромеханиками.

ISBN 966-580-130-9

Дворак Н.М., 2006

Керченский государственный морской технологический университет, 2006

СОДЕРЖАНИЕ

Введение 4

1. МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ УПРАВЛЕНИЯ 5

1.1. Принципы построения и основы работы микропроцессорных систем управления 5

1.2. Элементная база МПСУ 7

1.3. Оперативные запоминающие устройства. Блоки оперативной памяти 13

1.4. Постоянные запоминающие устройства. ПЗУ с раздельными и совмещенными шинами 18

1.5. Архитектура микропроцессора КР580ВМ80 21

1.6. Типы машинных циклов и слово состояния микропроцессора КР580ВМ80 25

1.7. Командные циклы чтения/записи запоминающих и внешних устройств 28

1.8. Командный цикл подтверждения прерывания. Выполнение команды RST 34

1.9. Принципиальные электрические схемы формирования шин МПСУ 38

1.10. Интерфейс МПСУ с изолированной системой шин 40

1.11. Интерфейс МПСУ с общей системой шин 47

1.12. Организация обслуживания запросов прерывания с использованием команды RST 50

1.13. Программируемый контроллер параллельного интерфейса 54

1.14. Программируемый контроллер прерываний 58

1.15. Программируемый интервальный таймер 67

1.16. МПСУ с вводом/выводом аналоговой информации 73

1.17. Выходные каскады МПСУ 77

2. МИКРОКОНТРОЛЛЕРНЫЕ СИСТЕМЫ УПРАВЛЕНИЯ 80

2.1. Архитектура микроконтроллера К1816ВЕ51 (МК51). Организация памяти МК51 80

2.2. Принципиальная электрическая схема порта ввода-вывода МК51. Организация вывода и ввода информации битами и байтами 85

2.3. Схемы подключения внешней памяти к МК51 92

2.4. Интерфейс МК51 с большим числом внешних устройств 96

2.5. Таймер/счетчики МК51. Реализация выдержек времени 99

2.6. Система прерываний МК51. Использование прерываний в программах 104

2.7. Основы организации последовательного интерфейса 107

2.8. Организация мультиконтроллерных систем 113

2.9. Микроконтроллерная система управления грузовым лифтом 118

3. ВОПРОСЫ ЭКСПЛУАТАЦИИ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ 122

3.1. Отладка аппаратных средств МПСУ 122

3.2. Отладка программного обеспечения МПСУ 125

3.3. Методы обеспечения помехоустойчивости МПСУ 129

ПРИЛОЖЕНИЯ 134

А. Команды микропроцессора КР580ВМ80 134

Б. Команды микроконтроллера К1816ВЕ51 143

ЛИТЕРАТУРА 149

ПРЕДМЕТНЫЙ УКАЗАТЕЛЬ 150

Введение

Автоматика современных судов базируется преимущественно на микропроцессорных средствах. Дешевизна, надежность, многоканальность и практически неограниченные возможности в реализации алгоритмов управления являются решающими аргументами в пользу выбора микропроцессорных систем автоматического управления. Теоретические разработки в области автоматического управления, считавшиеся сложными во внедрении из-за несовершенства элементной базы систем автоматики, легко и просто реализуются на базе микропроцессоров.

Принципы построения и работа микропроцессорных систем управления (МПСУ) коренным образом отличаются от всех иных существующих систем управления. Работу МПСУ определяет не столько принципиальная электрическая схема, сколько ее программное обеспечение. В МПСУ аппаратная и программные части связаны органично, друг без друга они бесполезны. Эта особенность чрезвычайно усложняет диагностику, поиск неисправностей и техническое обслуживание МПСУ.

В обязанности судовых электромехаников входит техническое обслуживание и ремонт устройств МПСУ. Целью настоящего учебного пособия является изучение основ построения и работы МПСУ в том объеме, чтобы специалист-электромеханик был в состоянии читать принципиальные электрические схемы и программы микропроцессорных устройств, и на такой основе – грамотно эксплуатировать МПСУ.

Учебное пособие включает:

Раздел 1. Микропроцессорные системы управления.

Раздел 2. Микроконтроллерные системы управления.

Раздел 3. Вопросы эксплуатации микропроцессорных устройств.

Примеры, рассмотренные в данном учебном пособии, охватывают основные приемы построения схем микропроцессорных устройств и их программирования.

1. Микропроцессорные системы управления

1.1. Принципы построения и основы работы

микропроцессорных систем управления

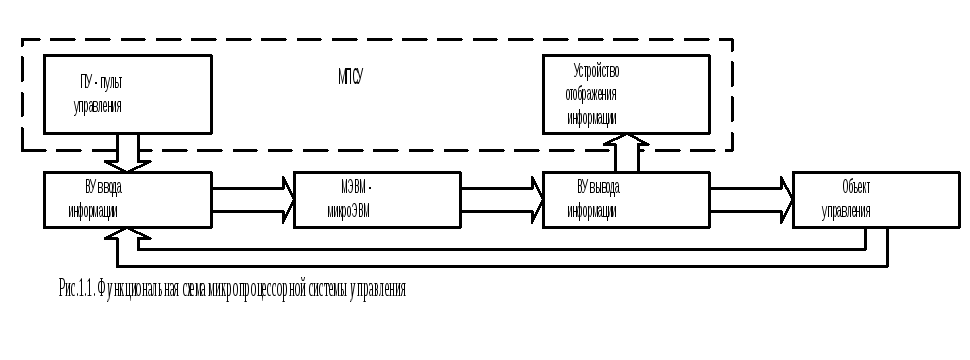

М ПСУ

представляет собой комплекс технических

и программных средств, осуществляющих

ввод информации о состоянии управляемого

объекта, обработку информации и вывод

управляющих сигналов на объект управления.

Функциональная схема МПСУ приведена

на рис.1.1, где ВУ – внешние устройства.

ПСУ

представляет собой комплекс технических

и программных средств, осуществляющих

ввод информации о состоянии управляемого

объекта, обработку информации и вывод

управляющих сигналов на объект управления.

Функциональная схема МПСУ приведена

на рис.1.1, где ВУ – внешние устройства.

Я дром

МПСУ является МЭВМ. Минимальная

конфигурация МЭВМ содержит микропроцессор

(МП) и устройства памяти (рис.1.2). Память

подразделяется на постоянную (ПЗУ) и

оперативную (ОЗУ). В ячейках ПЗУ хранятся

в виде двоичных кодов команды программы

работы МПСУ. МП выполняет эти команды.

ПЗУ является обязательным элементом

МПСУ. Промежуточные результаты выполнения

команд сохраняются во внутренних

регистрах МП. Большие объемы информации

результатов выполнения команд сохраняются

в ОЗУ.

дром

МПСУ является МЭВМ. Минимальная

конфигурация МЭВМ содержит микропроцессор

(МП) и устройства памяти (рис.1.2). Память

подразделяется на постоянную (ПЗУ) и

оперативную (ОЗУ). В ячейках ПЗУ хранятся

в виде двоичных кодов команды программы

работы МПСУ. МП выполняет эти команды.

ПЗУ является обязательным элементом

МПСУ. Промежуточные результаты выполнения

команд сохраняются во внутренних

регистрах МП. Большие объемы информации

результатов выполнения команд сохраняются

в ОЗУ.

Работа МП состоит в последовательном выполнении команд, считанных из ПЗУ (рис.1.3). Структурно команда состоит из кода операции (КОП) и операндов.

КОП является обязательной частью команды, и он определяет содержание действий в процессе выполнения команды и также указывает на наличие операндов. Операнд является необязательной частью команды. Количество операндов (0, 1 или 2) в команде определяется КОП. Операнд содержат информацию, уточняющую действия в процессе выполнении команды:

- адреса ячеек памяти и ВУ, из которых читается информация (в цикле чтения) или в которые записывается информация (в цикле записи);

- числовые константы;

- проверяемые условия;

- адреса переходов и др.

Операнды, относящиеся к выполняемой команде, располагаются по адресам ячеек ПЗУ сразу за ячейкой с КОП.

Некоторые команды не содержат операндов.

Естественное выполнение команд – последовательное. Однако возможны безусловные и условные переходы, например, как показано на рис.1.3, после выполнения команды №2 следующей выполняется команда № N.

В сигнальном представлении КОП и операнды

абсолютно неразличимы. Любой код,

например, 7F, может быть

либо КОП, либо операндом. Однозначность

трактовки кодов и, следовательно,

правильность выполнения команд программы,

записанной в ПЗУ, достигается благодаря

применению начальной установки и сброса

МП. После прохождения начальной установки

или сброса во всех типах МП начинает

исполняться команда, которая расположена

по нулевому адресу ПЗУ, причем всегда

первым считанным кодом будет только

КОП. Это, так называемый, аппаратный

пуск программы МПСУ. Начальная установка

происходит в момент включения питания

процессора. Сброс осуществляется

нажатием на кнопку "Сброс", которая

имеется в схемах всех МПСУ.

сигнальном представлении КОП и операнды

абсолютно неразличимы. Любой код,

например, 7F, может быть

либо КОП, либо операндом. Однозначность

трактовки кодов и, следовательно,

правильность выполнения команд программы,

записанной в ПЗУ, достигается благодаря

применению начальной установки и сброса

МП. После прохождения начальной установки

или сброса во всех типах МП начинает

исполняться команда, которая расположена

по нулевому адресу ПЗУ, причем всегда

первым считанным кодом будет только

КОП. Это, так называемый, аппаратный

пуск программы МПСУ. Начальная установка

происходит в момент включения питания

процессора. Сброс осуществляется

нажатием на кнопку "Сброс", которая

имеется в схемах всех МПСУ.

Дальше команды исполняются в соответствии с их содержанием и расположением в ПЗУ. Сначала исполнится команда, считанная с нулевого адреса ПЗУ. Затем выполняется следующая команда, КОП которой содержится по адресу сразу за 2-м операндом предыдущей команды (рис.1.3) и т.д.

С труктурно

МПСУ имеют шинную (магистральную)

организацию связей МП с памятью и ВУ

(рис.1.4).

труктурно

МПСУ имеют шинную (магистральную)

организацию связей МП с памятью и ВУ

(рис.1.4).

Шина представляет собой совокупность физических проводников, объединенных по функциональной идентичности сигналов, передаваемых по проводникам. В МПСУ ШД имеет обычно 8 проводников (1 байт), ША – 8 или 16 проводников (1 байт и 1 слово), размерность ШУ составляет 2-5 проводников.

Шинная организация позволяет строить МПСУ по модульному принципу, в соответствии с которым возможно подключение стандартным способом, видным из рис.1.4, произвольного числа блоков памяти и ВУ.

Между

МП и блоками памяти и ВУ по ШД происходит

обмен данными D. Связь МП

с конкретным устройством устанавливается

с использованием адресной информации

А, передаваемой по ША. По отношению к

устройствам адресная информация

структурно состоит из двух частей:

адреса устройств и адреса ячейки памяти

внутри этих устройств. Адрес устройства

формируется дешифратором ДШ. Выбранное

устройство активизируется сигналом

![]() (Chip Select –

выбор кристалла чипа), в результате чего

это устройство выходит на связь с МП.

Все остальные устройства неактивны и

связи с МП не поддерживают. В МПСУ

активный уровень сигнала выбора кристалла

(Chip Select –

выбор кристалла чипа), в результате чего

это устройство выходит на связь с МП.

Все остальные устройства неактивны и

связи с МП не поддерживают. В МПСУ

активный уровень сигнала выбора кристалла

![]() стандартизирован и равен 0. Управляющая

информация, поступающая с ШУ, определяет

направление передачи информации между

МП и устройствами, выбирает для связи

либо блоки памяти, либо ВУ, подтверждает

прерывания и др.

стандартизирован и равен 0. Управляющая

информация, поступающая с ШУ, определяет

направление передачи информации между

МП и устройствами, выбирает для связи

либо блоки памяти, либо ВУ, подтверждает

прерывания и др.

МП имеет также входы управляющих сигналов, назначение и количество которых зависит от типа МП. Стандартными управляющими входными сигналами МП являются сигналы сброса, запроса прерывания, захвата шин, остановки. ВУ активно используют вход запроса прерывания.

В режиме вывода информации из МП к ШД может быть подключено любое число блоков памяти и ВУ.

В режиме ввода информации в МП к ШД может быть подключено только один из блоков памяти или одно ВУ. Если этого не выполнить, то принимаемая МП информация будет неправильной, а одновременно подключенные к ШД блоки памяти и ВУ выйдут из строя.