- •Арифметические и логические основы вычислительной техники учебное пособие

- •Введение

- •Арифметические основы вычислительной техники Системы счисления

- •Двоичная система счисления

- •Восьмеричная система счисления

- •Шестнадцатеричная система счисления

- •Критерии выбора системы счисления

- •Перевод чисел из одной системы счисления в другую

- •Перевод целых чисел.

- •Перевод правильных дробей.

- •Перевод чисел из системы счисления в систему счисления основания которых кратны степени 2

- •Кодирование чисел

- •Переполнение разрядной сетки

- •Модифицированные коды

- •Машинные формы представления чисел.

- •Погрешность выполнения арифметических операций

- •Округление

- •Нормализация чисел

- •Последовательное и параллельное сложение чисел

- •Сложение чисел с плавающей запятой

- •Машинные методы умножения чисел в прямых кодах

- •Ускорение операции умножения

- •Умножение с хранением переносов

- •Умножение на два разряда множителя одновременно.

- •Умножение на четыре разряда одновременно.

- •Умножение в дополнительных кодах.

- •Умножение на 2 разряда Мт в дополнительных кодах.

- •Матричные методы умножения.

- •Машинные методы деления

- •Деление чисел в прямых кодах.

- •Деление чисел в дополнительных кодах.

- •Методы ускорения деления.

- •Двоично-десятичные коды

- •Суммирование чисел с одинаковыми знаками в коде 8421.

- •Сложение чисел с разными знаками.

- •Двоично-десятичные коды с избытком 3

- •Код с избытком 6 для одного из слагаемых

- •Система счисления в остаточных классах (сок)

- •Представление отрицательных чисел в сок

- •Контроль работы цифрового автомата

- •Некоторые понятия теории кодирования

- •Обнаружение и исправление одиночных ошибок путем использования дополнительных разрядов

- •Коды Хемминга

- •Логические основы вычислительной техники Двоичные переменные и булевы функции

- •Способы задания булевых функций

- •Основные понятия алгебры логики

- •Основные законы алгебры логики

- •Формы представления функций алгебры логики

- •Системы функций алгебры логики

- •Минимизация фал

- •Метод Квайна

- •Метод Блейка - Порецкого

- •Метод минимизирующих карт Карно (Вейча)

- •Минимизация коньюнктивных нормальных форм.

- •Минимизация не полностью определенных фал

- •Кубическое задание функций алгебры логики.

- •Метод Квайна-Мак Класки

- •Алгоритм извлечения (Рота)

- •Минимизация фал методом преобразования логических выражений

- •Применение правил и законов алгебры логики к синтезу некоторых цифровых устройств Синтез одноразрядного полного комбинационного сумматора

- •Синтез одноразрядного комбинационного полусумматора

- •Синтез одноразрядного полного комбинационного сумматора на двух полусумматорах

- •Синтез одноразрядного комбинационного вычитателя

- •Объединенная схема одноразрядного комбинационного сумматора-вычитателя

- •Триггер со счетным входом как полный одноразрядный сумматор

- •Введение в теорию конечных автоматов Основные понятия теории автоматов

- •Способы задания автоматов

- •Структурный автомат

- •Память автомата

- •Канонический метод синтеза

- •Пример синтеза мпа Мили по гса

- •Синхронизация автоматов

- •Литература

- •220013, Минск, п.Бровки, 6.

Минимизация фал методом преобразования логических выражений

Рассмотрим подход к упрощению ФАЛ заключающийся в применении к ней скобочных преобразований. Пусть имеется функция

f=x1x3x4x6+x2x3x4x6 + x5x6 + x7

Применим к ней скобочные преобразования, в результате чего получим функцию f=((x1+x2)x3x4 + x5)x6 + x7.

Из выражений видно, что цена схемы до минимизации была равна 14, после стала равна 11. Таким образом общая стоимость схемы сократилась , однако функции до преобразования соответствовала схема имеющая два уровня элементов, а после 5 уровней. Таким образом, полученная схема будет работать примерно в 2,5 раза медленнее исходной (до преобразования).

Применение правил и законов алгебры логики к синтезу некоторых цифровых устройств Синтез одноразрядного полного комбинационного сумматора

Пусть имеется два числа

A=a1a2 . . . a i-1a ia i+1 . . . an

B=b1b2 . . . b i-1bib i+1 . . . bn

В зависимости от значений аргументов ai, bi, zi формируется значение булевых функций Ci, и Пi. Введем следующие обозначения.

ai x Ci С

bi y Пi П

zi z

Таблица истинности, отражающая алгоритм работы сумматора, имеет следующий вид.

Таблица 23.

|

|

x |

y |

z |

С |

П |

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

0 |

0 |

1 |

1 |

0 |

|

|

|

0 |

1 |

0 |

1 |

0 |

|

|

|

0 |

1 |

1 |

0 |

1 |

|

|

|

1 |

0 |

0 |

1 |

0 |

|

|

|

1 |

0 |

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

0 |

1 |

|

|

|

1 |

1 |

1 |

1 |

1 |

|

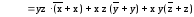

Запись одной функции с участием другой носит название совместной минимизации. С учетом этого функция C будет иметь вид

.

.

Таким образом, логическая схема синтезированного одноразрядного полного комбинационного сумматора имеет вид (рис. 30):

& 1 1 & & 1 & & x

y z 1 П С Рис. 30.

Логическая схема полного сумматора.

Синтез одноразрядного комбинационного полусумматора

Одноразрядный полусумматор это устройство для сложения разрядов двух чисел без учета переноса из предыдущего разряда и имееющее два входа (два суммируемые разряды) и два выхода (суммы и переноса).

Таблица истинности, отражающая алгоритм работы полусумматора, имеет следующий вид.

Таблица 24.

|

|

x |

y |

C |

П |

|

|

|

0 |

0 |

0 |

0 |

|

|

|

0 |

1 |

1 |

0 |

|

|

x y

П

C

а) |

1 |

0 |

1 |

0 |

Логическая схема, соответствующая записанной |

|

|

1 |

1 |

0 |

1 |

системе булевых функций, имеет вид (рис.31а): |

Данная схема может быть упрощена, если функция C будет записана на нулевых наборах и использована совместная минимизация.

Рис. 31. Логическая схема полусумматора

до и после упрощения

Логические нули

Логические нули