- •2.1. Микросхема имс (fpga) xc3s200, используемая в обучающей программе.

- •1) Starting the ise Software (начало работы с программой ise):

- •Verifying Functionality using Behavioral Simulation (верификация функциональности за счет использования моделирования поведения (работы).

- •Implement Design and Verify Constraints (реализация разработки и верификация ограничений).

- •Implementing the Design (реализация разработки).

- •By Frédéric Rivoallon, Xilinx, Inc.

- •Glue logic

Verifying Functionality using Behavioral Simulation (верификация функциональности за счет использования моделирования поведения (работы).

Create a test bench waveform containing input stimulus you can use to verify the functionality of the counter module. The test bench waveform is a graphical view of a test bench (создайте временную диаграмму (прохождения сигналов) на испытательном стенде, которая содержит входной сигнал, который Вы можете использовать для проверки функциональности модуля счетчика).

Create the test bench waveform as follows (порядок создания временной диаграммы):

1. Select the counter HDL file in the Sources window (выбрать файл counter HDL в окне Sources – Документы);

2. Create a new test bench source by selecting Project → New Source (создайте источник временной диаграммы выбрав пиктограммы Project → New Source);

3. In the New Source Wizard, select Test Bench WaveForm as the source type, and type

counter_tbw in the File Name field (в окне New Source Wizard – чародей нового документа, выберите Test Bench WaveForm временную испытательную диаграмму в качестве типа документа, и напечатайте counter_tbw в поле File Name – новое имя);

4. Click Next (щелкните по пиктограмме следующий);

5. The Associated Source page shows that you are associating the test bench waveform with the source file counter. Click Next (страница Associated Source – связанный документ покажет, что Вы связали временную испытательную диаграмму с файлом документа счетчика. Щелкните по пиктограмме следующий);

6. The Summary page shows that the source will be added to the project, and it displays the source directory, type and name. Click Finish (итоговая страница покажет, что документ будет добавлен к проекту и при этом отобразится директория документа, его тип и имя. Щелкните по пиктограмме конец);

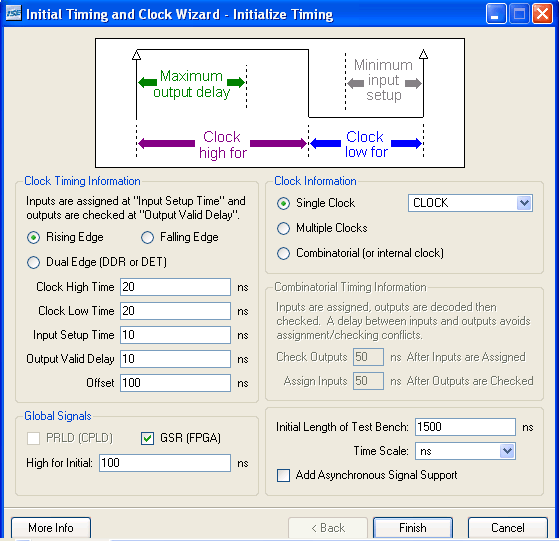

7. You need to set the clock frequency, setup time and output delay times in the Initialize Timing dialog box before the test bench waveform editing window opens (Вам необходимо установить значение частоты тактовых импульсов, время подготовки к работе и времена задержки выходных сигналов до того, как откроется окно редактирования временной испытательной диаграммы);

The requirements for this design are the following (требования к данной разработке следующие):

♦ The counter must operate correctly with an input clock frequency = 25 MHz (счетчик может работать правильно при частоте входных тактовых импульсов = 25 MHz);

♦ The DIRECTION input will be valid 10 ns before the rising edge of CLOCK (вход DIRECTION - Направление будет действителен в течение 10 нс до нарастающего фронта тактовых импульсов);

♦ The output (COUNT_OUT) must be valid 10 ns after the rising edge of CLOCK (выход счетчика COUNT_OUT должен быть действительным в течение 10 нс после нарастающего фронта тактовых импульсов);

The design requirements correspond with the values below (требования к разработке соответствуют нижеуказанным значениям).

Fill in the fields in the Initialize Timing dialog box with the following information (заполните поля в диалоговом окне Initialize Timing – инициализация временной диаграммы):

♦ Clock High Time: 20 ns (верхний уровень генератора тактовых импульсов – 20 нс);

♦ Clock Low Time: 20 ns (нижний уровень генератора тактовых импульсов – 20 нс);

♦ Input Setup Time: 10 ns (время подготовки к работе -10 нс);

♦ Output Valid Delay: 10 ns (действительное время задержки выходного сигнала - 10 нс);

♦ Offset: 0 ns (параметр смещения – 0 нс);

♦ Global Signals: GSR (FPGA) (наличие глобальных сигналов для моделирования FPGA - enable the simulation of the global signals for Global Set/Reset (GSR) – параметр GSR (FPGA).

Note: When GSR(FPGA) is enabled, 100 ns. is added to the Offset value automatically (Примечание: в случае включения параметра GSR (FPGA) автоматически добавляется временной интервал в 100 нс для параметра смещения).

♦ Initial Length of Test Bench: 1500 ns (начальная длина испытательной временной последовательности – 1500 нс);

Leave the default values in the remaining fields (оставьте значения переменных по умолчанию в оставшихся полях).

8. Click Finish to complete the timing initialization (щелкните по пиктограмме Окончание для завершения процесса временной инициализации);

9. The blue shaded areas that precede the rising edge of the CLOCK correspond to the Input Setup Time in the Initialize Timing dialog box. Toggle the DIRECTION port to define the input stimulus for the counter design as follows (зона с голубым оттенком, которая предшествует нарастающему фронту тактовых импульсов, соответствует опции Input Setup Time – время подготовки к работе входа в диалоговом окне Initialize Timing - инициализация временной диаграммы. Переключите порт DIRECTION (направление) для определения входного стимулирующего воздействия для разрабатываемого счетчика как показано ниже):

♦ Click on the blue cell at approximately the 300 ns to assert DIRECTION high so that the counter will count up (щелкните по голубой ячейке при временном интервале примерно в 300 нс для объявления величины DIRECTION (направление) достаточно большой, чтобы счетчик считал в направлении нарастания счетной последовательности);

♦ Click on the blue cell at approximately the 900 ns to assert DIRECTION low so that the counter will count down (щелкните по голубой ячейке при временном интервале примерно в 900 нс для объявления величины DIRECTION (направление) достаточно малой, чтобы счетчик считал в направлении убывания счетной последовательности);

Figure 7: Initialize Timing (инициализация временной диаграммы).

Note: For more accurate alignment, you can use the Zoom In and Zoom Out toolbar buttons (примечание: для более точной настройки Вы можете использовать опции Zoom In (давать изображение крупным планом) и Zoom Out (давать изображение мелким планом).

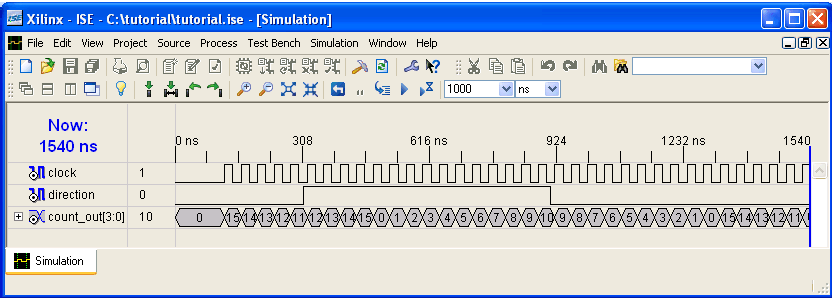

Figure 8: Test Bench Waveform (испытательная временная диаграмма)

10. Save the waveform (сохраните испытательную временную диаграмму);

11. In the Sources window, select the Behavioral Simulation view to see that the test bench waveform file is automatically added to your project (в окне Sources (документы) выбрать ниспадающее меню Behavioral Simulation (моделирование поведения) для того, чтобы убедиться в том, что файл испытательной временной диаграммы автоматически добавлен к Вашему проекту).

Figure 9: Behavior Simulation Selection (выбор опции моделирования поведения)

12. Close the test bench waveform (закройте испытательную временную диаграмму).

Simulating Design Functionality (моделирование функциональности разрабатываемого счетчика).

Verify that the counter design functions as you expect by performing behavior simulation as follows (убедитесь в том, что функции разрабатываемого счетчика согласно Ваших ожиданий выполняют операции поведенческого моделирования):

1. Verify that Behavioral Simulation and counter_tbw are selected in the Sources window (убедитесь, что опции Behavioral Simulation (моделирование поведения) и counter_tbw);

2. In the Processes tab, click the “+” to expand the Xilinx ISE Simulator process and double-click the Simulate Behavioral Model process (в таблице Processes (процессы) щелкните по знаку “+”для расширения рамок процесса моделирования (Xilinx ISE Simulator process) и дважды щелкните по пиктограмме Simulate Behavioral Model (моделирование процессов поведенческой модели);

The ISE Simulator opens and runs the simulation to the end of the test bench (откроется окно Xilinx ISE [Simulation] и произойдет прогонка моделирующего процесса до конца заданного Вами временного интервала испытаний);

3. To view your simulation results, select the Simulation tab and zoom in on the transitions.

The simulation waveform results will look like the following (для просмотра результатов моделирования выберите опцию Simulation tab (моделирование) и дайте изображение переходных процессов крупным планом):

Figure 10: Simulation Results (результаты моделирования).

Note: You can ignore any rows that start with TX (примечание: Вы можете игнорировать любые ряды, начинающиеся с TX (передача)).

4. Verify that the counter is counting up and down as expected (убедитесь в том, что счетчик считает в двух направлениях (увеличение и уменьшение счетной последовательности) как ожидалось);

5. Close the simulation view. If you are prompted with the following message, “You have an active simulation open. Are you sure you want to close it?“, click Yes to continue (закройте пиктограмму обзора моделирования (View). Если Вы получите подсказку в виде следующего сообщения “You have an active simulation open. Are you sure you want to close it?“ – У вас открыт процесс активного моделирования. Вы уверены, что Вам не хочется закрыть его?. Щелкните по пиктограмме Yes (да) для продолжения).

You have now completed simulation of your design using the ISE Simulator.

Таким образом Вы теперь завершили моделирование Вашей разработки с использованием моделирующей программы ISE Simulator.

Create Timing Constraints (создание временных ограничений).

Specify the timing between the FPGA and its surrounding logic as well as the frequency the design must operate at internal to the FPGA. The timing is specified by entering constraints that guide the placement and routing of the design. It is recommended that you enter global constraints. The clock period constraint specifies the clock frequency at which your design must operate inside the FPGA. The offset constraints specify when to expect valid data at the FPGA inputs and when valid data will be available at the FPGA outputs.

Определите временные параметры, связывающие FPGA (матричная БИС FPGA) и окружающие ее логические элементы, а также частоту, при которой разрабатываемый счетчик должен работать внутри FPGA. Временные интервалы определяются за счет ввода ограничений, которые управляют размещением и маршрутизацией разрабатываемой ИМС. Рекомендуется, чтобы Вы ввели глобальные ограничения. Ограничение периода тактовых импульсов определяет тактовую частоту, при которой Ваша разработка должна работать внутри ИМС FPGA. Ограничение смещения определяет, когда следует ожидать действительных данных на входе ИМС FPGA и когда действительные данные появятся выходе ИМС FPGA.

Entering Timing Constraints (ввод временных ограничений).

To constrain the design do the following (предлагается следующая процедура ввода ограничений):

1. Select Synthesis/Implementation from the drop-down list in the Sources window (выберите опцию Synthesis/Implementation (синтез/реализация) из ниспадающего меню в окне Sources (документы);

2. Select the counter HDL source file (выберите документ counter HDL (счетчик HDL);

3. Click the “+” sign next to the User Constraints processes group, and double-click the and double-click the Create Timing Constraints process (щелкните по знаку “+” рядом с опцией User Constraints processes group (ограничения пользователя) и дважды щелкните по опции Create Timing Constraints (создание временных ограничений).

ISE runs the Synthesis and Translate steps and automatically creates a User

Constraints File (UCF). You will be prompted with the following message (Моделирующая программа ISE запускает этапы Synthesis (синтез) и Translate (перевод) и автоматически создает User Constraints File (UCF) – файл ограничений пользователя:

Figure 11: Prompt to Add UCF File to Project (подсказка о добавлении файла UCF к Вашему проекту).

4. Click Yes to add the UCF file to your project (щелкните по пиктограмме Да и добавьте файл ограничений пользователя к Вашему проекту);

The counter.ucf file is added to your project and is visible in the Sources window (файл counter.ucf добавляется к Вашему проекту и появляется в окне Sources (документы).

The Xilinx Constraints Editor opens automatically (редактор ограничений Xilinx открывается автоматически).

Note: You can also create a UCF file for your project by selecting Project → Create New

Source (примечание: Вы можете также создать файл UCF (ограничений пользователя) в Вашем проекте путем выбора опции Project → Create New Source (проект – создание нового документа);

In the next step, enter values in the fields associated with CLOCK in the Constraints Editor Global tab (на следующем этапе введите в поля, связанные с тактовым генератором (CLOCK) в таблице Constraints Editor Global tab (глобальные ограничения редактирования).

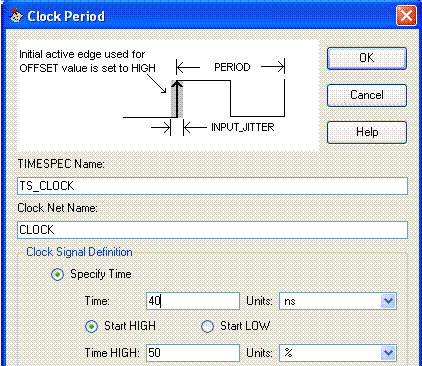

5. Select CLOCK in the Clock Net Name field, then select the Period toolbar button or double-click the empty Period field to display the Clock Period dialog box (выберите опцию CLOCK (тактовый генератор) в поле Clock Net Name (имя тактового генератора), затем выберите пиктограмму Period (период) на инструментальной линейке или дважды щелкните по пустому полю пиктограммы Period (период) для отображения диалогового окна Clock Period (период тактового генератора);

6. Enter 40 ns in the Time field (введите 40 нс в поле опции Time (время);

Figure 12: Clock Period (период тактового генератора).

7. Click OK (щелкните по пиктограмме ОК);

8. Select the Pad to Setup toolbar button or double-click the empty Pad to Setup field to

display the Pad to Setup dialog box (выберите окно Pad to Setup (панель установки) или дважды щелкните по пустому полю Pad to Setup (панель установки) для отображения диалогового окна Pad to Setup (панель установки);

9. Enter 10 ns in the OFFSET field to set the input offset constraint (введите 10 нс в поле OFFSET (смещение) для установки ограничений по смещению);

Figure 13: Pad to Setup (панель установки).

10. Click OK (щелкните ОК);

11. Select the Clock to Pad toolbar button or double-click the empty Clock to Pad field to display the Clock to Pad dialog box (выберите панель установки Clock to Pad или дважды щелкните по пустому полю Pad to Setup (панель установки) для отображения диалогового окна Clock to Pad (панель тактового генератора);

12. Enter 10 ns in the OFFSET field to set the output delay constraint (введите 10 нс в поле OFFSET (смещение) для установки ограничений по смещению);

Figure 14: Clock to Pad (панель тактового генератора).

13. Click OK (щелкнуть по пиктограмме ОК);

The constraints are displayed in the Constraints (read-write) tab, as shown below (ограничения отображаются в таблице Constraints (ограничения):

Figure 15: Timing Constraints (временные ограничения).

14. Save the timing constraints. If you are prompted to rerun the TRANSLATE or XST step, click OK to continue (сохраните временные ограничения. Если Вы получите подсказку по повторному запуску этапов TRANSLATE (перевод) или XST, щелкните по пиктограмме ОК для продолжения);

15. Close the Constraints Editor (закройте редактор ограничений).