- •2.1. Микросхема имс (fpga) xc3s200, используемая в обучающей программе.

- •1) Starting the ise Software (начало работы с программой ise):

- •Verifying Functionality using Behavioral Simulation (верификация функциональности за счет использования моделирования поведения (работы).

- •Implement Design and Verify Constraints (реализация разработки и верификация ограничений).

- •Implementing the Design (реализация разработки).

- •By Frédéric Rivoallon, Xilinx, Inc.

- •Glue logic

Lecture 16

FPGA Synthesis (синтез ПЛИС)

1 The general approach to a problem of programming Xilinx FPGA devices (общий подход к проблеме программирования ПЛИС, производимые фирмой Xilinx).

With embedded systems becoming more popular, many designers want to reduce their

component count and increase flexibility. To accomplish both of these goals, a microprocessor

already available in the system can be used to configure an FPGA. This application note

provides a thorough discussion of FPGA configuration via a microprocessor, covering

Virtex® and Spartan® FPGA families. Also, this application note presents a system-level model

using a Xilinx® Complex Programmable Logic Device (CPLD) to implement an interface to the

FPGA configuration pins. C code is included to illustrate an example application using either

Slave Serial or SelectMAP mode. CPLD design files are also included to illustrate a possible

synchronous interface between the processor and the FPGA.

Поскольку встроенные [встраиваемые] системы становятся все более популярными, поэтому многие разработчики хотят сократить свои расходы на их создание и повысить их гибкость. Для решения этой задачи можно использовать, например, схему программирования на основе микропроцессора.

Примечание: embedded system - встроенная [встраиваемая] система - компьютерная система, работающая совместно с другим оборудованием и размещаемая с ним либо в одном конструктивном блоке, либо внутри данного оборудования.

This section discusses a reference design allowing a microprocessor to configure an FPGA

device via the SelectMAP mode (SelectMAP configuration mode is the fastest configuration

option). In order to accomplish SelectMAP configuration, this design uses a combination of a

microprocessor, CPLD, and flash memory (Figure 1).

Для программирования ПЛИС предлагается комбинация микропроцессора, блока CPLD (Complex Programmable Logic Device - сложное устройство с программируемой логикой (технология, разработанная фирмой Xilinx) и блока флэш-памяти.

Figure 1: SelectMAP Configuration

A 16-bit wide flash memory device is used to store the FPGA configuration data. Because each

flash address stores 16-bits of data, the microprocessor reads each address to retrieve the 16-bit

wide data and delivers the data in a byte-wide fashion to the FPGA. During this process, the

microprocessor provides the FPGA with a configuration clock and monitors the DONE and BUSY pins. A CPLD is used to form the glue logic between the microprocessor and the FPGA device.

В данной схеме блок 16-битовой флэш-памяти используется для хранения данных конфигурации ПЛИС. Поскольку каждый адрес во флэш-памяти хранит 16-битовые данные, микропроцессор производит считывание каждого адреса для извлечения 16-битовых данных и отправляет данные в байтах в ПЛИС. В течение этого процесса микропроцессор обеспечивает ПЛИС тактовым генератором для процесса конфигурации и производит мониторинг штырьков DONE (выполнено) и BUSY (занято). Блок CPLD используется для образования т.н. схем «клейкой логики» (glue logic – простые схемы для соединения сложных логических схем) между микропроцессором и ПЛИС.

Примечание: CPLD (Complex Programmable Logic Device) - сложное устройство с программируемой логикой - технология, разработанная фирмой Xilinx.

CoolRunner CPLD

A Xilinx CoolRunner CPLD is used for glue logic between the microprocessor and the Xilinx

Virtex FPGA. In the SelectMAP configuration mode, the CoolRunner device is responsible for

driving the Virtex FPGA configuration pins, namely PROGRAM, CS, WRITE, CCLK, and

D[0:7]. The Virtex FPGA’s INIT, DONE, and BUSY pins are also registered by the CPLD,

allowing the status of these pins to be monitored by the microprocessor.

Блок CoolRunner CPLD используется для создания схемы «клейкой логики» между микропроцессором и ПЛИС Xilinx Virtex FPGA. Состояние штырьков конфигурации этого блока отслеживается микропроцессором.

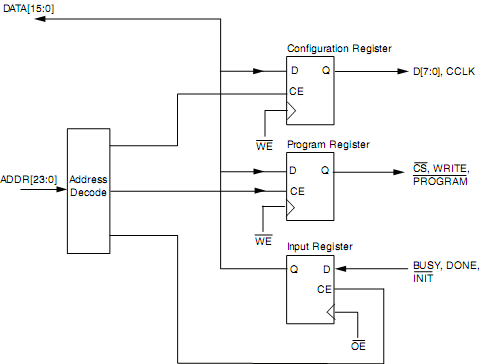

Figure 2: CPLD Block Diagram (структурная схема блока CPLD).

The CoolRunner CPLD is used to establish a synchronous interface between the

microprocessor and the Xilinx FPGA. This interface is comprised of three registers: the

Configuration Register, Program Register, and Input Register. These registers store FPGA

configuration signals each time the processor does a read or write to the port, supporting the

set of signals required for SelectMAP mode (PROGRAM, CCLK, DATA[0:7], INIT, CS, WRITE, DONE, and BUSY). The Configuration Register and Program Register are write-only registers, while the Input Register is read-only.

Блок CoolRunner CPLD используется для создания синхронного интерфейса между микропроцессором и ПЛИС Xilinx Virtex FPGA.

Этот интерфейс образован 3 регистрами: Регистр конфигурации, Программный регистр и Входной регистр. Эти регистры хранят сигналы конфигурации ПЛИС каждый раз, когда процессор выполняет процедуру чтения или записи в порт, поддерживая набор сигналов, необходимых для режима SelectMAP (PROGRAM, CCLK (тактовый генератор конфигурации), DATA[0:7], INIT (инициализации), CS (выбор кристалла), WRITE (запись), DONE (выполнено), и BUSY (занято).

Регистр конфигурации и Программный

регистр – регистры только для записи

(сигнал

![]() -

разрешение записи, Входной регистр –

только для чтения.

-

разрешение записи, Входной регистр –

только для чтения.

A detailed block diagram of the CPLD is shown in Figure 7.

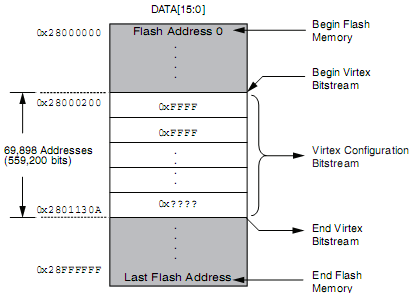

Figure 3: Flash Memory Map (карта памяти флэш-памяти).

Flash Memory (блок флэш-памяти).

In this design, the 16-bit-wide flash memory begins at address 0x28000000 and ends at

address 0x28FFFFFF. As shown in Figure 5, a Virtex XCV50 configuration bitstream consists

of 559,200 bits. Because each address location contains 16 bits of data, a total of 34,950

addresses are needed. The first 16 bits of configuration data reside at address 0x28000200

and the final 16 bits are located at address 0x2801130A. This design arbitrarily chose address

0x28000200 to be the starting address in order to simulate actual customer scenarios in which

flash memory is also used to hold other system data.

В данной схеме 16-битовая флэш-память начинается с адреса 0x28000000 и заканчивается по адресу 0x28FFFFFF. В приведенной схеме битовый поток данных конфигурации включает 559 200 бит. Поскольку каждый адрес памяти содержит 16 бит данных, всего получается 34 950 адресов. Первые 16 бит данных конфигурации находятся по адресу 0x28000200, а последние 16 бит расположены по адресу 0x2801130A. В данной схеме случайно выбранный адрес является стартовым с целью побудить пользователей использовать флэш-память для хранения других данных.

The data within the flash memory might need to be byte-swapped, depending upon the

application. For this design, byte-swapped data is used for SelectMAP configuration but not for

Slave-Serial configuration. Byte-swapping reformats the FPGA configuration data so that the

order of the bits within each byte is reversed.

Данные, хранящиеся во флэш-памяти, могут подвергнуться процедуре обмена одного байта на другой в зависимости от приложения. Эта процедура производит реформацию данных конфигурации ПЛИС, в результате которой порядок битов в каждом байте реверсирован.

Примечание: byte swapping – процедура обмена байтов необходима, например, когда двоичный файл, созданный Операционной Системой DOS/WIndows необходимо прочитать в ЭВМ, которая имеет другой порядок размещения своих байтов.

2. Содержание этапов процесса разработки ПЛИС.

ISE 9.1i Quick Start Tutorial (обучающая программа для ускоренного освоения процесса разработки ПЛИС с использованием демонстрационной платы Spartan™-3 Demo Board).

2.1. Микросхема имс (fpga) xc3s200, используемая в обучающей программе.

Field programmable gate array (FPGA) - программируемая пользователем вентильная матрица, вентильная матрица с эксплуатационным программированием, матричная БИС FPGA.

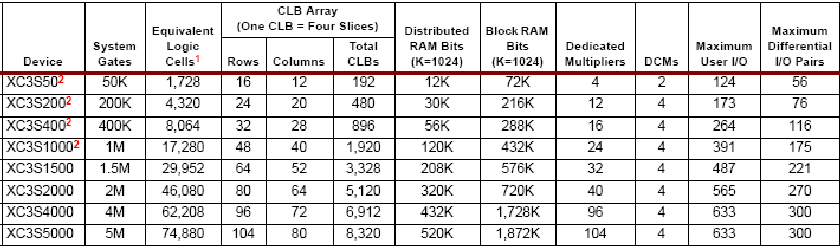

The Spartan®-3 family of Field-Programmable Gate Arrays is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The eight-member family offers densities ranging from 50,000 to five million system gates, as shown in Table 1.

Семейство матричных БИС FPGA Spartan®-3 специально предназначено для удовлетворения необходимости в получении экономичных электронных приложений с большой степенью интеграции.

Table 1: Summary of Spartan-3 FPGA Attributes

Микросхема XC3S200 имеет в своем составе свыше 200 000 системных логических элементов, 4 320 эквивалентных логических ячеек (один массив включает 24х20=480 конфигурируемых логических блоков), распределенное ОЗУ имеет 30х1024 бит памяти, блочное ОЗУ имеет 216х1024 бит, количество выделенных блоком умножения – 12, 4 блока управления тактовыми генераторами, 173 штырька ввода/вывода.

Самая мощная матричная БИС FPGA данного семейства (XC3S5000) имеет в своем составе 5 млн. системных логических элементов.

• Configurable Logic Blocks (CLBs) contain RAM-based Look-Up Tables (LUTs) to implement logic and storage elements that can be used as flip-flops or latches. CLBs can be programmed to perform a wide variety of logical functions as well as to store data (конфигурируемые Конфигурируемые логические блоки (CLB) содержат таблицы поиска (таблицы преобразования; справочные таблицы; таблицы соответствия), построенные на основе элементов памяти ОЗУ для организации комбинационных логических устройств и элементов памяти, которые в свою очередь могут использоваться в качестве триггеров или логических защелок.

Конфигурируемые логические блоки (CLB) можно запрограммировать для выполнения широкой номенклатуры логических функций, а также для хранения данных.

Latches are used as simple memory elements. A latch has many useful applications. They are often used to hold small values for an indefinite amount of time. The simplest latch is most likely the NAND latch. This consists of two NAND gates connected such that the output of one goes to the other's input. In this configuration, there are 2 inputs and one output. One of the inputs is called the SET input, and the other input is called RESET.

Регистр-фиксатор (регистр-защёлка; триггер-фиксатор) используется в качестве простого элемента памяти. Они имеют много применений. Их часто используют для хранения небольших величин в течение неопределенного времени. Простейшим триггер-фиксатор можно построить на основе элементов «И-НЕ».

• Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation.

Twenty-six different signal standards, including eight high-performance differential standards, are available as shown in Table 2. These early interfaces primarily used low voltage differential signaling (LVDS) and various protocols, such as FlatLink and OpenLDI. They typically supported several pixel depths and either four or five differential pairs were used. LVDS interfaces were subsequently employed between a PC and an external monitor where dual-link interfaces were used to support the need for higher resolutions.

Since then, there has been a shift away from LVDS toward the Digital Visual Interface (DVI) standard that is now common on PCs and most commercial electronics, such as TVs. DVI can drive higher resolutions and larger displays than is possible with LVDS. The DVI standard

itself has evolved into the High Definition Multimedia Interface (HDMI) standard to support both the audio and video components for high-definition TV (HDTV).

HDMI utilizes smaller connectors than DVI while maintaining DVI electrical compatibility.

High-Speed Differential Signaling and PMCs

The next step beyond DVI is the use of digital interface standards, such as that developed by the Society of Motion Picture and Television Engineers (SMPTE), SMPTE-292M. This standard defines the method for transmission of HDTV formats, both interlaced and progressive, over a high-speed serial interface. It is now commonly used in television broadcast centers.

Double Data-Rate (DDR) registers are included. The Digitally Controlled

Impedance (DCI) feature provides automatic on-chip terminations, simplifying board designs.

Double data rate (DDR) transmission is used in many applications where fast data transmission is needed, such as memory access and first-in first-out (FIFO) memory structures. DDR uses both edges of a clock to transmit data, which facilitates data transmission at twice the rate of a

single data rate (SDR) architecture using the same clock speed. This method also reduces the number of I/O pins required to transmit data.

Блоки ввода/вывода (IOB) управляют потоком данных между штырьками ввода/вывода и внутренними логическими блоками. Каждый блок ввода/вывода (IOB) поддерживает двунаправленный поток данных + операции с 3-мя состояниями.

В настоящее время используются 26 различных стандартов для передаваемых сигналов, включая 8 дифференциальных стандартов с высоким разрешением (имеется в виду переход от стандарта LVDS (low voltage differential signalling – низковольтный дифференциальный стандарт для сигналов) к DVI (цифровой видео-интерфейс - Digital Visual Interface) и HDTV (high-definition TV – стандарту для телевидения с высоким разрешением).

Double data rate (DDR) transmission is used in many applications where fast data transmission is needed, such as memory access and first-in first-out (FIFO) memory structures. DDR uses both edges of a clock to transmit data, which facilitates data transmission at twice the rate of a

single data rate (SDR) architecture using the same clock speed. This method also reduces the number of I/O pins required to transmit data.

Передача сигналов с использованием архитектуры DDR (Double data rate transmission – передача сигналов с удвоенной скоростью) используется во многих приложениях, в которых требуется высокая скорость передачи сигналов и структура памяти по принципу

FIFO (first in – first out - "первым поступил - первым выводится" (тип очереди, простая очередь). Способ передачи DDR использует оба края тактовых импульсов для передачи данных, что обеспечивает удвоение скорости передачи по сравнению со способом передачи данных, основанном на архитектуре SDR (однократной скорости передачи сигналов при той же скорости передачи тактовых импульсов. Данный способ передачи также сокращает число штырей ввода/вывода, необходимых для передачи данных.

• Block RAM provides data storage in the form of 18-Kbit dual-port blocks (блоки ОЗУ обеспечивают хранение данных в форме 18-килобитных блоков с двойными портами).

• Multiplier blocks accept two 18-bit binary numbers as inputs and calculate the product (блоки умножителей принимают два 18-битных двоичных числа в качестве входных сигналов и вычисляют произведение).

• Digital Clock Manager (DCM) blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase shifting clock signals (блоки управления тактовыми генераторами (DCM) обеспечивают самокалибровку, полностью оцифрованные решения для распределения, задержку, деление и фазовый сдвиг тактовых импульсов).

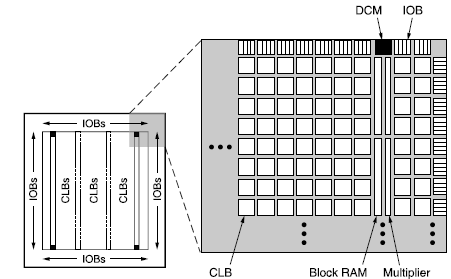

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. The XC3S50 has a single column of block RAM embedded in the array.

Those devices ranging from the XC3S200 to the XC3S2000 have two columns of block RAM. The XC3S4000 and XC3S5000 devices have four RAM columns. Each column is made up of several 18-Kbit RAM blocks; each block is associated with a dedicated multiplier. The DCMs are positioned at the ends of the outer block RAM columns.

The Spartan-3 family features a rich network of traces and switches that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

Эти элементы показаны на Рис.4. Кольцо блоков ввода/вывода IOB окружено регулярной матрицей из конфигурируемых логических блоков (CLB). Изделие XC3S50 имеет одну колонну из блоков ОЗУ, встроенных в матрицу.

В изделиях от XC3S200 до XC3S2000 имеется две колонки из блоков ОЗУ.

Изделия XC3S4000 и XC3S5000 имеют 4 колонки из блоков ОЗУ.

Каждая колонка состоит из нескольких 18-килобитных блоков ОЗУ; каждый блок связан с выделенным умножителем. Блоки DCM расположены на концах наружных блоков колонок ОЗУ.

ИС семейства Spartan-3 имеют развитую сеть из трассировок и переключателей, которые связывают все пять функциональных элементов, и передают сигналы между ними. Каждый функциональный элемент имеет связанную с ним коммутационную [переключательную] матрицу (матричный переключатель), который обеспечивает многочисленные соединения при маршрутизации.

з

з

Figure 4: Spartan-3 Family Architecture (архитектура семейства БМК (FPGA) Spartan-3).

Условные обозначения:

CLB – конфигурируемый логический блок;

DCM – блоки управления тактовыми генераторами;

IOB – блоки ввода/вывода;

Block RAM – блоки ОЗУ;

Multiplier – блок умножения.

2.2. This tutorial contains the following sections (данная обучающая программа использует следующие этапы):

• “Getting Started” (начало работы);

• “Create a New Project” (создание нового проекта);

• “Create an HDL Source” (создание программы с помощью языка описания аппаратных средств);

• “Design Simulation” (моделирование процесса разработки);

• “Create Timing Constraints” (создание временных ограничений);

• “Implement Design and Verify Constraints” (реализация ограничений по конструкции и процесса верификации проекта);

• “Reimplement Design and Verify Pin Locations” (повторная реализация размещения штырьков основных блоков ПЛИС и проверки его функционирования);

• “Download Design to the Spartan™-3 Demo Board” (загрузка разработанной программы проекта ПЛИС в демонстрационную плату Spartan™-3 Demo Board).

2.2.1. “Getting Started” (начало работы);