2.3 Вибір додаткових елементів схеми

Для того, щоб реалізувати в мікроконтролері обробку переривань від зовнішніх пристроїв, застосуємо програмований контролер переривань КР580ВН59А. ВІС ПКП виконує такі функції:

-

запам’ятовує запити переривання, які задаються переднім фронтом або

потенціалом;

-

маскує, тобто забороняє виконання обраних запитів;

-

формує вектор переривання та виконує дії по переходу на підпрограму

обробки запиту;

-

формує сигнал переривання для МП;

-

виконує пріоритетну обробку запитів переривання.

Велика інтегральна схема КР580ВН59А може виробляти код команди 8-розрядного МП і8085 CALL ADRV, де ADRV – адреса підпрограми обробки.

Одна ВІС ПКП обробляє вісім запитів на переривання, але за каскадного вмикання кількох ВІС кількість запитів переривання може бути збільшена до 64.

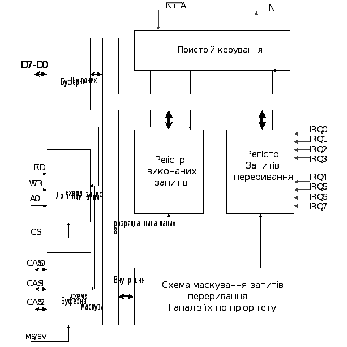

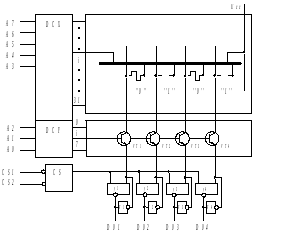

Структурну схему ВІС ПКП КР580ВН59А наведено на рисунку 2.4

Рис. 2.4 Структурна схема КР580ВН59А.

Програмований паралельний інтерфейс (ППІ) КР580ВВ55 призначений для введення-виведення паралельної інформації у 8-байтовому форматі, що дозволяє реалізувати більшість відомих протоколів обміну по паралельних каналах. ВІС ППІ може використовуватись для з’єднання МП зі стандартним периферійним устаткуванням (дисплеєм, телетайпом, накопичувачем, тощо). Структурну схему ВІС КР580ВВ55 показано на рисунку 2.5

Рис. 2.5 Структурна схема ВІС КР580ВВ55.

До складу ВІС входять:

-

блок керування читанням/записом ReadlWrite Control Unit (RWCU), що забезпечує керування зовнішнім і внутрішнім передаванням даних і керувальних слів;

-

двонапрямлений 8-розрядний буфер даних Bufer of Data(BD), що з’єднує лінії даних ВІС із системною шиною даних;

-

три 8-розрядні порти введення-виведення (Port A, Port B, Port C) для обміну інформацією, при чому порт С поділений на два 4-розрядні: С’ (PC7-PC4) і C”(PC3-PC0). Порти А і С’ об’єднані у групу А, порти В і C” – у групу В.

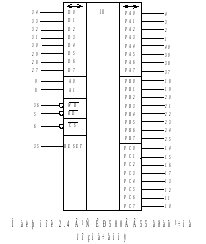

Рис. 2.6 Графічне позначення ВІС КР580ВВ55.

Схема ВІС містить також блоки керування групою А Control Unit A (CUA) та групою B (CUB), що формують сигнали керування для відповідних груп.

Блок RWCU містить регістр керувального слова, який зберігає керувальні слова, що надходять від МП.

Призначення виводів ВІС КР580ВВ55:

-

D7-D0 – вхід/вихід даних;

-

RD – читання: L-рівень сигналу дозволяє зчитування інформації з регістра, що адресується розрядам А0, А1 на лінії D7-D0;

-

WR – запис: L-рівень сигналу дозволяє запис інформації із шини D7-D0 у порт паралельного інтерфейсу, що адресується розрядам А0, А1;

-

А0, А1 – входи для адресування внутрішніх регістрів ППІ;

-

RESET – скидання: Н-рівень сигналу скидає регістр керувального слова і встановлює всі порти в режим уведення;

-

СS – вхід вибірки мікросхеми: L-рівень сигналу з’єднує шину даних D7- D0 ВІС із системною шиною;

-

РА7-РА0 – вхід/вихід порту А;

-

РВ7-РВ0 – вхід/вихід порту В;

-

РС7-РС0 – вхід/вихід порту С;

-

Ucc – вивід напруги живлення +5 В;

-

GND – спільний вивід 0 В.

Програмований послідовний інтерфейс КР580ВВ51 являє собою універсальний синхронно-асинхронний приймач-передавач (УСАПП), призначений для організації обміну між МП і зовнішніми пристроями в послідовному форматі. Він приймає дані з 8-розрядної шини даних МП і передає їх у послідовному форматі периферійному пристрою або одержує послідовні дані від периферійного пристрою і перетворює їх у паралельну форму для передачі до МП. Обмін може бути як напівдуплексним (однонапрямленим), так і дуплексним (двонапрямленим). Послідовний інтерфейс може здійснювати обмін даними в асинхронному режимі зі швидкістю передачі до 9,6 кбіт/с або в синхронному – зі швидкістю до 56 кбіт/с залежно від запрограмованого режиму. Довжина переданих даних – від 5 до 8 біт. При передачі в МП символів завдовжки менше 8 біт невикористані біти заповнюються нулями. Формат символу містить також службові біти і необов’язковий біт контролю парності.

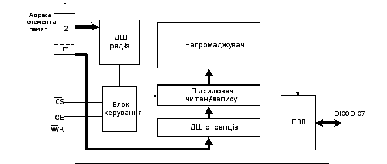

Структурна схема УСАПП (рисунок 2.7) містить:

-

буфер передавача TBF зі схемою керування передавачем TCU, який призначено для приймання даних від МП і видачі їх у послідовному форматі на вихід TxD;

-

буфер приймача RBF зі схемою керування приймачем RCU, що виконує приймання послідовних даних із входу RxD і передачу їх у МП у паралельному форматі;

-

буфер даних BD, яки являє собою паралельний 8-розрядний двонапрямлений буфер шини даних із тристабільними каскадами, який використовується для обміну даними та керувальними словами між МП і УСАПП;

-

блок керування читанням/записом RWCU, що приймає керувальні сигнали від МП і генерує внутрішні сигнали керування;

-

блок керування модемом MCU, який обробляє керувальні сигнали, призначені для зовнішнього пристрою.

Рис. 2.7 Структурна схема ВІС КР580ВВ51

Призначення виводів ВІС КР580ВВ51:

-

D7-D0 – канал даних;

-

RESET – встановлення нуля (вихідний стан);

-

CLK – синхронізація;

-

А0 – адресація: L-рівень визначає можливість запису або читання даних в/із УСАПП, Н-рівень визначає можливість запису керувальних слів або читання стану слова в (із) УСАПП;

-

RD – читання: дозвіл виведення даних або стану слова з УСАПП на шину даних;

-

WR – запис: дозвіл уведення інформації із шини даних;

-

CS – вибірка кристала з’єднання УСАПП із шинами даних МП;

-

DSR – готовність передавача термінала;

-

DTR – запит передавача термінала;

-

CTS – готовність приймача термінала;

-

RTS – запит приймача термінала;

-

SYNDET – вид синхронізації: для синхронного режиму вихідний сигнал високого рівня – ознака внутрішньої синхронізації, для синхронного режиму із зовнішньою синхронізацією сигнал є вхідним, в асинхронному режимі сигнал є вихідним;

-

RxC – синхронізація приймача;

-

RxRDY – готовність приймача;

-

RxD – вхід приймача;

-

ТхС – синхронізація передавача;

-

ТхЕ – кінець передачі;

-

ТхRDY – готовність передавача;

-

ТxD – вихід передавача;

-

Ucc – напруга живлення +5 В;

-

GND – спільний вивід 0 В.

Для побудови ОЗП ми взяли мікросхему К537, з організацією 2Кx8. Мікросхеми цієї серії представляють з себе ОЗП статичного типу, тобто кожний елемент пам'яті виконаний на тригерах. Для зберігання інформації в тригері потрібне джерело живлення, тобто тригер розглянутого типу енергетично залежний. За наявності живлення тригер здатний зберігати свій стан як завгодно довго. В один із двох станів, в який може перебувати тригер, його приводять сигнали, що надходять по лініях шини даних у режимі запису. В мікросхемах даного типу може бути передбачено додаткове джерело живлення для забезпечення автономної роботи блоку пам'яті при випадковому відключенні живлення.

Розрізняють ОЗП з однорозрядною та багаторозрядною організацією.

Щоб

ввести інформацію в ОЗП, використовують

вхід DI (Data Input), а для виведення - вихід

DO (Data Output) і вихідний підсилювач. Вхідний

та вихідний підсилювачі можна виконати

як один підсилювач читання/запису.

Керують режимами (запису, зчитування,

зберігання) за допомогою сигналів CS і

W/R. Одиничний стан сигналу W/R визначає

режим запису біта інформації в елемент

пам’яті, а нульовий – режим зчитування

біта інформації з елемента пам’яті.

Роботу

мікросхеми статичного ОЗП в динамічному

режимі ілюструють часові діаграми,

показані на рисунку 2.9, які відображують

послідовність подачі адресних і

керувальних сигналів під час запису і

зчитування, а також часові інтервали

між різними сигналами і тривалостями

сигналів: час циклу запису/зчитування

(tц.зп/зч),

тривалість сигналів CS (вибору мікросхеми)

τвм і

паузи між ними τвм,

час установлення сигналу CS щодо адреси

tус.вм.а,

час збереження адреси після сигналу CS

tзб.а.вм,

час вибірки адреси tв.а

чи час вибору мікросхеми tв.вм.

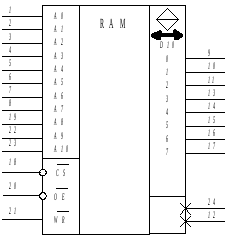

Великі інтегральні схеми ОЗП з багаторозрядною організацією 2mx n мають n інформаційних входів/виходів DIOn-1-DIO0. Структурну схему ВІС ОЗП статичного типу з інформаційною ємністю 2mx8 показано на рис.2.8 Вона має 8 входів/виходів даних DIO7-DIO0. Такий ОЗП припускає читання/запис 8-розрядного коду. Для запису нуля або одиниці, що надходять на входи DIO7-DIO0, потрібно на адресні входи подати код адреси Аm-1-А0, а на входи блоку керування сигнал дозволу CS та сигнал W/R. Зчитування інформації відбувається аналогічно, але значення сигналу W/R протилежне.

Рис. 2.8 Структурна схема ВІС ОЗП статичного типу

Рис. 2.9 Часові діаграми мікросхеми статичного ОЗП.

У більшості мікросхем ОЗП статичного типу підсилювач введення/виведеня містить ключовий підсилювач-формувач, що може перебувати у трьох станах, два з яких відповідають нулеві або одиниці, а третій – високоімпедансний (z-стан). У z-стані не відбувається обміну інформацією з ОЗП. Перехід у z-стан визначається сигналом ОЕ.

Рис 2.10 Графічне позначення ВІС ОЗП К537.

Графічне позначення схеми статичної мікросхеми ОЗП типу К537 наведено на рисунку 2.10

Для побудови ПЗП ми беремо дві мікросхеми одноразово програмованої ПЗП (ППЗП або PROM – Programmed Read Only Memory) типу КР556РТ(РТ15) з організацією 2Кx4. Мікросхеми цього типу використовують для зберігання налагоджених програм МПС керування різноманітного призначення. Вони допускають програмування на місці їх застосування користувачем. Програмування або занесення інформації в одноразово програмовані ПЗП полягає у руйнуванні (перепалюванні) частини плавких перемичок на поверхні кристала імпульсами струму амплітудою 30...50 мА у тих перетинах рядків і стовпців матриці нагромаджувача, куди потрібно записати 0(1). У початковому стані ВІС ПЗП має перемички в усіх перетинах рядків і стовпців. Програмування ВІС виконують у програматорі поданням електричних імпульсів, за допомогою яких перепалюють відповідні перемички. Тому таке програмування одноразове. Технічні засоби для виконання цієї операції досить прості, їх може побудувати сам користувач. Мікросхеми серії К556 виготовлено за ТТЛШ-технологією, вони мають час вибірки 45-85 нс і рівень споживаної потужності становить від 0,6 до 1 Вт. Для них характерна єдина напруга живлення 5 В, наявність вхідних і вихідних ТТЛ-рівнів напруги логічного 0 (0,4 В) і логічної 1 (2,4 В).

Типовий варіант реалізації ППЗП показано на рисунку 2.11 а графічне позначення мікросхеми ППЗП типу КР556РТ14 наведено на рисунку 2.12. Матриця до програмування, тобто у вихідному стані, містить однорідний масив провідних перемичок, що з’єднують рядки і стовпці в усіх точках їх перетинань. Перемички встановлюють з ніхрому, з полікристалічного кремнію, із сициліду платини та інших матеріалів. Перемичка в матриці виконує роль ЕП. Наявність перемички кодують логічною 1, якщо підсилювач зчитування являє собою повторювач, і логічним 0, якщо підсилювач зчитування – інвертор. Отже, мікросхема ППЗП у вихідному стані перед програмуванням залежно від характеристики вихідного підсилювача може мати матрицю, заповнену або логічним 0, або логічною 1. Програмування мікросхеми, матрицю якої у вихідному стані заповнено 0, полягає в перепалюванні перемичок у тих ЕП, де мають зберігатися 1. Якщо матрицю у вихідному стані заповнено 1, то перепалюють перемички в ЕП, де мають зберігатися 0.

Рис. 2.11 Побудова мікросхеми ППЗП.

Рис. 2.12 ПЗП К556РТ14.