2.1 Архітектура мікроконтролера

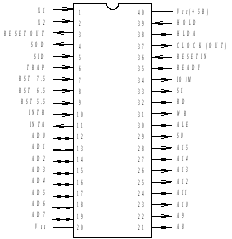

Для побудови мікроконтролера ми застосували процесор і8085. Це 8-розрядний однокристальний МП, з єдиною внутрішньою 8-розрядною шиною, по якій передаються дані, коди команд та адреси. Даний процесор має 40 виводів, схема призначення яких наведена на рисунку 2

Рис. 2.1 Виводи процесора і8085.

Таблиця 1 Виводи і їх призначення

|

|

|

|

Виводи |

Опис |

|

AD6-AD7 |

Шина адрес/даних |

|

A8-A15 |

Шина адрес |

|

ALE |

Дозвіл захоплення адреси |

|

RD |

Керування читанням |

|

WR |

Керування записом |

|

IO/M |

Покажчик введення/виведення |

|

S0,S1 |

Покажчик стану пам’яті |

|

READY |

Виклик стану очікування |

|

S1D |

Введення послідовних даних |

|

S0D |

Виведення послідовних даних |

|

HOLD |

Потреба захвату |

|

HLDA |

Підтвердження стану захвату |

|

INTR |

Запит переривань |

|

TRAP |

Запит незамаскованого переривання |

|

RST 5,5 RST 6,5 RST 7,5 |

Запит апаратного переривання |

|

INTA |

Підтвердження запита на переривання |

|

RESET IN |

Скидання системи |

|

RESET OUT |

Скидання периферії |

|

X1, X2 |

З’єднання кристала чи зовнішнього ГТІ |

|

CLK |

Сигнал внутрішнього ГТІ |

|

Vcc, Vss |

Живлення, земля |

Типовий процесор має 40 виводів, виводи 12-19 використовуються як рівноцінні лінії шини адрес/даних, тому цей мікропроцесор називається пристроєм з мультиплексорною шиною адрес/даних. Даний процес оснащений спеціальним сигналом, для того щоб інформувати периферійні пристрої про операції які виконуються на шині даних чи на шині даних. Цей спеціальний сигнал – ALE. A8-

A15 – це адресні лінії. Мікропроцесор і8085 оснащений внутрішнім генератором тактових імпульсів (ГТІ), входи якого X1, X2, зазвичай з’єднані з кристалом.

Більшість виводів даного процесора є стандартними для даного покоління процесорів, але деякі відмінності досить суттєві. Вхід READY інформує МП про те, що периферійні пристрої готові передати чи прийняти дані.

Вхід HOLD сповіщає МП, що інший пристрій хоче використати шини адрес і даних. Вихід HLDA вказує периферійним пристроям, що запит HOLD був отриманий і мікропроцесор не буде керувати шинами в наступному циклі тактових імпульсів.

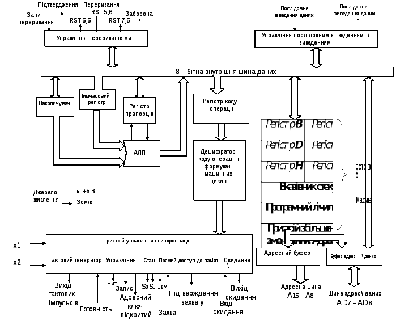

На рисунку 2.2 представлена функціональна схема МП Intel і8085, яка містить внутрішні регістри — акумулятор, пари регістрів В і С, D і Е, Н і L, покажчик стека SP, регістр стану (індикатор), декілька регістрів тимчасового зберігання даних. Ця схема містить також пристрій керування і синхронізації. Нарешті, вона містить також АЛБ який являє собою комбінаційну схему на основі суматора і логічних елементів, і призначений для виконання арифметичних та логічних операцій. Всі вісім ліній даних, так само як і 16-розрядні адресні виходи, забезпечено буферами.

Рис. 2.2 Функціональна схема МП і8085.

Мікропроцесор і8085 має такі особливі режими роботи: переривання, очікування, захоплення шин при ПДП.