- •Федеральное агентство по образованию Российской Федерации

- •Тема 12. Основы теории электронных приборов

- •Тема №2.Электрическое поле.Электрические цепи постоянного тока.

- •Тема №3. Магнитное поле.Магнитные цепи. Индуктивность и ёмкость в электрических цепях.

- •Свойства ферромагнитных материалов. Гистерезис.

- •Тема №4. Однофазные электрические цепи синусоидального тока.

- •Тема№5.Общие свойства четырёхполюсников.

- •Тема №6. Переходные процессы в электрических цепях.

- •Тема№7.Методы расчёта переходных процессов.

- •Какому знаку подчиняется сигнал на выходные цепи (вывод формулы)

- •Тема №8. Трехфазные электрические цепи.

- •Тема №9.Периодические и апериодические несинусоидальные сигналы.

- •Тема№10.Расчёт электрических цепей с помощью оператора Лапласа.Спектры.

- •Передаточная функция и ее связь с дифференциальным уравнением, импульсной и частотной характеристикой

- •Раздел 2. Электроника Тема 12. Основы теории электронных приборов

- •Параметры, характеристики выпрямительных диодов. Типы полупроводниковых диодов.

- •Параметры диодов.

- •Выпрямительные диоды

- •Усиление электрических сигналов с помощью биполярного транзистора.

- •Параметры транзистора:

- •Общая характеристика схем включения транзисторов p-n-p типа.

- •Полевые транзисторы.

- •Полевые транзисторы с изолированным затвором.

- •Полевой транзистор со встроенным каналом (мдп- транзистор).

- •Транзистор с индуцированный каналом (моп- транзистор).

- •Транзистор с затвором Шотки.

- •Силовые полупроводниковые приборы.

- •Оптоэлектроника.

- •Светодиод.

- •Тема 13. Транзисторные усилители электрических сигналов.

- •Коэффициент усиления.

- •Импульсные усилители (иу).

- •Электрические фильтры.

- •Дифференцирующие цепи.

- •Дифференцирующая rl-цепь

- •Интегрирующие цепи(фнч) (фильтр высоких частот)

- •Интегрирующая rc-цепь.

- •Интегрирующая rl-цепь

- •Активные фильтры.

- •Интегральные микросхемы

- •Тема 14. Аналоговые и цифровые элементы и устройства.

- •Логические элементы в дискретном исполнении

- •Триггеры в интегральном исполнении.

- •Тема 15. Комбинационные цифровые устройства.

- •Сумматоры

- •Демультиплексор

- •Регистры (узлы накапливающего типа)

- •Набор элементарных операций:

- •Параллельный статический регистр.

- •Расшифровка временной диаграммы.

- •Цифроаналоговые преобразователи (цап).

- •Аналого-цифровые преобразователи (ацп).

- •Запоминающие устройства (зу).

- •Классификация зу.

- •Тема 16. Источники вторичного питания. Генераторы.

- •Internet-ресурсы.

- •Http://ktf.Krk.Ru/courses/foet/(Сайт содержит информацию по разделу «Электроника»)

- •Http://www.College.Ru/enportal/physics/content/chapter4/section/paragraph8/theory.Html(Сайт содержит информацию по теме «Электрические цепи постоянного тока»)

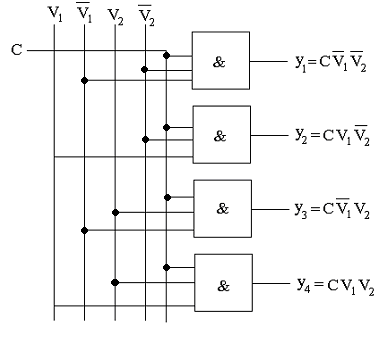

Демультиплексор

Демультиплексор или распределитель выполняет функцию обратную мультиплексора, т.е. преобразует последовательный вход в параллельный. Он осуществляет подключения входного сигнала на один из нескольких своих выходов (каналов направления).

Для случая, когда n=4,

демультиплексор в соответствии с

сигналами на адресных входах V1 и

V2передает двоичную информацию

со входа на один их четырех выходовy1,y2,y3,y4. В схеме даны

описания логическими функциями перехода

для каждого выхода.

Рис. 15-9. Логическая схема демультиплексора.

Схема сравнения или компаратор.

Цифровые

компараторы применяются для выполнения

сравнения двух чисел, заданных в двоичном

коде. Эти компараторы могут определять

для двух двоичных чисел «а» и «![]() »

операции а=

»

операции а=![]() ,

а>

,

а>![]() ,a<

,a<![]() .

На рисунке 4-10 представлена схема

одноразрядного компаратора, который

представляет собой логический элемент

«исключающее ИЛИ-НЕ». Работа схемы

представлена таблицей истинности. Если,

например, а>

.

На рисунке 4-10 представлена схема

одноразрядного компаратора, который

представляет собой логический элемент

«исключающее ИЛИ-НЕ». Работа схемы

представлена таблицей истинности. Если,

например, а>![]() обеспечивается для четырехразрядного

числа, в четырех случаях:

обеспечивается для четырехразрядного

числа, в четырех случаях:

а4>![]() 4

, а4=

4

, а4=![]() 4

и а3>

4

и а3>![]() 3

, или а4=

3

, или а4=![]() 4

, а3=

4

, а3=![]() 3

и а2>

3

и а2>![]() 2

, или а4=

2

, или а4=![]() 4

, а3=

4

, а3=![]() 3

и а2=

3

и а2=![]() 2

, а1>

2

, а1>![]() 1

. В том случае если поменять местами

аiи

1

. В том случае если поменять местами

аiи![]() i

то а<

i

то а<![]() .

.

Рис.15-10. Логическая схема одноразрядного компаратора.

Таблица истинности одноразрядного компаратора:

|

а |

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

Регистры (узлы накапливающего типа)

Регистр (RG)– это устройство для приема, преобразования, хранения и выдачи по команде информации. В качестве ячейки памяти используютсяRS,DилиJKтриггер, которые могут хранить одноразрядные двоичные числа.

Для хранения n-разрядных чисел необходимо “n” триггеров.

Запись информации и считывание в триггере могут производится:

Параллельно, всеми разрядами одновременно, т.е. во все разряды одновременно заносится один такт.

Последовательно, т.е. поочередно начиная со старшего или младшего разряда.

По способу ввода или вывода информации регистра различают:

Однофазного типа.

В этом случае операция производится только в прямом или только в обратном коде.

2) Парафазного типа.

Это когда запись и считывание производится как в прямом так и в обратном коде.

Регистры также разделяют на:

Асинхронные(функцию тактирующих сигналов производят управляющие сигналы)

Синхронные (управляющие сигнала стробируются тактирующими импульсами. Стробирующий сигнал - это импульс, выделенный во времени)

Набор элементарных операций:

Установка– это запись в операционный элемент двоичного кода (установка «0» во всех разрядах счетчика).

Передача – прием– перезапись кода числа из одного операционного элемента в другой.

Сдвиг– это изменение положения разрядов кода относительно первоначального.

Преобразования– это адресная передача сигнала от многих источников к одному потребителю.

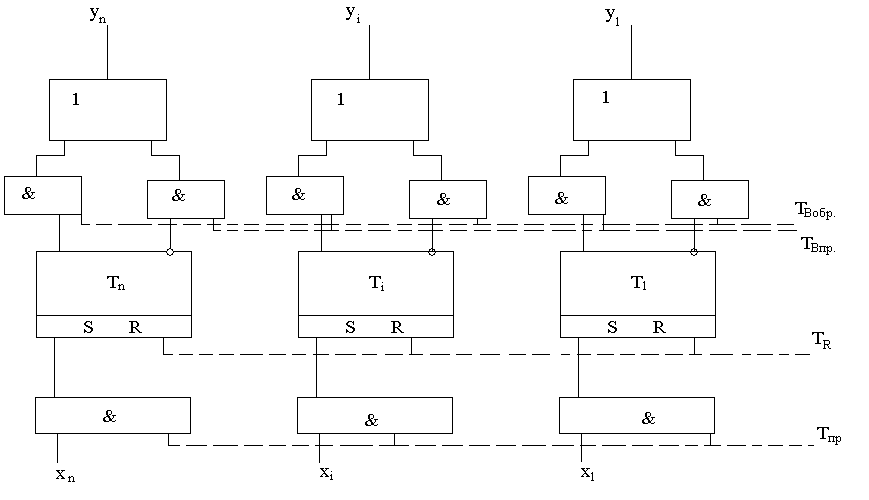

Параллельный статический регистр.

Схема параллельного статического регистра представлена на рис 15-11.

Рис. 15-11. Схема параллельного статического регистра.

Условное обозначение параллельного статического регистра:

Запись и хранение в параллельном статическом регистре .

Начальное

состояние

![]() или ввод равняется «0», т.е. ввод

отсутствует. На входахRSтриггеры устанавливаются «1». Далее на

х2=0, на х1=1, а при состоянии

или ввод равняется «0», т.е. ввод

отсутствует. На входахRSтриггеры устанавливаются «1». Далее на

х2=0, на х1=1, а при состоянии![]() (запись и чистка) = 1 переключает логический

элемент

(запись и чистка) = 1 переключает логический

элемент![]() и на входеRSтриггераT1появляется 0, аQ1=1.

(Смотри работуRSтриггера).

На входеT2остается

1 и соответственно на выходеT2Q2=0.

и на входеRSтриггераT1появляется 0, аQ1=1.

(Смотри работуRSтриггера).

На входеT2остается

1 и соответственно на выходеT2Q2=0.

Описанную работу регистра – это запись информации в регистр и ее хранение.

Считывание (рисунок 15-11).

На

выходах у1и у2, работающих

в режиме хранения устанавливаются 0 при![]() =1,

на у1=1, на у2=0. Это и есть

процесс считывания информации.

=1,

на у1=1, на у2=0. Это и есть

процесс считывания информации.

Параллельный регистр построенный на “n” триггерах(рисунок 4-12).

В исходное состояние (нулевое) на все n-триггеров необходимо податьTR=1 (TRподсоединяется ко всемRSтриггерам кRсм. предыдущую схему) запись и чистка.

Чтобы запомнить число х1значение всех всех егоnразрядов подаются на входы хi.Подача сигнала Тпр(прямой)(это тактовый импульс). С числом х1(хi1, хi2, … , хin), которое хранится в регистре, могут выполняться поразрядные сложение числа, умножение и т.д. Когда подаются сигналы Тпрследующие, триггеры, хранящие значение «1» в разрядах числа х1, сохраняют своё состояние каким бы ни было значение одноименного разряда х2, а хранившие «0» либо сохраняют его(если значение одноименного разряда х2=0), либо переключаются в «1», если в разряде числа х2есть «1».

Рис. 15-12. Схема параллельного регистра, построенный на “n” триггерах.

Ввод:

![]()

![]()

Вывод:

Последовательные сдвигающие

регистра(RG![]() )

)

В таких регистрах ввод-вывод регистрируемого кода производится последовательно разряд за разрядом со сдвигами (передачей) состояния предыдущего триггера последующему.

|

i-1 |

i |

i+1 |

|

0 |

1 |

1 |

|

0 |

0 |

1 |

|

1 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

0 – влево Сдвиг вправо на 1 разряд соответствует операции деления на 2, а сдвиг влево на 1 разряд соответствует операции умножения.

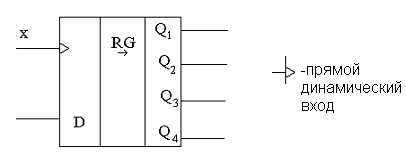

Последовательный регистр, построенный на D-триггерах(рис 15-13).

Рис. 15-13. Последовательный регистр, построенный на “D” триггерах А) и его временная диаграмма Б).

Условное обозначение последовательного регистра на D-триггерах:

По приходу тактового импульса «С» первый D-триггер записывает код «х» («0» или «1»), находящийся в этот момент на егоD-входе, а каждый следующийD-триггер переключается в состояние, в котором до этого находился предыдущий. Таким образом записываемый сигнал проходит со входаD-триггера к выходу “Q” с задержкой, имеющий длительность большую, чем передний фронт тактового импульса. В этот момент и происходит запись информации. Каждый тактовый импульс последовательно сдвигает код числа в регистре на один разряд. Для записи «n»-разрядного кода необходимо «n» тактовых импульсов.