Схемотехника / Учебники и методички / potehin

.pdf

3.2. Транзисторно-транзисторная логика

Транзисторно-транзисторная логика (ТТЛ) малой степени интеграции появилась на первом этапе развития интегральной схемотехники (19691985 г.г.). Эти схемы характеризуются хорошими электрическими параметрами, удобны в применении, обладают большим функциональным разнообразием. Серия К155 (аналог известной серии SN74) отличалась большой функциональной полнотой – в ее составе 103 интегральных МСХ (155 серия имеет 89 ИС, КМ155 – 91 ИС). Используются данные микросхемы в ранее выпускавшихся изделиях.

3.2.1. Базовый логический элемент ТТЛ

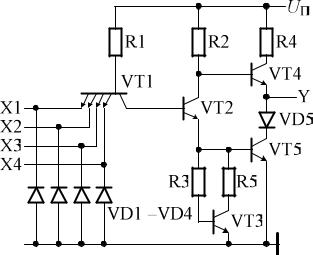

Классической структурой ТТЛ является схема базового элемента И-НЕ серии 133, 155 (рис. 3.3). Схема содержит входной многоэмиттерный транзистор VT1, реализующий функцию И, фазосмещающий каскад на транзисторе VT2; двухтактный выходной каскад, выполненный по схеме составного эмиттерного повторителя на транзисторах VT4 и VT5 с введением диода сдвига уровня VD5 и компенсирующий транзистор VT3. Эмиттеры транзистора VT1 служат входами логического элемента и соединены с шиной нулевого потенциала через обратно смещенные антизвонные диоды VD1-VD4. Последние

Рис.3.3. Схема базового логического элемента И-НЕ серий 133, 155, SN54, SN74

служат своего рода демпфером, защищая от отрицательного входного напряжения транзистор VT1.

Подадим на один или несколько входов Х многоэмиттерного транзистора (МЭТ) напряжения лог. 0 (рис. 3.4).

Эмиттерный переход МЭТ, на входе которого установлен низкий уровень, будет смещен в прямом направлении, т. к. через резистор R1 на его базу подается высокий уровень (напряжение питания UП = + 5В). Напряжение на базе

МЭТ будет складываться из входного напряжения Uвх0 и напряжения прямос-

51

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

мещенного перехода БЭ кремниевого транзистора, примерно, равного 0.7 – 0.8 В:

= UБЭ1 + Uвх0 ≈ 0.7 + 0.1 = 0.8 В.

Напряжения 0.8 В недостаточно чтобы открыть три перехода: UБК1, UБЭ2, UБЭ5. Для отпирания трех переходов необходимо иметь напряжение не менее 3

0.7 = 2.1, в связи с чем транзистор VT2 заперт. Ток Iвх0 вытекающий из эмиттера МЭТ, на входе которого низкий уровень, определится величиной сопротивления резистора R1, величина которого колеблется от 2.8-4.0-7.5 кОм для стандартной серии, и напряжением на базе UБ1 МЭТ. Для R1 = 2.8 кОм величина тока

Iвх0 = – (UП – 0.8)/ 2.8×103 = – 1.5 мА.

Всправочниках указывается максимальное значение тока Iвх0 = – 1.6 мА, по-

скольку учитывают разброс параметров Uвых0 , UБЭ1, R1. |

|

|||||

R4 |

|

|

R1 |

IБ4 |

R4 |

R1 |

|

|

R2 |

||||

заперт |

|

VT1 |

IБ1 |

|

VT4 |

VT1 |

|

|

|

||||

VT4 |

|

|

|

|

||

|

|

|

VT2 |

VD1 UВЫХ1 |

||

UВХ0 |

|

|

заперт |

|||

I |

0 |

заперт |

|

IВХ1 |

||

открыт |

|

ВХ |

|

|

VT5 |

|

|

|

R3 |

R5 |

|

IН |

|

|

|

|

|

|||

VT5 |

|

|

|

VT3 |

|

СПАР |

DD1 |

|

DD2 |

|

|

|

RН |

|

|

|

|

DD3 |

||

Рис. 3.4. Токи и напряжения в ЛЭ при низком входном уровне |

||||||

Как указывалось, при низком уровне на любом из входов транзистор VT2 заперт, следовательно, на его коллекторе высокое напряжение, которое подается на базу транзистора VT4 и является для него отпирающим. Базовый ток VT4 течет по цепи UП-R2-БЭ4-VD5-Rн. Формально резистор Rн является эквивалентом всех МСХ, которые подключены к данному выводу. Максимальное число подключаемых входов определяется коэффициентом разветвления и может равняться 8-10. Учитывая, что при высоком выходном уровне сигнала, все подключаемые каскады запираются, то их входные токи не превышают величины 10-20 мкА. Суммарный ток нагрузки равен IН ≈ 100 – 200 мкА при

Краз = 10.

Максимальный базовый ток IБ4m может возникать только в случае короткого замыкания на выходе или случайном подключении данного выхода к от-

52

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

крытому выходу другой МКС. При кротком замыкании на выходе и R1 = 1.6 кОм величина тока IБм может возрасти до значения:

IБм = (UП – UБЭ4 – VD5)/ R2 = (5 – 0.7 – 0.7)/1600 ≈ 2.25 мА.

Коллекторный ток выходного транзистора VT4, связанный с током базы соотношением IК = IБ β, при этом может возрасти до большой величины, что может привести к тепловому разрушению МСХ. Поэтому коллекторной цепи VT4 установлен защитный резистор (ограничитель величины тока) R4 = 130 Ом. Максимальное значение коллекторного тока IК4m будет ограничено величиной

IК4m = (– UКЭ4Н – VD5)/ R4 = (5 – 0.1 – 0.8)/130 ≈ 31.5 мА,

где UКЭ4Н – напряжение коллектор – эмиттер насыщенного транзистора, равное 0.1 В.

Рассмотрим второй вариант управления базовым элементом.

Установим на всех входах МЭТ высокие уровни, например, подключив их через резистор 1 кОм к источнику питания + 5 В (рис. 3.5).

IК4 |

R4 |

R1 |

|

R2 |

|

|

R1 |

IБ4 |

|

IБ1 |

|

IК2 |

VT4 |

U |

0 |

VT4 |

VT1 |

|

|

|

ВЫХ |

||

|

|

|

VT2 |

VD1 |

|

VT1 |

|

|

|

|

|

|

|

||

|

|

|

|

IБ5 |

|

|

|

|

1 |

|

|

VT5 |

IВХ0 |

||

|

I ВХ |

UВХ |

|

|

|||

|

|

R3 |

R5 |

|

|

|

|

|

|

|

|

VT3 |

|

|

|

DD1 |

|

DD2 |

|

|

|

|

DD3 |

Рис. 3.5. Токи и напряжения ЛЭ при высоком входном логическом уровне |

|||||||

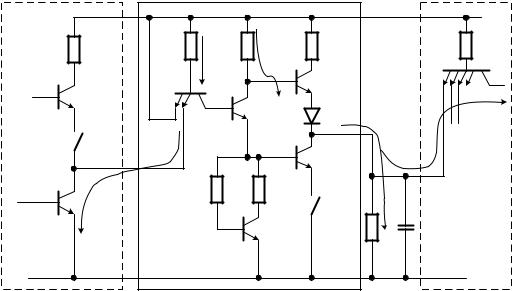

Переходы Б1-Э1 VT1 смещены в обратном направлении, т. к. на эмиттере уровень лог. 1, на базе напряжение понижено за счет протекания тока базы через резистор R1. Переход Б1-К1 VT1 смещен в прямом направлении. Базовый

ток IБ1 течет по цепи ЕП-R1-Б2-Э2-Б3-Э3-GND (земля, нуль, общий провод). Ток базы IБ1 частично ответвляется в параллельную ветвь, выполненную на тран-

зисторе VT3. Транзистор VT3 совместно с резисторами R3 и R5 выполняет роль термокомпенсирующей цепи для транзистора VT5. Напряжение на базе МЭТ является суммой напряжений трех переходов:

= UБК1 + UБЭ2 + UБЭ5 ≈ 3 × 0.7 = 2.1 В.

Напряжение UБ1 безусловно меньше напряжения поданного на эмиттер и этот переход Б1-Э1 заперт.

53

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Базовый ток второго транзистора IБ2, практически равный базовому току первого транзистора при R1 = 4 кОм по величине будет приблизительно равен:

IБ2 = (UП – 3 × UБЭ)/ R1 = (5 – 2.1)/4000 ≈ 0.72 мА.

Транзисторы VT2 и VT5 открыты и насыщены, напряжение UКЭН каждого из них будет, примерно, равно (0.1-0.2) В. Напряжение на коллекторе VT2 относительно нулевого потенциала равно UК2 = UКЭН + UБЭ5 ≈ 0.1 + 0.8 = 0.9 В.

Этого напряжения недостаточно чтобы открыть два перехода: переход Б4-Э4 выходного транзистора VT4 и переход диода VD1, следовательно, оба перехода заперты. Поэтому на рисунке 3.5. цепочка, состоящая из транзистора VT4 и диода VD5, показана пунктиром, поскольку в работе ЛЭ не участвует.

Коллекторный ток IК5 обеспечивает выходной ток, равный сумме входных токов всех подключенных нагрузок. При Краз = 10 и максимальном входном токе одного ЛЭ 1.65 мА величина коллекторного тока IК5 должна иметь величину IК5 ≥ 10 1.65 = 16.5 мА.

В динамическом режиме, когда идут переходные процессы, токи транзисторов могут существенно превышать их статические значения. При U 1ВХ транзисторы VT2 и VT5 открыты и насыщенны, в их базо-эмиттерных областях накапливается избыточный заряд неосновных носителей. В момент перехода управляющего импульса с высокого уровня на низкий, транзистор VT1 переходит в активный режим и своим коллекторным током рассасывает избыточный заряд. В течении нескольких наносекунд ток во входной цепи значительно превышает статическое значение. По окончании процесса рассасывания VT2 и VT5 начинают запираться, однако VT4, работающий в активном режиме, отпирается чуть раньше момента запирания VT5. В результате чего некоторое время через VT4, VD5, и VT5 от источника питания UП протекает сквозной ток, величина которого ограничивается сопротивлением защитного резистора R5. Кратковременные пики тока могут достигать величины 25–30 мА, что вызывает появление импульсной помехи в цепях питания. Для уменьшения уровня помех рекомендуется шунтировать по питанию каждую микросхему высокочастотным конденсатором 0.01 – 0.1 мкФ.

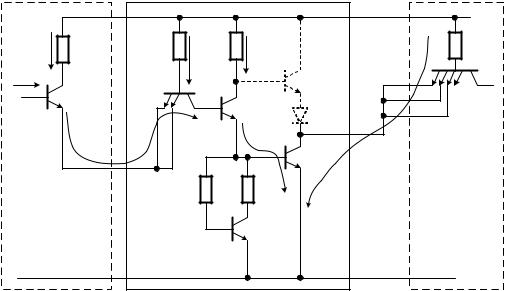

Статические характеристики ЛЭ ТТЛ

Передаточная характеристика базового логического элемента ТТЛ, представляющая собой зависимость UВЫХ =f (UВХ) приведена на рисунке 4.5, а. На этом же рисунке в сопоставимом масштабе представлена входная характеристика.

При нулевом напряжении на входе одного из эмиттеров МЭТ ток вытекает из эмиттера, его величина определяется сопротивлением R1, транзисторы VT2, VT3 и VT5 заперты, а VT4 и диод VD5 открыты (точка 1), напряжение

на выходе высокое – Uвых1 . При увеличении входного напряжения до порогового значения UП1 = 0.8 В (точка 2 на передаточной характеристике) транзистор VT2 начинает открываться, но VT4 все еще заперт. При напряжении на входе UП2 = 1.2 В транзистор VT2открывается, а VT4 начинает только откры-

54

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

ваться (точка 3). Дальнейшее увеличение напряжения на входе до 1.5 В приводит к тому, что ток через транзистор VT2 резко нарастает, так как открывается переход база-эмиттер VT5 и коэффици-

|

|

|

|

ент усиления транзистора VT2 возрастает, |

|

|

|

|

|

||

|

|

|

|

за счет уменьшения отрицательной обрат- |

|

|

|

|

|

ной связи по эмиттеру. |

|

|

|

|

|

Напряжение на коллекторе VT2 падает |

|

|

|

|

|

(точка 4 на передаточной характеристике). |

|

|

|

|

|

Входной ток резко уменьшается и меняет |

|

|

|

|

|

знак на противоположный. Короткое время |

|

|

|

|

|

||

|

|

|

|

VT4 все еще заперт, а VT5 уже открыт и че- |

|

|

|

|

|

||

|

|

|

|

рез них протекает ток «короткого замыка- |

|

|

|

|

|

ния», приводящий к увеличению потреб- |

|

|

|

|

|

||

|

|

|

|

ляемой мощности от источника питания. |

|

|

|

|

|

Входной ток I 1ВХ при напряжении Uвх1 2 –3 |

|

|

|

|

|

||

Рис. 3.6. Характеристики : |

В мал и равен, примерно 10 – 20 мкА. Воз- |

||||

а передаточная; б входная |

растает входной ток при Uвх1 = 4 В и может |

||||

достичь предельно допустимого значения Iвх1 |

mах = 40 мкА, в связи с чем ре- |

||||

комендуется соблюдать условие U1вх ≤ 4 В.

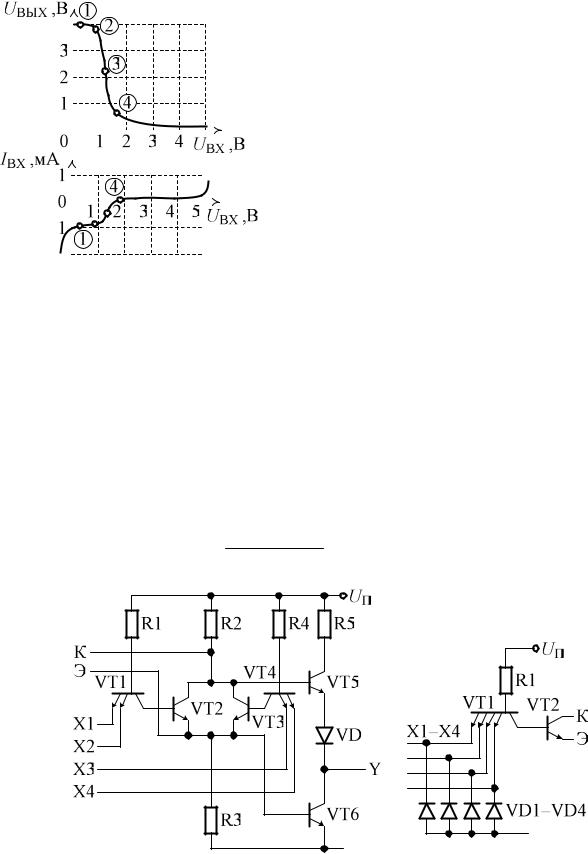

3.2.2. Логические элементы ИЛИ-НЕ

Схемотехнически почти все ЛЭ, входящие в состав серий ТТЛ могут быть образованы комбинированием двух базовых схем: элемента И-НЕ (рис. 3.7, а) и расширителя по ИЛИ (рис. 3.7, б). Схема логического элемента И- ИЛИ-НЕ (ИЛИ-НЕ) получается путем подключения параллельно ключевому транзистору дополнительных транзисторов, как показано на рис. 3.7, а (половина ИС К155ЛР1). В результате имеем логический элемент 2И-2И-2ИЛИ,

реализующий функцию y = x1x2 x3x4 .

а |

б |

Рис.3.7. Логический элементы: а – И-ИЛИ-НЕ; б – расширитель по

55

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Причем если входы х1 и х2, а также х3х4 перемкнуть, то получим двухвходовую схему ИЛИ. Если же на один из входов подать уровень лог.0, то схема

реализует двухвходовую схему И-НЕ: y = 0 x2 |

x3 x4 |

= x3 x4 . Присое- |

динением логического расширителя по ИЛИ можно расширить функциональные возможности логического элемента. Для всех ТТЛ, имеющих возможность расширения по ИЛИ, максимальное число объединений равно восьми.

При присоединении одного расширителя задержка распространения схемы увеличивается примерно на 5 нс, а потребляемая мощность – на 5 мВт.

В составе серий 155, 133 имеются более сложные микросхемы структуры И-ИЛИ-НЕ: ЛР3 – логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ. Такие микросхемы обладают большой функциональной гибкостью. Кроме того, в составе этих серий имеются логические элементы типа ЛЕ, реализующие логическую функцию ИЛИ-НЕ. Например, К155ЛЕ1 содержит четыре логических элемента 2ИЛИ-НЕ, К155ЛЕ2 – два логических элемента ИЛИ-НЕ со стробированием на одном элементе и возможностью расширения по ИЛИ на другом и другие.

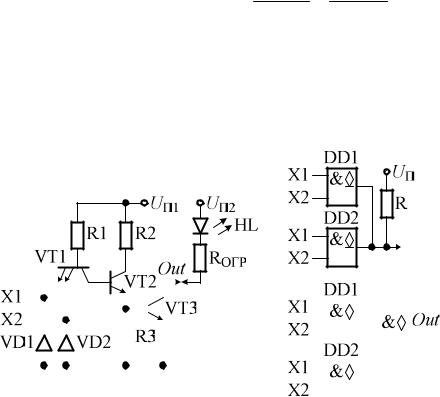

3.2.3 Логические элементы с открытым коллектором

и тремя состояниями выхода

Физические параметры и функциональные возможности ЛЭ существенно зависят от схемы включения выходного каскада. На практике встречается пять основных видов выходных каскадов: со стандартным выходом, с открытым коллектором, с открытым эмиттером, с тремя состояниями выхода и с мощным выходным каскадом на выходе. Стандартные микросхемы имеют два со-

стояния выхода: высокий уровень напряжения на выходе U1вых , когда открыт верхний транзистор и диод, а выходной ток I1вых небольшой (рис. 3.8). Низкий уровень напряжения Uвых0 , когда открыт нижний транзистор, который обеспе-

чивает достаточно большой выходной ток Iвых0 . Работают выходные каскады всегда в противофазе, причем вместо верхнего транзистора и диода может использоваться составной транзистор. ЛЭ со стандартным выходом имеет нагрузочную способность n = 10 (n = 20 для 555 серии, n = 33 для 1531 серии); такой же выходной каскад с повышенной нагрузочной способностью может иметь значения n до 300. Выходы некоторых микросхем выполнены так, что верхний транзистор и относящиеся к нему элементы отсутствуют. В качестве выходного каскада используется транзистор, выход которого не подключен к нагрузке (рис. 3.9.).

Эти транзисторы изготавливаются на разное допустимое напряжение питания: +5, +15, +30, +35 В и др. Выходы таких ЛЭ подключаются с помощью

внешнего резистора и обеспечивают большой ток выхода Iвых0 (втекающий в коллектор). Поэтому в выходную цепь транзистора можно включить элементы индикации, исполнительные механизмы, электромагнитные реле и т.д.

56

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Логические элементы с открытым коллектором допускают параллельное подключение несколько выходов к общей нагрузке и реализацию с их помощью логических функций, называемых «монтажное ИЛИ» и «монтажное И». Выходное напряжение может принять уровень логической единицы только в том случае, если все выходные транзисторы закрыты:

Y Y1Y2 X1X 2 X 3 X 4

Если хотя бы на одном выходе будет логический 0, то на выходе всей системы будет низкий потенциал. Для обозначения ЛЭ с открытым коллектором используют ромб с чертой снизу . Для обозначения псевдоэлемента «монтажное И, ИЛИ» рядом со знаком & или 1 ставится ромбик – . При использовании ЛЭ в режиме «монтажной логики» каждая МСХ теряет свою са-

б

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Рис.3.9. Логический элемент ТТЛ с открытым коллектором: а - принципиальная схема с внешней нагрузкой; б - «монтажное И»; в - условное графическое изображение; - открытый коллектор, - монтажное соединение

мостоятельность.

1. Логические элементы, выходные каскады которых выполнены с открытым эмиттером, отличаются тем, что эмиттер выходного каскада не подключен внутри ИС к общей шине, а оформлен в виде отдельного вывода, а на коллектор подано напряжение источника питания. Такие ЛЭ используются в интерфейсных устройствах (например, 559 ИП4, 1102АП2 и др.) и работают как эмиттерные повторители. Они обеспечивают малое выходное сопротивле-

ние и большой ток выхода I1вых вытекающий из эмиттера. На условных изображениях схемы с открытым эмиттером обозначаются специальным значком

(ромбик с черточкой сверху).

2.В интерфейсных устройствах используются выходные каскады, представляющие собой изолированные мощные транзисторы, электроды которых (эмиттер, коллектор, база) подключены к внешним выводам ИС. Выходные каскады с изолированными транзисторами используются в логических элементах типа передатчиков (155 ЛП7, 1102АП5...) и обеспечивают выходной

ток до 300 мА. На условных графических обозначениях ЛЭ с мощным выходом обозначается треугольником.

57

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

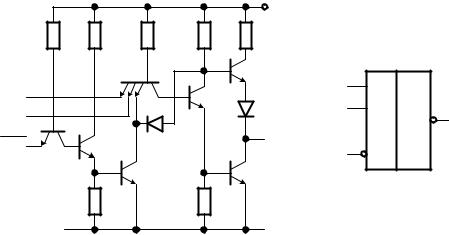

3. Логические элементы с тремя состояниями выхода отличаются от стандартных микросхем тем, что могут переводиться в высокоимпедансное состояние – состояние Z, когда выход отключен от источника питания и от общей шины (рис. 3.10).

|

|

|

|

UП |

R1 |

R2 |

R4 |

R5 |

R7 |

|

|

VT4 |

|

VT6 |

& θ |

X1 |

|

|

VT5 |

X1 |

|

|

|

VD2 X2 |

Y |

||

X2 |

|

VT2 VD1 |

|

Out |

|

OE |

VT1 |

|

OE |

||

|

VT3 |

|

VT7 |

||

|

|

|

|

||

|

|

R3 |

R6 |

|

б |

а

Рис. 13.10. Логический элемент с тремя состояниями выхода:

а – принципиальная схема; б – условное обозначение.

ЛЭ имеет встроенную цепь управления, содержащую транзисторы VT1,VT2,VT3, диод VD1 и имеет вход OE (Output Enable – разрешение выхода). При низком уровне на OE ЛЭ работает как устройство со стандартным выходом, так как на базе VT2 низкий уровень напряжения, транзистор VT3 и диод VD1 находятся в непроводящем состоянии. При OE = 1 по цепи UП-R1- Б2-К2- Б3-Э3- протекает ток, переводящий транзистор VT3 входит в насыщенное и диод VD1 оказывается подключенным по общей шине через транзистор VT3. В результате на коллекторе и базе транзистора VT5 устанавливается низкое напряжение и выходные каскады VT6,VT7 запираются, ток утечки этих транзисторов составляет 20-40 мкА.

Выходы ИС с тремя состояниями можно объединять, что расширяет функциональные возможности MCX. Необходимо лишь обеспечить условие, чтобы в активном состоянии в данный момент находился лишь один выход

3.2.4. Разветвление и объединение ЛЭ

Для обеспечения работоспособности логических микросхем различных серий друг от друга при условии сохранения параметров MCX, оговоренных в технических условиях на них, следует выполнять требования по уровням выходных напряжений и токов при формирования уровней лог.0 и лог.1, а также по значения суммарной емкостной нагрузки.

Выходные напряжения ЛЭ – источников сигналов в открытом и закрытом состоянии при определенной нагрузке должны соответствовать входным пороговым напряжениям закрытого и открытого состояния ЛЭ – нагрузки с уче-

том величины напряжения помехи:

Uвых0 Uпор0 Un0;U1вых U1пор U1n,

58

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

|

где Uвых0 , Uвых1 – выходные напряжения ЛЭ в открытом и закрытом со- |

|||||||||

стоянии; Uпор0 , |

Uпор1 – порог отпирания и запирания ЛЭ, соответственно; Uп0, |

|||||||||

Uп1 |

– допустимое напряжение помехи на отпирание и запирание ЛЭ нагрузки. |

|||||||||

|

Уровень помехи, как правило, заранее неизвестен и может быть опреде- |

|||||||||

лен лишь на этапе экспериментального макетирования. |

|

|||||||||

|

Значение суммарных токов всех ЛЭ – нагрузок не должно превышать |

|||||||||

значений выходных токов MCX – источника в открытом и закрытом состоя- |

||||||||||

ниях: |

|

|

K раз |

|

|

|

|

K раз |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Iвых0 |

Iвх0 |

i ; |

Iвых1 |

|

Iвх1 |

i , |

|

|

где Iвых0 , |

Iвых1 |

|

i 1 |

|

|

|

|

i 1 |

|

|

– соответственно выходные токи в открытом и закрытом |

|||||||||

состоянии; Iвх0 |

, Iвх1 |

– входные токи для одного элемента нагрузки при Uвх0 |

||||||||

Uвх1 |

соответственно; Kраз – число логических входов, подключаемых к выходу |

|||||||||

MCX – источника. |

|

|

|

|

|

|

|

|

||

|

Суммарная емкость, подключаемая к источнику сигнала, не должна пре- |

|||||||||

вышать емкость ЛЭ – источника Cн, при которой гарантируются временные |

||||||||||

параметры, т.е. |

|

|

|

K раз |

K раз |

|

|

|||

|

|

|

|

|

|

|

||||

|

|

|

C Н |

С вх ,нi С m i , |

|

|||||

|

|

|

|

|

i 1 |

i 1 |

|

|

||

где Cвх – максимальная емкость входа ЛЭ (примерно, 3пФ); Cм – емкость монтажных соединений одного входа нагрузки.

Коэффициент разветвления по выходу определяется следующими выражениями:

Краз0 = Iвых0 /Iвхн0 ; К1раз = I1вых /I1вхн ; Kс = (Сн + См)/Свхн,

где Краз0 , К1раз – нагрузочная способность ЛЭ – источника сигнала в от-

крытом состоянии, соответственно; Kс – емкостная нагрузочная способность ЛЭ источника.

Наименьший из вычисленных коэффициентов принимается за Kраз для нагружаемой MCX.

Если требуется определить допустимое значение единичных нагрузок ИС других серий, расчет ведут аналогичным образом, подставляя значения вход-

ных токов Iвх0 , I1вх соответствующей серии. Ниже приводятся таблицы входных и выходных токов различных серий (табл. 3.1) и число единичных нагрузок при сопряжении различных серий (табл. 3.2).

59

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Таблица 3.1

ИС – передатчик |

|

Число единичных нагрузок |

|

||

|

155 |

531 |

555 |

|

1533 |

155 |

10 |

8 |

20 |

|

20 |

531 |

12 |

10 |

50 |

|

50 |

555 |

5 |

4 |

20 |

|

20 |

1533 |

2 |

2 |

10 |

|

20 |

Отметим, что токи Iвых0 и I1вых в таблице имеют те значения, при кото-

рых ТУ гарантируются значения логических уровней Uвых0 и U1вых. Превыше-

ние выходных токов допустимых значений приводит к изменению Uвых0 и

U1вых, причем т.о., что в целом снижается помехоустойчивость ИС.

|

|

|

|

Таблица 3.2 |

Серия |

0 |

1 |

0 |

0 |

|

Iвх , мА |

Iвх , мА |

Iвых, мА |

Iвых, мА |

155 |

-1,6 |

0,04 |

16 |

-0,4 |

531 |

-2 |

0,05 |

20 |

-1 |

555 |

-0,36 |

0,02 |

8 |

-0,4 |

1533 |

-0,2 |

0,02 |

4 |

-0,4 |

|

|

|

|

|

При объединении выходов с открытым коллектором необходимо обеспечить логические уровни выходных напряжений, соответствующие уровням

устройств со сложным выходом: U1вых 2,4 В и U0вых 0,4 В. Для этого надо рассчитать величину нагрузочного сопротивления Rн при выбранном Uн, обеспечить заданные уровни лог.0 и лог.1 при данной конфигурации схемы и используемых серий ЛЭ.

При выборе сопротивления нагрузки, следует учитывать, что максимальное быстродействие обеспечивается при минимальном сопротивлении, однако при этом возрастает потребление мощности. При увеличении RH увеличивается время заряда паразитных емкостей.

В табл. 3.3 приведены значения количества единичных нагрузок, под-

|

|

|

|

Таблица 3.3 |

|

ИС – передатчик |

|

Число единичных нагрузок |

|||

|

155 |

531 |

555 |

|

1533 |

155ЛА6 |

30 |

24 |

60 |

|

60 |

555ЛА6 |

15 |

12 |

60 |

|

60 |

155ЛА12 |

30 |

24 |

60 |

|

60 |

531ЛА12 |

37 |

30 |

150 |

|

150 |

555ЛА12 |

15 |

12 |

60 |

|

60 |

531ЛА16 |

37 |

30 |

15 |

|

150 |

ключаем к ИС с открытым коллектором.

60

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)