Схемотехника / Учебники и методички / potehin

.pdf

По направлению передачи информации они подразделяются на однонаправленные и реверсивные.

5.8.2. Параллельные регистры

Двоичное n-разрядное число, предназначенное для хранения, поступает на вход регистра памяти в параллельной форме, т.е. все разряды подаются одновременно. Рационально в качестве регистра использовать простейшие триггера типа D, управляемые потенциалом или фронтом. В одном корпусе может быть размещено четыре, шесть или восемь отдельных триггеров, связанных общими цепями синхронизации и управления.

Микросхемы К555ТМ8 и К555ТМ9 представляют собой четыре и шесть D-триггеров, соответственно, с общим входом синхронизации и общим входом сброса (рис. 5.23). ИС К555ТМ8 имеет внешние выводы с прямого и инверсного выхода, а ИС К555ТМ9 - только прямой выход.

Схемы выполнены на двухступенчатых, синхронных, динамических D- триггерах. Вход сброса управляется инверсным сигналом, а вход синхронизации - прямым сигналом.

а б в

Рис. 5.23. Функциональная схема – а; условное обозначение ИС КР1554ТМ8– б; функциональное обозначение ИС КР1554ТМ9 – в

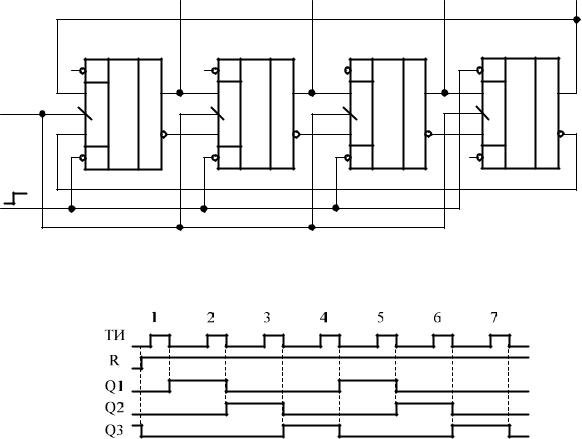

Рис. 5.24. Временные диаграммы

Регистры характеризуются минимальной длительностью импульса для записи информации и определенными временными соотношениями по времени установления tуст и времени удержания tуд на входах управления регистров относительно входов информации. Время установления сигнала - это интервал времени, который необходим для установки сигнала информации с оп-

181

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

ределением сигнала синхронизации (разрешения) при записи информации. Время удержания сигнала – это интервал времени, который необходим для завершения записи при удержании сигнала информации на заданном уровне после воздействия сигнала синхронизации. Следует обратить внимание на то, что информационный сигнал единичного или нулевого уровня на входе D должен установиться до прихода переднего фронта импульса за время, превышающее минимальное значение tуст, и должен сохранять свой уровень в течение некоторого времени, превышающего минимальное значение tуд. Следовательно, для обеспечения надежной работы регистра памяти необходимо, чтобы длительность импульса синхронизации Ти превышала tуд минимум в 2- 3 раза. Длительность паузы Тп между импульсами синхронизации также должна существенно превышать минимальное значение tуст. Необходимо отметить, что для записи информации в регистр нет необходимости в очистке регистра, т.е. в его обнуление с помощью сигнала.

Временные диаграммы, поясняющие работу триггерной ячейки регистра памяти, приведены на рисунке 5.24.

Значительный интерес для разработчиков радиоэлектронной аппаратуры представляют восьмиразрядные регистры памяти серий К555, К531, 1533:

ИР22, ИР23, ИР27, ИР33, ИР34, ИР35, ИР37.

Все упомянутые регистры имеют достаточно сходную логическую структуру и различаются лишь некоторыми частностями в организации ввода и вывода информации.

Микросхема 1533ИР37 представляет собой восьмиразрядный буферный регистр. Логическая структура и условное обозначение приведены на рисунке

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

C |

RG |

Q1 |

19 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

E0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

2 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

D1 |

|

|

18 |

|||

|

|

|

11 |

|

|

|

|

|

|

|

D |

T |

|

|

|

|

Q1 |

|

Q2 |

||||||||

C |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

Z |

|

|

|

|

3 |

|

|

|

|

||||

D1 |

2 |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

Q3 |

17 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

4 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

D3 |

|

|

|

||||||

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

16 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

5 |

|

D4 |

|

Q4 |

||||||

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

D4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q4 |

6 |

|

|

|

|

|||||

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

D5 |

|

|

15 |

||||||

D5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q5 |

|

|

Q5 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

7 |

|

|

|

||||||

D6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q6 |

|

D6 |

|

|

14 |

||||||

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

Q6 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

D7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q7 |

8 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

12 |

|

9 |

|

|

|

Q7 |

|||

D8 |

|

|

|

|

|

|

|

D |

T |

|

|

|

|

Z |

|

|

|

Q8 |

|

|

D8 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E0 |

|

Q8 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|||

Рис. 5.25. Структура - а и уловное обозначение регистра 1533ИР37 – б

5.25, а, б.

182

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Регистр построен на D – триггерах с импульсным управлением, вход прямой динамический, переключение производится положительным фронтом тактового импульса. Регистр имеет восемь входов данных D0...D7 и восемь выходов Q0…Q7. Когда на специальный вход E0 подается низкий уровень, то после поступления положительного перепада на тактовый вход С, входная информация появляется на выходах Q. Если на E0установлен высокий уровень, то выходные буферные каскады переводятся в высокоимпедансное состояние (состояние Z ). При низком уровне тактового сигнала С триггеры регистра находятся в режиме хранения информации, зафиксированной при прохождении предыдущего положительного фронта импульса С.

а |

б |

Рис. 5.26. Структура - а и условное обозначение регистра 1533ИР38 - б

Микросхема 1533ИР38 содержит два одинаковых четырехразрядных регистра, построенных на синхронных D- триггерах с тремя состояниями выхода. Логическая структура одного регистра и условное графическое обозначение ИР38 приведена на рис. 5.26. Каждый регистр имеет четыре входа и выхо-

да, входR, тактовый вход С и вывод E0 для управления Z- состоянием выхо-

дов. Если на вывод E0 подать уровень лог.1, то выходные буферы окажутся в третьем (разомкнутом) состоянии. Обнуление регистров происходит при по-

даче на вход R низкого уровня напряжения.

Данные со входов Di поступят на выходы Qi при поступлении переднего фронта (перепад 0/1) тактового импульса на вход С.

5.9. Сдвигающие регистры

Сдвигающие регистры представляют собой цепочку последовательно стоящих триггеров, логически определенным образом связанных между собой. Сдвигающие регистры могут выполнять следующие операции: сдвиг ин-

183

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

формации вправо; сдвиг информации влево; прием информации последовательным или параллельным кодом; хранение.

Сдвиг информации заключается в том, что цифра хранившаяся в i-ом разряде регистра до сдвига, после каждого тактового импульса передается в (i+1) – й разряд при сдвиге вправо, или в соседний (i-1) – й разряд – при сдвиге влево. На функциональных схемах регистры обозначаются буквенным символом RG. Под символом ставится стрелка, указывающая направление сдвига:вправо, влево, двунаправленный (реверсивный). Выше указывалось, что понятие ”весовых коэффициентов” к разрядам регистра не применяются и вес каждого разряда считается равным единице или определяется записанной

врегистр информацией.

5.9.1Последовательный регистр сдвига вправо

Принципиальными особенностями такого регистра являются: информационные входы каждого последующего триггера соединены с входами предыдущего, синхронизирующие входы триггеров объединены, вход начальной установки регистров общий. На рис. 5.27. приведена схема четырехразрядного сдвигающего регистра с последовательным вводом, выполненного на универсальных JK-триггерах, например K555TB6.

а б Рис. 5.27. Четырехразрядный сдвигающий регистр с последовательным вводом:

а – функциональная схема; б – условное изображение

Первый триггер при помощи инвертора включен по схеме D-триггера и служит для приема входной информации по входу D. К исходному состоянию, когда все триггеры выключены, регистр приводится с помощью импульса начальной установки нулевого уровня У0, подаваемого на вход R. Пусть на вход D первого триггера установлен уровень лог.1. С приходом первого после У0 тактирующего импульса ТИ произойдет запись единицы в первый триггер. Уровень 1 на прямом выходе Q1 этого триггера устанавится после прохождения заднего фронта ТИ (перепад 1/0) через время tз (рис. 5.28.), определяемого быстродействием данного типа триггера. Содержимое второго, третьего и четвертого триггеров при этом не изменится, т.к. во время прохождения среза первого ТИ, на выходах первого, второго и третьего триггеров был низкий уровень.

Допустим, к приходу второго тактового импульса ТИ2 на входе первого триггера установлен нуль, тогда после второго тактового импульса на выходе Q1 будет нуль, на выходе Q2 – лог. 1, на выходах Q3, Q4 будут по прежнему

184

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

низкие уровни напряжения. Пусть в третьем tз и четвертом тактах на вход первого триггера поступает единица. Третий тактирующий импульс запишет эту единицу в первый триггер, а нуль с выхода Q1 запишется во второй триггер. Единица с выхода Q2 перепишется в третий триггер, а четвертый триггер останется в нулевом состоянии. Четвертый ТИ запишет входную единицу в первый триггер, включит второй триггер и выключит третий, единицу с выхода Q3 перепишет в четвертый триггер.

Цифровой код, поступившей на вход первого триггера в виде 1-0-1-1, установится на выходах триггеров Q1 – Q4 в виде 1-1-0-1. Первая поступившая на вход D 1 за четыре такта продвинулась в четвертый триггер, вторая цифра 0 за три оставшихся такта продвинулась в третий триггер и т.д.

Рис. 5.28. Временные диаграммы последовательного регистра

На временных диаграммах (рис. 5.6.) видно, что сдвиг первой входной единицы на одну позицию вправо происходит с приходом каждого тактового импульса. После четвертого такта входная цифровая последовательность 1011 установится на выходах Q4 – Q1 в виде параллельного кода, который может быть считан внешним устройством.

5.9.2. Реверсивный регистр

Последовательный регистр сдвига влево, выполненный на триггерах типа – D, тактируемых фронтом показан на рис. 5.29. Цифровая информационная последовательность поступает на вход D крайнего правого триггера W и снимается с выхода Q1 крайнего левого триггера.

с выхода Q1 крайнего левого триггера.

Рис. 5.29. Четырехразрядный сдвигающий регистр влево с последовательным вводом

185

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Работает данный регистр аналогично вышеописанному регистру сдвига вправо. Только запись и сдвиг информации происходит в момент прохождения переднего фронта тактового импульса ТИ сдвиг происходит справа налево.

Реверсивный сдвигающий регистр можно построить на JK-триггерах или триггерах типа D с использованием дополнительных логических ячеек 2И-2И-ИЛИ “исключающее или”. На рис. 5.30. приведена принципиальная схема трехразрядного реверсивного сдвигающего регистра, собранного на триггерах типа D, тактируемых фронтом.

Рис. 5.30. Функциональная схема реверсивного сдвигающего регистра

При подаче управляющего сигнала V = 1 происходит прием информации со входа D1 и сдвиг информации слева направо при поступлении каждого синхроимпульса на вход ТИ. Благодаря наличию инвертора в управляющей

Параллельный ввод

|

D0 |

DD5.1 |

D1 |

DD5.2 |

D2 |

DD5.3 |

D3 |

DD5.4 |

|

|

|

& |

|

& |

|

& |

|

& |

|

|

|

|

DD1 |

|

DD2 |

|

DD3 |

|

DD4 |

|

S |

S |

TT |

S |

TT |

S |

TT |

S |

TT |

|

D |

Q |

D |

Q |

D |

Q |

D |

Q |

|

|

Вход |

||||||||

|

C |

|

C |

|

C |

|

C |

|

|

|

|

|

|

|

|

||||

C |

& |

R |

|

R |

|

R |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

& |

|

& |

|

& |

|

S/P |

1 |

DD6.1 |

DD6.2 |

DD6.3 |

DD6.4 |

||||

|

|

|

|

|

|

|

|

||

Рис. 5.31. Регистр с параллельным и последовательным вводом

цепи V нижние логические ячейки И схем “исключающего ИЛИ” отключены. При изменении уровня управляющего сигнала V с единичного уровня на ну-

186

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

левой, происходит изменение режима работы регистра на “сдвиг влево”. Теперь запрещена работа верхних ячеек И схемы “исключающего ИЛИ” и запись информации будет происходить по входу Q4, на который можно подавать информацию с четвертого триггера или любого другого источника, а сдвиг информации будет происходить справа налево.

Регистр сдвига с параллельным и последовательным вводом информации и последовательным ее выводом, показан на рис. 5.31. В схеме использованы двухступенчатые D-триггеры с записью информации по входу D фронтом 1/0 тактового импульса S и принудительной асинхронной установкой триггера в состояние 1или 0 сигналами Sa = 0 и Ra = 0.

Последовательный ввод информации происходит при высоком уровне сигнала s/p (последовательно – параллельно). При этом нулевой уровень сигнала устанавливается на общих входах ячеек DD5.1-DD5.4 и DD6.1 – DD6.4 и работа этих ячеек запрещена. С приходом каждого фронта тактирующего импульса на вход С происходит запись информации со входа S и сдвиг ее на один шаг вправо. Благодаря инвертору DD7 тактирование происходит по фронту 0/1 тактовых импульсов. При низком уровне сигнала s/p регистр переводится в режим асинхронной параллельной загрузки по входам D0-D3.

5.10. Кольцевые регистры-счетчики

Кольцевые регистры (счетчики) строятся на основе обычных сдвигающих регистров, выполненных на JK-триггерах или триггерах D-типа. Особенность кольцевых регистров заключается в том, что выход регистра определенным образом связан с входом регистра. Число триггеров объединенных в кольцо может выбрано произвольным. В зависимости от способа задания обратной связи различают два типа кольцевых регистров: регистр сдвига единицы и кольцевой счетчик

5.10.1. Кольцевой регистр сдвига единицы

Особенностью логической структуры кольцевого регистра сдвига единицы является то, что при приведении регистра к исходному состоянию один из триггеров цепочки устанавливается в единичное состояние, а остальные сбрасываются в нуль. При этом вводится прямая обратная связь между выходом последнего триггера и входом первого. Логическая структура трехразрядного кольцевого регистра сдвига единицы, выполненного на универсальных JK- триггерах, приведена на рис. 5.32.

К исходному состоянию регистр приводится низким уровнем напряжения подаваемым на входы начальной установки триггеров. Первый и второй триггеры приводятся к исходному нулевому состоянию, а в третий триггер записывается логическая единица. Тактирующие импульсы подаются на входы С всех триггеров одновременно.

Первый, после окончания сигнала начальной установки (“НУ”, “Пуск”), тактирующий импульс переписывает единицу с выхода последнего триггера в первый. Действительно, на управлющих входах первого триггера J = 1, К = 0,

187

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

что соответствует режиму «управление единицей». Третий триггер при этом обнуляется, т. к. на управляющий вход J подавался низкий уровень напряжения с выхода второго триггера, что соответствует режиму «управление нулем». Второй триггер остается в исходном состоянии, поскольку на его входе J был нулевой уровень. Второй тактирующий импульс сдвигает информацию на один шаг вправо и т. д. Временные диаграммы, поясняющие работу трехразрядного регистра сдвига единицы, приведены на рис.5.33.

Нетрудно заметить, что в отличие от двоичных счетчиков на выходе кольцевого регистра сдвига единицы получаем позиционный код без помощи дешифратора, что является его достоинством. Подобным образом можно строить пятеричные, шестеричные, восьмеричные и десятичные счетчики. Каждый из выходов приходит в активное состояние с частотой = вх / n, где n – число триггеров в кольце. Следовательно, коэффициент счета численно равен числу триггеров. Для построения десятичного счетчика требуется десять триггеров, что в 2,5 раза больше чем у двоичного счетчика. Это приводит к увеличению экономических и энергетических затрат, что является основным недостатком кольцевых регистров (счетчиков).

|

|

|

Q1 |

|

Q2 |

Q3 |

|

Q4 |

|

|

DD1 |

|

DD2 |

|

DD3 |

|

DD4 |

|

S |

TT |

S |

TT |

S |

TT |

S |

TT |

C |

J |

Q |

J |

Q |

J |

Q |

J |

Q |

C |

|

C |

|

C |

|

C |

|

|

|

|

|

|

|

||||

|

K |

Q |

K |

Q |

K |

Q |

K |

Q |

|

R |

|

R |

|

R |

|

R |

|

Пуск

Рис. 5.32. Принципиальная схема кольцевого регистра сдвига единицы

К достоинствам регистра можно отнести максимальное быстродействие,

Рис. 5.33. Временные диаграммы кольцевого регистра сдвига единицы

определяемого только скоростью переключения применяемых триггеров. На каждом выходе сигналы имеют одинаковую задержку относительно такти-

188

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

рующих импульсов, равную времени задержки переключения одного триггера.

5.10.2 Кольцевые счетчики

Кольцевой счетчик, часто именуемый счетчиком Джонсона, обладает высоким быстродействием, как и кольцевой регистр, но имеет коэффициент счета Ксч = 2n, что делает его более экономичным. Отличия в построении кольцевого счетчика от кольцевого регистра заключаются в следующем. Во-первых,

Рис. 5.34. Принципиальная схема пятиразрядного кольцевого счетчика

все триггеры счетчика приводятся к одному нулевому состоянию. Во-вторых, обратная связь делается перекрестной: инверсный выход последнего триг-

гера Q соединяется с управляющим входом J первого триггера, а прямой выход Q последнего триггера подключается ко входу К первого (перекрестная обратная связь). При построении кольцевого счетчика на триггерах типа D c

динамическим управлением выход Q соединяется со входом D входного триггера. На рис. 5.34. приведена схема пятиразрядного кольцевого счетчика.

Перед пуском счетчик приводится к исходному состоянию путем подачи сигнала низкого уровня на входы R всех триггеров. При этом на выходе Q последнего триггера установится уровень лог 1, который поступит на вход D первого триггера. После окончания сигнала начальной установки первый тактирующий импульс переведет в единичное состояние первый триггер, остальные триггеры сохранят предыдущее состояние. Второй импульс переведет в единичное состояние второй триггер, причем первый триггер сохранит предыдущее состояние. Так будет продолжаться до прихода пятого импульса (говорят, что по счетчику распространяется волна единиц). После пятого им-

пульса ситуация изменится на обратную: на выходе Q установится лог 0. Теперь с приходом каждого тактирующего импульса по счетчику будет продвигаться волна нулей. На приведенном рисунке сигналы на прямых выходах триггеров показаны жирными линиями. Сигналы на инверсных выходах показаны пунктирными линиями, чтобы исключить возможную путаницу.

Достоинством кольцевого счетчика является то, что состояние 01 или 10 для двух соседних триггеров в течение одного цикла бывает только один раз независимо от длины счетчика. Это позволяет дешифрировать любое состоя-

189

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

ние с помощью простых двухвходовых логических элементов 2И либо 2ИЛИНЕ (на основании правила де-Моргана). Следует отметить, что на выходах дешифрирующих ячеек не возникают ложные пики, обусловленные различными величинами задержек сигналов в разных разрядах, поскольку в каждом такте только один триггер меняет свое состояние. В качестве примера на рис.5.35 приведена диаграмма выделенного четвертого такта Q4Q5.

Рис. 5.35 - Временные диаграммы кольцевого счетчика

Общий недостаток кольцевых структур заключается в том, что любой сбой (случайное включение какого-либо триггера) будет существовать сколь угодно долго, т. е. не самоустраняются. Для устранения сбоев разработаны различные варианты логических цепей коррекции обратной связи.

Микросхема К564ИЕ19 – пятиразрядный кольцевой счетчик (Джонсона) с предварительной установкой каждого разряда по входам S1S5 (рис. 5.36).

Микросхема имеет информационный вход D, |

|

|

|

|

|

|

|

|

|||||

вход тактовый С, вход установки нуля R, входы |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

разрешения предварительной установки каждого |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

разряда S1 - S5, вход разрешение предваритель- |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

ной установки ES, инверсные выходы первого – |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

пятого разрядов ( |

|

- |

|

). Логический уровень |

|

|

|

|

|

|

|

|

|

Q1 |

Q5 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||||

на входе разрешения предварительной установки |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

ES высокий. Счетчик имеет вход установки R, |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||||

при подаче на который напряжения высокого |

Рис. 5.36. Условное |

||||||||||||

уровня все разряды счетчика устанавливаются в |

|||||||||||||

графическое обозначение |

|||||||||||||

состояние высокого уровня независимо от со- |

|||||||||||||

|

К564ИЕ19 |

||||||||||||

стояния уровня на остальных входах. |

|

||||||||||||

|

|

|

|

|

|

|

|

||||||

190

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)