Схемотехника / Учебники и методички / potehin

.pdf

состояние импульсом "Начальной установки" (Нач. уст.). Затем, с помощью сигнала "Запись", триггер Dl переводится в единичное состояние, и тактирующие импульсы начинают загрузку слагаемых А и В в регистры RG-1 и RG- 2, начиная с младших разрядов. После окончания загрузки на входе сумматора выставлены биты a0 и b0 и и сигнал переноса P0 = 0, при этом на выходе сумматора установится результат суммы S0 и сигнал переноса P1.

С помощью сигнала "Сумма", устройство переводится в режим побитного арифметического сложения чисел А и В. При этом тактирующие импульсы ТИ поступают на все три регистра одновременно и на триггер запоминания переноса. По окончании суммирования результат зафиксирован в выходном регистре RG-3, а сигнал переноса в триггере памяти D9.

Рассматриваемое устройство при незначительных изменениях позволяет реализовать самые разнообразные схемы работы.

Недостатком последовательных сумматоров является невысокое быстродействие. Максимальное время суммирования такой схемы tсум = n t0, где t0 - период следования тактовых сигналов, a n – разрядность слагаемых. Кроме того, при таком построении невозможно осуществление циклического переноса, т.е. прибавление единицы переноса из старшего разряда в младший разряд суммы.

Параллельный сумматор

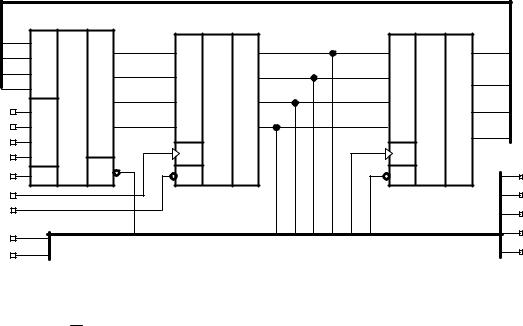

Параллельный сумматор комбинационного типа строится на основе каскадного соединения одноразрядных комбинационных сумматоров. Они могут выполняться с последовательным, параллельным и групповым переносом.

Сумматор с поразрядным последовательным переносом параллельного действия состоит из отдельных разрядов, каждый из которых содержит одно-

разрядный полный сумматор (рис. 4.52.). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

В сумматоре этого типа перенос рас- |

a0 |

|

|

|

|

|

pi |

SM |

|

Si |

|

|

|

S0 |

|||

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|||||||||||

пространяется последовательно от разряда |

|

|

|

|

|

ai |

|

Pi+1 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

к разряду по мере образования суммы в |

b0 |

|

|

|

|

|

bi |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

каждом отдельном разряде. При наиболее |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

pi |

SM |

|

Si |

|

|

|

S1 |

||||

неблагоприятных |

условиях перенос про- |

a1 |

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||||||||

изойдет во всех разрядах слагаемых. Мак- |

|

|

|

ai |

|

Pi+1 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||||||

b1 |

bi |

|

|

|

|

|

|||||||||||

симальное время переноса составит |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

tперен = n t1, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a2 |

|

|

|

|

pi |

SM |

|

Si |

|

|

|

S2 |

|||

|

|

|

|

|

|

|

|

|

|

||||||||

где t1-время формирования переноса в |

|

|

|

|

|

|

|

|

|||||||||

|

|

ai |

|

Pi+1 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|||||||||||

одном разряде, |

|

|

b2 |

|

|

bi |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||||

n – число разрядов сумматора. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Данный тип |

сумматора |

наиболее |

an |

|

|

|

|

pi |

SM |

|

Si |

|

|

|

Sn |

||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|||||||||||

прост с точки зрения построения схемы и |

|

ai |

|

Pi+1 |

|

|

|

|

|||||||||

|

|

|

|

|

|

||||||||||||

bn |

bi |

|

|

|

|

Pn |

|||||||||||

|

|

|

|

||||||||||||||

цепей переноса, но имеет сравнительно не- |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

высокое быстродействие. |

|

Рис. 4.52. Параллельный сумматор |

|||||||||||||||

Типичным представителем |

комбина- |

с последовательным переносом |

|||||||||||||||

ционного сумматора с последовательным |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

151 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

переносом является четырехразрядный сумматор К155ИМЗ.

4.6.3. Параллельный перенос

Уменьшение времени распространения переноса осуществляется за счет формирования ускоренного или параллельного переноса на основе выраже-

ния: |

Pi+1 = Gi pi Ti. |

|

Перенос для первого разряда сформируется как |

|

P1 = G0 p0 T0. |

|

где G0 = a0 b0, T0 = a0 b0, p0 – входной перенос. |

|

На выходе второго разряда перенос равен |

|

P2 = G1 P1 T1. |

|

Подставим в последнее выражение значение P1 и получим |

|

P2 = G1 (G0 p0 T0) T1 = G1 G0 T1 T1T0 p0. |

|

Для переноса в третьем разряде по аналогии получим следующее выра- |

жение:

P3 = G2 P2 T2 = G2 (G1 G0 T1 T1T0 p0) T2 = = G2 G1 T2 G0 T2T1 T2T1T0 p0.

На выходе четвертого разряда сигнал переноса равен

P4 = G3 P3 T3 = G3 (G2 G1 T2 G0 T2T1 T2T1T0 p0) T3 = = G3 G2T3 G1T3T2 G0T3T2T1 T3T2T1T0 p0.

Особенностью полученных выражений является то, что входящие в них Gi и Ti, формируются одноразрядными сумматорами одновременно во всех разрядах.

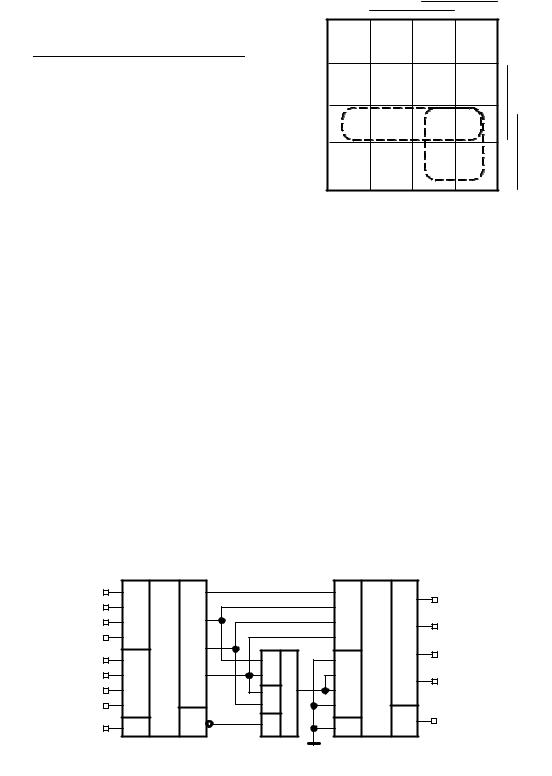

Ускоренный перенос реализован в четы- |

11 |

|

|

|

|

|

|

|||||||

|

A4 |

SM |

|

|

|

|||||||||

рехразрядном |

двоичном |

полном сумматоре |

|

|

|

|

||||||||

12 |

|

B4 |

P4 |

|

9 |

|||||||||

|

|

|||||||||||||

К555ИМ6 (рис.4.53.). |

|

|

|

15 |

|

A3 |

|

S4 |

|

10 |

||||

Результаты на выходах суммы и перено- |

|

|

|

|||||||||||

|

|

|

||||||||||||

14 |

|

B3 |

|

|

|

|

||||||||

|

|

|

|

|

||||||||||

са описываются следующими выражениями: |

2 |

|

|

|

S3 |

|

13 |

|||||||

A2 |

|

|||||||||||||

|

|

|

||||||||||||

|

|

|||||||||||||

SA,B p0 |

A1 B1 2(A2 |

B2) 4(A3 B3) |

3 |

|

B2 |

|

|

|

|

|||||

|

|

|

|

|

||||||||||

|

|

S2 |

1 |

|||||||||||

S 1S 4S |

2 |

8S |

3 |

16P . |

6 |

|

A1 |

|

||||||

|

|

|

|

|

||||||||||

1 |

1 |

|

|

|

4 |

5 |

|

B1 |

|

S1 |

|

4 |

||

причем знак плюс – символ арифметической |

|

|

|

|||||||||||

|

|

|||||||||||||

7 |

|

P0 |

|

|

|

|

||||||||

операции. |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Микросхема может быть использована |

Рис. 4.53. Условное обозна- |

для операций с числами, представленными как |

чение 1531ИМ6 |

в положительной, так и в отрицательной логике |

|

(когда единица кодируется низким уровнем напряжения). В режиме положительной логики вход P0 нельзя оставлять открытым. Если первый разряд ис-

пользуется как полусумматор, на входе P0 устанавливают потенциалU0. Взаимная перестановка входов одинакового разряда не меняет режим работы сумматора. При наращивании разрядности сумматора выход P4 соединяется со входом P0 более старшего разряда.

152

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Четырехразрядный сумматор К555 ИМ6 можно использовать в качестве вычитателя. Операция вычитания выполняется путем сложения уменьшаемого с вычитаемым, взятым в дополнительном коде.

При большом числе разрядов слагаемых затраты на оборудование сумматора с параллельным переносом становятся настолько велики, что их реализация становится нецелесообразной. Поэтому сумматоры объединяют в группы, например, по четыре разряда. Перенос между группами – групповой перенос – можно осуществлять либо последовательным, либо параллельным методом.

4.6.4. Накапливающий 4-х разрядный двоичный сумматор

Функциональная схема накапливающего сумматора приведена на рис. 4.54. Она включает один четырехразрядный комбинационный сумматора D1 и два регистра D2, D3. В качестве комбинационных сумматоров могут быть взяты микросхемы К155ИМЗ, К555ИМ6, выполняющие операцию суммирования двух четырехразрядных двоичных чисел A и B с учетом переноса из предыдущего разряда P0 и формирующие перенос P4 в последующий разряд. В качестве запоминающих регистров могут быть взяты микросхемы К555ТМ8 или

1 |

A |

DD1 |

S |

DD2 |

|

|

|

DD3 |

1 |

|

|

|

|

|

|

|

|

||||

|

0 |

|

|

|

D0 RG Q0 |

|

||||

2 |

A1 |

SM |

0 |

D0 RG |

Q0 |

|

||||

3 |

A2 |

|

S1 |

D |

Q |

D |

1 |

|

2 |

|

4 |

A3 |

|

S2 |

1 |

1 |

|

Q1 |

|

|

|

|

D2 |

Q2 |

D2 |

3 |

|

|||||

b0 |

B0 |

|

Q2 |

|

||||||

|

S3 |

|

||||||||

b1 |

B1 |

|

D |

Q3 |

D |

Q3 |

4 |

|

||

b2 |

B2 |

|

|

3 |

|

|

3 |

|

||

b3 |

B3 |

|

P4 |

C |

|

C |

|

0 |

|

|

p0 |

P0 |

|

R |

|

R |

|

Q |

|||

C1 |

|

|

|

|

1 |

0 |

||||

|

|

|

|

|

|

|

|

Q1 |

||

R1 |

|

|

|

4 |

3 2 1 0 5 6 |

|

|

|

2 |

Q2 |

|

5 |

|

|

|

|

|

3 |

|||

C2 |

|

|

|

|

|

|

Q3 |

|||

R2 |

6 |

|

|

|

|

|

|

|

4 |

P4 |

Рис. 4.54. Функциональная схема 4-х разрядного накапливающего сумматора

К555ТМ9, представляющие собой набор четырех и шести триггеров с общим входом сброса R и синхронизации С. Установка триггеров в нулевое состояние производится низким уровнем сигнала на входе R. При этом выполняется микрооперация очистки регистров:

Y1: RG1(4) := 0; Y2: RG2(4) := 0.

Синхровходы С служат для записи информации установленной на входах Dl, D2, D3, D4 регистров, т.е. выполняют микрооперации

Y3: RG1(4) := S1; Y4: RG2(4) := RG1(4).

На первом этапе производится очистка регистров, и на вход первого сумматора устанавливается первое слагаемое A0. Сумматор выполняет функцию сложения:

D1: S1= RG2(4) + А(4),

153

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

где А(4) – слагаемое А, поступившее на вход сумматора,

RG2(4) – слагаемое B, поступившее на вход сумматора с выхода второго регистра.

Поскольку регистры перед началом суммирования были обнулены, слагаемое B равно нулю и, следовательно, первая сумма будет равна

D1: S1= 0 + А(4) = А(4).

С помощью тактового импульса Ти1 запишем первый результат в регистр D1. Результат суммирования теперь доступен для чтения в виде пятиразрядного выходного кода Dl, D2, D3, D4,P4 на выводах устройства. Тактовым импульсом Ти2 перепишем первый результат во второй регистр RG2(4).

На втором шаге будет произведено суммирование второго операнда А(4) с первой суммой S1, в результате чего получим вторую промежуточную сумму S2. Суммирование можно продолжать до переполнения сумматора, т.е. появления 1 на выходе P4.

Пример. С помощью сигнала начальной установки УО приведем регистры в нулевое состояние. На вход первого сумматора D1 подадим какое-либо двоичное число, например, А0 =710 =01112. Число В0, подаваемое с выхода регистра D4, равно нулю, следовательно, на выходе D1 будет сумма А0 + В0, равная S0 = 01112. С помощью тактирующих импульсов ТИ1 и ТИ2 перепишем сумму на выход второго регистра D3. Теперь на входах В4 сумматора установится двоичное число 01112 =710.

Установим на входе сумматора новое число А, например, А1 = 510 = 01012. На выходе сумматора появится число S1 = А1 + В1 = 1210 = 110010. Вновь запишем результат в первый регистр и зафиксируем его на выходе устройства.

На третьем шаге к полученной сумме прибавим третье число, например, А2 = 810. В результате суммирования на выходе получим пятиразрядное число S2 = А2 + В2 = 2010 = 1 110010, в котором единица в старшем разряде P4 указывает на переполнение разрядной сетки.

4.6.4. Суммирование двоично-десятичных чисел

Особенность суммирования десятичных чисел, представленных двоичнодесятичными кодами, связана с тем, что перенос из старшего разряда младшей тетрады в старшую, должен происходить при N ≥ 9, а не при N ≥ 15 как было при двоичном суммировании. При N ≥ 9 к полученному результату необходимо прибавить 610 (двоичный код 0110). Прибавить число 610 можно с помощью дополнительного сумматора. Причем определять, когда следует прибавлять корректирующий и когда делать этого не надо, должен специальный узел

– схема коррекции. В таблице на рис. 4. 55. а указаны коды, требующие коррекции, даны их двоичные эквиваленты и номера минтермов.

Выражение для сигнала коррекции имеет вид;

Yк = M10 M11 M12 M13 M14 M15, где M10 ÷ M15 = S3S’2 S1S’0 ÷ S3S2S1 S0.

154

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Нанесем на карту Карно функцию Yк (рис. 4.40, б) на карту Карно и проведем минимизацию. Единицы функции опишутся двумя контурами:

Избыточные коды

N S3S2S1S0 Минтерм

10 |

1 0 1 0 |

M10 |

11 |

1 0 1 1 |

M11 |

12 |

1 1 0 0 |

M12 |

13 |

1 1 0 1 |

M13 |

14 |

1 1 1 0 |

M14 |

15 |

1 1 1 1 |

M15 |

|

|

|

S0 |

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

3 |

0 |

2 |

|

|

|

|

|

|

||||

0 |

4 |

0 |

5 |

0 |

7 |

0 |

6 |

S2 |

1 |

|

1 |

|

1 |

15 |

1 |

14 |

|

12 |

13 |

|

|

S3 |

||||

0 |

|

0 |

|

1 |

1 |

|

||

8 |

9 |

10 |

|

|||||

|

|

|

11 |

|

|

|||

а б

Рис. 4.55. а – Таблица кодов, требующих корректировки; б карта минимизации корректирующей функции

Yк = S3 S2 S3 S1.

Высокий уровень на выводе двоичного переноса P4 также указывает на необходимость коррекции, с учетом этого окончательное выражение:

Yк = S3 S2 S3 S1 P4.

Схема сумматора, с узлом коррекции, собранном по выведенному выражению, приведена на рис. 4.41.

Пример. Установим на вход число = 710 = 01112 и число B = 610 = = 01102. На выходе первого сумматора образуется сумма = 11012. На выводах сумматора S3 и S2 высокие уровни и, следовательно на выходе корректирующего узла тоже высокий уровень. Это означает, что на входах второго сумматора установлен код коррекции B = 610 = 01102, на входе А этого сумматора число 1310. Результат на выходе второго сумматора число S2 = 1910 = 1 00112,

a0 |

|

DD1 |

|

|

|

DD2 |

|

|

A0 |

S0 |

|

A0 |

SM S0 |

s0 |

|||

a1 |

A |

SM |

|

A |

|

|||

a |

1 |

S1 |

|

|

1 |

S1 |

s1 |

|

2 |

A2 |

|

|

A2 |

||||

a3 |

A3 |

S2 |

|

A3 |

S2 |

s2 |

||

b0 |

B0 |

& |

B0 |

|||||

|

||||||||

b1 |

B1 |

S3 |

1 |

B1 |

S3 |

s3 |

||

b2 |

B2 |

|

& |

B2 |

|

|

||

b3 |

B3 |

|

B3 |

P4 |

p4 |

|||

p0 |

P0 |

P4 |

1 |

P0 |

||||

Рис. 4.56. Функциональная схема сумматора с десятичной коррекцией

который представлен в виде десятичного переноса p4 = 1 и четырехразрядного числа суммы S = 310 = 00112,

4.6.5. Суммирование чисел со знаками

155

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Суммирование чисел со знаками производят с использованием обратных или дополнительных кодов. Рассмотрим вариант построения сумматора двух четырехразрядных чисел и B(4). Знак числа принято указывать в старшем бите (требуется дополнительный пятый разряд). Положительное число в пятом разряде кодируется 0, отрицательное число 1. Мы выберем модифифицированные коды, когда под знак отдаются два старших разряда:

A6 A5 = 00 – число положительное, A6 A5 = 11 – число отрицательное. Пример. Заданы числа A10 = 910 и B10 = 1210, необходимо просуммировать их со знаками = (+A + B), S2 = (+A – B), S3 = (– A + B), S4 = (–A – B). Прямой код положительного числа Aпр = 00 10012, обратный код отрицательного числа

Aобр = 11 10012, аналогично для числа B: Bпр = 00 11002, Bобр = 11 00112,

Возможные варианты результатов суммирования. |

|

Таблица 4.12. |

|||||||

S1 = (+ A + B) |

S2 = (+ A – B) |

S3 = (– A + B) |

S4 = (– A – B) |

||||||

Aпр |

00 1001 |

Aпр |

00 1001 |

Aобр |

11 0110 |

Aобр |

11 0110 |

||

Bпр |

00 1100 |

Bобр |

11 0011 |

Bпр |

00 1100 |

Bобр |

11 0011 |

||

S1 |

01 0101 |

S2 |

11 1100 |

S3 |

1 00 0010 |

S4 |

1 10 1001 |

||

|

|

|

|

|

00 |

0011 |

|

10 |

1001 |

Инверсия |

|

|

11 0011 |

|

|

|

|

11 1010 |

|

Ответ |

+ 2110 |

|

– 310 |

|

+ 310 |

|

|

– 2110 |

|

Примечание. Стрелкой обозначен циклический перенос |

|

|

|

||||||

Проанализируем полученные результаты.

1. При суммировании чисел с одинаковыми знаками (S1, S4) возможно переполнение разрядной сетки. Если бы под знак оставляли один разряд, то в первом случае (S1) при суммировании положительных чисел получили бы от-

рицательное число 1 01012 (–510). Во втором случае при суммировании отрицательных чисел получили бы +510.

2. При переполнении разрядной сетки единицу переполнения необходимо циклически прибавить к младшему разряду суммы (S3, S4)

Эти особенности будут учтены при разработке сумматора чисел со знаками.

В связи с тем , что отрицательные числа необходимо инвертировать. Воспользуемся замечательным свойством логического элемента «неравнозначность» (XOR) инвертировать аргумент A в зависимости от уровня (низкий

– высокий) аргумента B. В таблице истинности «исключающее ИЛИ» (неравнозначность) показано, что при b = 0 сигнал a проходит на выход не меняясь, при b = 1 сигнал a инвертируется. Это говорит о том, что данный логический элемент можно применить для преобразования кода числа в обратный код. Предлагаемый вариант функциональной схемы сумматора двоичных чисел со знаками приведен на рис. 4.57.

Числа A и B подаются на входы сумматора через ЛЭ «неравнозначность», на второй управляющий вход которого подается сигнал знака (0,1). Выходные сигналы суммы передаются на выход также через ЛЭ «неравнозначность», знак выходного сигнала снимается со старшего разряда (S5). Выход перепол-

156

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

нения разрядной сетки P5 соединен со входом P0 младшего разряда для выполнения функции циклического переноса.

|

|

|

|

|

|

Знак A |

=1 |

B |

|

|

=1 |

|

|

|

|

|

|

|

|

a0 |

0 |

SM |

Q0 |

||||

|

b |

|

a |

|

YN |

=1 |

B |

S0 |

|||||

|

|

|

a1 |

1 |

|

||||||||

|

0 |

|

0 |

|

0 |

=1 |

|

|

|

=1 |

|

||

|

|

|

a2 |

B2 |

|

Q1 |

|||||||

|

0 |

|

1 |

|

1 |

=1 |

B3 |

|

S1 |

||||

|

|

|

a3 |

|

=1 |

Q |

|||||||

|

1 |

|

0 |

|

1 |

|

B |

4 |

|

||||

|

1 |

|

1 |

|

0 |

|

|

|

|

S2 |

2 |

||

|

|

|

Знак B |

|

B5 |

|

|

||||||

|

|

|

|

|

|

=1 |

|

=1 |

Q |

||||

|

|

|

|

|

|

|

B |

|

|

|

|||

|

|

|

a |

|

|

b0 |

0 |

|

S |

3 |

|||

|

|

|

|

|

=1 |

B |

|

3 |

|

||||

a0 |

|

|

|

|

|

b1 |

1 |

|

=1 |

P4 |

|||

& |

|

|

|

|

=1 |

B |

|

||||||

1 |

|

a |

=1 |

b2 |

2 |

|

S4 |

||||||

b |

|

N1 |

=1 |

|

|

|

|

||||||

0 |

& |

|

b |

N1 |

b |

B3 |

|

S |

|

||||

a0 |

|

|

|

3 |

|

B4 |

|

|

|||||

b0 |

|

|

|

|

|

|

|

|

5 |

|

|||

|

|

|

|

|

|

|

B5 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

P5 |

|

|||

|

б |

|

|

|

в |

|

|

P0 |

|

|

|||

Рис.4.57. а – таблица истинности логической неравнозначности; б – функциональная схема и условное обозначение ЛЭ; в – функциональная схема сумматора двоичных четырехразрядных чисел со знаками

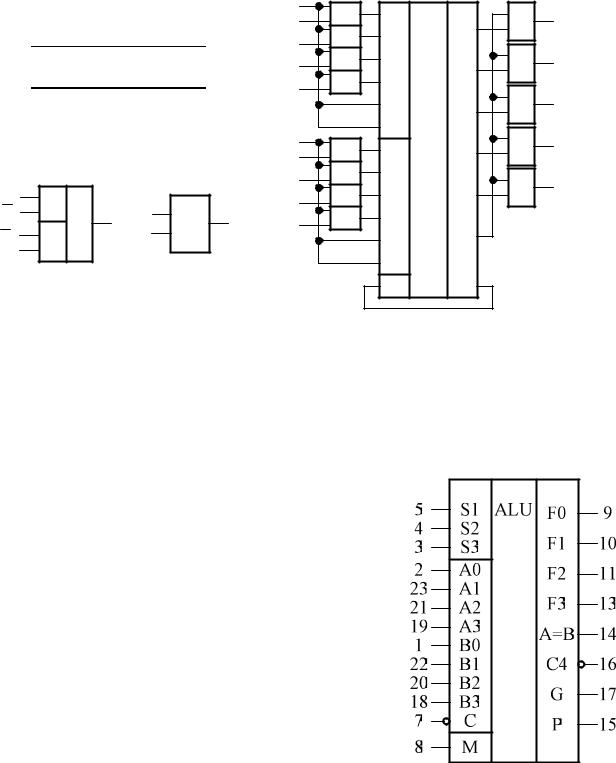

4.6.6. Арифметическо-логические устройства

Арифметическо-логические устройства (АЛУ) – это специализированные микросхемы, выполняющие в соответствии с программой на входах арифметические или ло-

гические преобразования двоичной информации

гические преобразования двоичной информации

(рис. 4.58.). В микро процессорной технике АЛУ являются базовыми элементами – они используются в сочетании с регистрами памяти и сдвига,

оперативными запоминающими устройствами и другими цифровыми узлами. АЛУ, принадлежащие к разным типам логик (ТТЛ, ТТЛШ, КМОП,

ЭСТЛ), функционально во многом совпадают, в том числе и по разводке выводов.

Микросхема К555ИП3 предназначена для действий с двумя четырехразрядными двоичны-

ми слоями : А = А3А2А1А0 и В = В3В2В1В0. Конкретный вид операции, выполняемой микросхемой, задается 5-разрядным кодом на выходах

МS3S2S1S0. Всего это АЛУ способно выполнить 25 = 32 операции: 16 логических и 16 арифмети-

ческих и арифметико-логических. Операции сложения и вычитания проводятся с ускоренным переносом из разряда в разряд. Кроме того, имеется вход приема сигнала переноса С.

157

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)