Схемотехника / Учебники и методички / potehin

.pdf

нажатии соответствующих кнопок 0 ÷ 9 (четыре столбца «Выходного кода» – Q3-Q2-Q1-Q0).

Решение задачи в общем виде в случае для восьми переменных представляется весьма трудной задачей. Однако, можно заметить что исходная функция принимает единичное значение в каждой строке всего лишь один раз, что упрощает решение задачи.

Судя по таблице 4.1, логическая единица на выходе Q3 получается в случае, если логически просуммировать аргументы x8, x9:

Q3 = x8 x9.

По аналогии запишем остальные выражения:

Q2 = x7 x6 x5 x4;

Q1 = x7 x6 x3 x2; (4.1)

Q0 = x9 x7 x5 x3 x1.

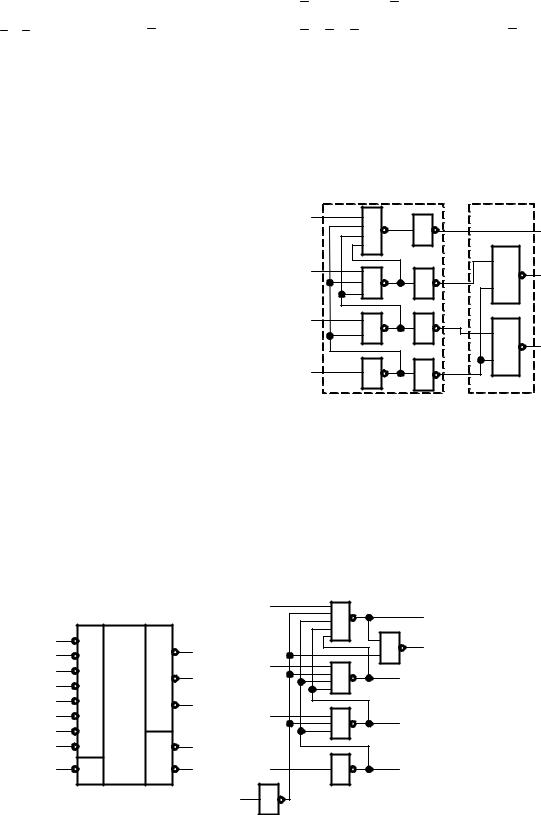

Для реализации данного шифратора требуется четыре ЛЭ логическое ИЛИ, как показано на рис. 4.2, а. Судя по схеме, входной сигнал x0 не участвует в формировании выходного кода. Отсутствие сигнала на любом из выходов Q3 ÷ Q1 указывает на то, что установлен нулевой набор. На рис. 4.2, б представлено условное графическое обозначение шифратора, аббревиатура шифратора CD (от англ. ENCODER).

Второй вид структурной схемы шифратора получим, если управляющие входные сигналы имеют нулевой активный уровень.

Можно, не строя таблицы истинности, преобразовать я полученные ранее выражения для выходных сигналов по правилу отрицания. Получим:

Q3 = x8 x9 ;

Q2 x2 x3 x6 x7 ;

х9 х8 х7 х6 х5 х4 х3 х2 х1 х0

|

|

|

|

|

|

|

|

|

1 |

|

Q0 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

Q1 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

Q2 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

Q3 а |

|

|

|||

|

|

|

||

|

|

|

Q3 = x4 x5 x6 x7 ;

Q2 = x1 x3 x5 x7 x9 .

х1 |

CD Q0 |

х1 |

CD Q0 |

х2 |

х2 |

||

х3 |

Q1 |

х3 |

Q1 |

х4 |

х4 |

||

х5 |

Q2 |

х5 |

Q2 |

х6 |

х6 |

||

х7 |

Q3 |

х7 |

Q3 |

х8 |

х8 |

||

х9 |

|

х9 |

|

|

б |

|

в |

Рис. 4.2. Функциональная схема шифратора – а, условное графическое обозначение с высокими активными уровнями напряжений на входах и выходах

– б, УГО с активными низкими уровнями – в

Устройство реализуется на четырех логических элементах И-НЕ, при этом входные и выходные сигналы инвертированы. Условное обозначение шифра-

101

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

тора, управляемого нулевыми уровнями напряжений по входам и низкими активными уровнями на выходах приведено на рис. 4.2, в.

Структуры шифраторов, приведенные на рис. 1 и 3, предназначены для обработки зависимых однопозиционных сигналов, когда из всех клавиш должна быть нажата только одна (клавиатура ПК или сотового телефона и т. д.). При нажатии нескольких клавиш одновременно на выходе шифратора получается код, соответствующий операции "поразрядное ИЛИ" над кодами отдельных клавиш и выходной код искажается. Такая ситуация в большинстве случаев неприемлема.

Если одновременно действуют несколько активных однопозиционных сигналов, то они называются независимыми. Например, сигналы запросов на прерывание от периферийных устройств, взаимодействующих с микропроцессором. Для обработки независимых однопозиционных сигналов применяют приоритетные шифраторы, в которых различным одновременно действующим сигналам присваивается приоритет. Часто полагают, что входные сигналы с большим индексом обладают большим приоритетом, реже – наоборот.

4.1.1. Приоритетные шифраторы

Приоритетные шифраторы имеют более сложную архитектуру и могут быть выполнены по двум структурам:

схема выделения старшего сигнала и обычный шифратор;

приоритетный шифратор как единое устройство.

Таблица 4.2

N |

|

Входной код |

|

Выходной код |

||||||

x3 |

|

x2 |

x1 |

|

x0 |

f3 |

f2 |

f1 |

f0 |

|

0 |

0 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

2 |

0 |

|

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

3 |

0 |

|

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

4 |

0 |

|

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

5 |

0 |

|

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

6 |

0 |

|

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

7 |

0 |

|

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

8 |

1 |

|

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

9 |

1 |

|

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

Схема выделения старшего сигнала имеет K входов и столько же выходов и работает по следующему алгоритму: из нескольких активных входных сигналов на выход этой схемы передается только один активный сигнал, имеющий наивысший приоритет, а все остальные активные сигналы с меньшим приоритетом передаются на выход как неактивные. Выделенный один активный сигнал далее легко может быть преобразован в двоичный код обычным шифратором.

Рассмотрим простой пример, когда по приоритету надо расставить четыре сигнала х3, х2, х1, х0 образующих десять комбинаций 9 ÷ 0 (табл. 4.2). Ак-

102

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

тивным уровнем является 1, старшим сигналом должен быть х3. Выходным сигналам дадим название fi.

Логические выражения для yi имеют вид: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

f3 = х3 ; |

f2 = |

x |

3 |

х2 = |

x3 |

x |

2 |

; |

(4.2) |

||||||||||||

f1 = |

x |

3 |

x |

2 х1 = |

x3 x2 |

x |

1 |

; |

f0 = |

x |

3 |

|

x |

2 |

x |

1 х0 = |

x3 x2 x1 |

x |

0 |

. |

|||||

Судя по правой части таблицы в каждой строке выделяется старший сигнал, из имеющихся в данном наборе.

Схемы, реализующие приведенные уравнения типа, называются дейзицепочками и используются для аппаратной обработки сигналов запроса на

прерывание. |

|

|

|

|

|

|

|

|

|

|

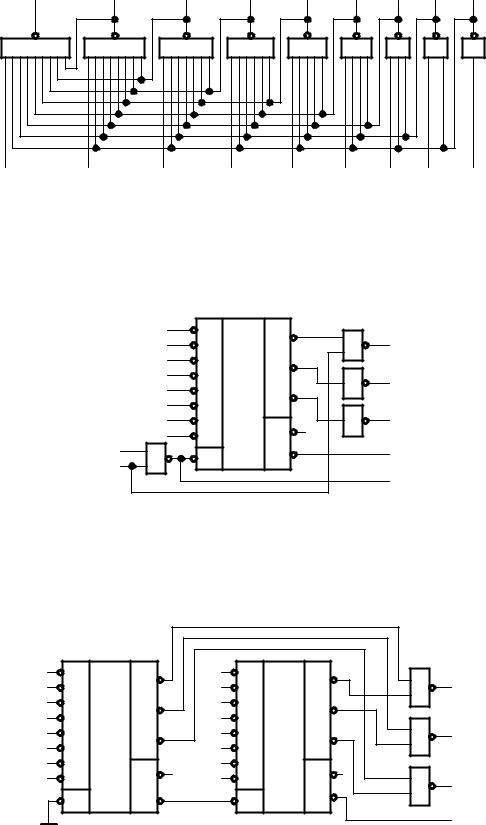

На рис. 4.3. в качестве примера при- |

|

Выделение |

|

|

Шифратор |

|||||

ведено |

функциональное |

изображение |

|

старшего разряда |

|

|||||

двухступенчатого приоритетного шифра- |

x0 |

& |

I |

1 |

f0 |

II |

||||

тора для четырех переменных. Первая |

|

|

|

Q0 |

||||||

ступень |

осуществляет |

расстановку при- |

x1 |

|

|

|

f1 |

1 |

||

оритетов, согласно выражениям (4.1). |

& |

|

1 |

|||||||

|

|

Q1 |

||||||||

Вторая ступень – собственно двухразряд- |

|

|

|

|

|

|

||||

ный шифратор. Выполнен шифратор по |

x2 |

& |

|

1 |

f2 |

1 |

||||

выражениям (4.0), из |

которых удалены |

|

|

|

|

|

||||

избыточные переменные (х9 ÷ х4): |

|

|

|

|

f3 |

Q2 |

||||

|

& |

|

1 |

|

||||||

|

|

|

Q0 = x3 x1: Q1 = x3 |

|

|

|

||||

x3 x2; |

|

|

|

|

|

|

|

|||

|

|

(4.3) |

|

|

Рис. 4.3. Структурная схема |

|||||

Следует отметить, что данный |

|

|||||||||

двухступенчатого приоритетного |

||||||||||

приоритетный |

шифратор |

невозможно |

|

|

шифратора |

|||||

использовать |

для |

|

наращивания |

|

|

|||||

|

|

|

|

|

|

|

||||

разрядности из-за отсутсвия расширяющих входов и выходов.

Рассмотрим функционирование приоритетного шифратора, у которого приоритетность заложена в функциональной схеме. Условное обозначение шифратора, обрабатывающего восемь входных сигналов, приведено на рис. 4.4. а.

К555ИВ1 |

x0 |

& |

|

E0 |

|

|

|

||||

0 |

PRCD 1 |

|

|

& |

GS |

1 |

x1 |

|

|

||

2 |

2 |

& |

|

f1 |

|

3 |

|

|

|

||

|

|

|

|

|

|

4 |

4 |

x2 |

& |

|

|

5 |

|

|

f2 |

||

6 |

|

|

|

|

|

7 |

GS |

|

& |

|

|

EI |

EO |

x3 |

|

f3 |

|

|

EI |

1 |

|

б |

|

|

а |

|

|

|

|

Рис. 4.4. Структурная схема приоритетного шифратора – а; функциональная схема, поясняющая принцип формирования сигналов расширения разрядности – б

103

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Прежде всего, отметим, что все входы и выходы этой ИС имеют в качестве активного сигнала низкий уровень, то есть логический ноль. Здесь обозначено:

I0-I7 – входные сигналы, причем сигнал с большим индексом имеет больший приоритет.

Вход ЕI (Епаblе Input – разрешение по входу) при активном уровне 0 разрешает работу ИС, а при неактивном уровне 1 формирует на всех выходах неактивные уровни 1. Этот сигнал служит для наращивания числа обрабатываемых информационных входов.

Выход ЕО (Епаblе Output – разрешение по выходу) служит для наращивания числа обрабатываемых информационных входов. Если на входы ИС не поступает ни одного активного сигнала, то значение выхода ЕО устанавливается равным 0.

Выход GS (Сrоuр Signal – групповой сигнал) принимает активное значение 0, если на входах данной ИС имеется хотя бы один активный сигнал, то есть GS выполняет функцию осведомительного сигнала о том, что на входах приоритетного шифратора есть сигнал.

Исходя из сказанного, можно оформить таблицу (табл. 4), иллюстрирующую работу такого приоритетного шифратора, где крестиком обозначены безразличные значения сигналов.

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 4.2 |

||

N |

EI |

I7 |

I6 |

I5 |

I4 |

I3 |

I2 |

I1 |

I0 |

EO |

GS |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

X |

X |

X |

X |

X |

X |

1 |

0 |

1 |

1 |

0 |

2 |

0 |

1 |

1 |

0 |

X |

X |

X |

X |

X |

1 |

0 |

1 |

0 |

1 |

3 |

0 |

1 |

1 |

1 |

0 |

X |

X |

X |

X |

1 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

1 |

0 |

0 |

1 |

1 |

5 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

1 |

0 |

0 |

1 |

0 |

6 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

1 |

0 |

0 |

0 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

8 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

9 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

Запишем уравнения для выходных сигналов в СКНФ и проведем необходимые преобразования по правилу де Моргана.

EO = EI + I7 +I6 +I5 +I4 +I3 +I2 +I1+I0 = EI +

I7 I6 I5 I4 I3 I2 I1 I0 = EI (I7 I6 I5 I4 I3 I2 I1 I0 );

Z = (I7 + I6 + I5 + I4 + I3 + I2 + I1 + I0) = I7 I6 I5 I4 I3 I2 I1 I0 ; (4.4) = EI + EI (I7 I6 I5 I4 I3 I2 I1 I0);

GS = EI EO ; |

Q0 = EI (I7 I6 I5 I6 I4 I3 I6 I4 I2 I1). |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 = |

|

( |

|

|

|

I5I4 |

|

I5I4 |

|

); |

Q2 = |

|

( |

|

|

|

|

|

|

|

); |

||

EI |

I7 |

I6 |

I3 |

I2 |

EI |

I7 |

I6 |

I5 |

I4 |

||||||||||||||

104

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

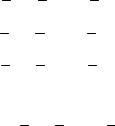

Функциональная схема шифратора, построенная по данным выражениям (без демонстрации сигналов EO и GS) представлена на рис. 4.5. Нетрудно убе-

f0 |

f1 |

f2 |

f3 |

f4 |

f5 |

f6 |

f7 |

f8 |

|

|

|

|

|

|

|

|

|

& |

& |

& |

& |

& |

& |

& |

& |

& |

x0 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 x7 |

x8 |

Рис. 4.5. Функциональная схема приоритетного шифратора

диться, что увеличение числа входов к существенному усложнению схемы. В связи с этим на практике реализуются шифраторы на 3 – 4 разряда.

По приведенным уравнениям выпускаются ИС приоритетного шифратора

8 3: SN74LS148, К555ИВ1.

|

0 |

0 |

PRCD 1 |

& |

A0 |

|

1 |

1 |

|||

|

2 |

2 |

2 |

|

|

|

3 |

3 |

1 |

A1 |

|

|

|

||||

|

4 |

4 |

4 |

|

|

|

5 |

5 |

1 |

|

|

|

6 |

6 |

GS |

A2 |

|

8 |

7 |

7 |

|

|

|

& |

EI |

EO |

|

Z |

|

9 |

|

|

|

|

A3 |

|

|

|

|

|

Рис 4.6. Схема увеличения разрядности

В качестве примера на рис. 4.6 показан принцип увеличения разрядности восьмивходового шифратора до десятивходового.

Сигналы 8 и 9 блокируют входы младших разрядов, подавая низкий уро-

I8 |

0 |

PRCD 1 |

I0 |

0 |

PRCD 1 |

& |

|

I9 |

1 |

I1 |

1 |

A0 |

|||

I10 |

2 |

2 |

I2 |

2 |

2 |

|

|

I11 |

3 |

I3 |

3 |

|

|

||

|

|

& |

|

||||

I12 |

4 |

4 |

I4 |

4 |

4 |

A1 |

|

I13 |

5 |

I5 |

5 |

|

|||

|

|

|

|

||||

I14 |

6 |

GS |

I6 |

6 |

GS |

|

|

I15 |

7 |

I7 |

7 |

& |

A2 |

||

|

EI |

EO |

|

EI |

EO |

|

A3 |

|

|

|

|

|

|

|

Рис 4.7. Схема увеличения разрядности в два раза.

вень сигнала на вход EI. Также сигналы 8 и 9 формируют четвертый разряд, а

105

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

сигнал 9, через логический элемент И-НЕ формирует двоичный код на выходе дешифратора равный девяти. Выход EO служит для определения наличия входных сигналов.

На рис. 4.7 представлен вариант наращивания разрядности шифраторов, позволяющий удвоить число входов.

Выход ЕО ИС, обрабатывающей сигналы, имеющие больший приоритет, соединяется со входом ЕI ИС, обрабатывающей сигналы, имеющие меньший приоритет. Если на входы ИС, обрабатывающей сигналы с большим приоритетом, не поступает ни одного активного сигнала, то значение выхода EO устанавливается равным 0 и, тем самым, разрешается обработка входных сигналов с меньшим приоритетом, поступающих на соответствующие ИС. Наличие одного любого активного сигнала на входах ИС, обрабатывающей сигналы с большим приоритетом, автоматически запирает все ИС, обрабатывающие сигналы с меньшим приоритетом. Старший выходной разряд шифратора берется с выхода EO шифратора с меньшим приоритетом.

4.2. Дешифраторы

4.2.1. Основные положения

Дешифратором называется комбинационное цифровое устройство с несколькими входами и выходами, у которого каждой комбинации входных сигналов соответствует активное значение только одного определённого выходного сигнала. Дешифраторы широко используются для преобразования двоичных кодов в управляющие сигналы различных цифровых устройств. Они используются в качестве коммутаторов распределителей информационных каналов и синхроимпульсов, для организации адресной логики в запоминающих устройствах, при выводе символов на печать, для преобразования двоично-десятичного кода в десятичный при управлении цифровыми индикаторами и т.д.

Переключательные функции полного дешифратора имеют следующий вид:

y0 xm 1xm 2 ...x1x0 ; y1 xm 1xm 2 ...x1x0 ; y2 xm 1xm 2 ...x1x0 ;

..................................

yN 1 xm 1xm 2 ...x1x0 .

Если число входных равно m, то максимально возможное число выходных шин равно N, где N = 2m, и такой дешифратор называется полным. Различные способы вычисления конъюнкций дают возможность получать разнообразные структуры дешифраторов: линейные, прямоугольные, матричные, пирамидальные. Рассмотрим принцип построения линейного дешифратора.

106

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Линейные дешифраторы

Таблица истинности трёхвходового полного дешифратора с нулевыми активными значениями входных сигналов y представлена в таблице 4.3.

Таблица 4.3

N |

|

Вход |

|

Выход |

|

|

|

|

|

|

|

|

|

x3 |

x2 |

x1 |

y0 |

|

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

2 |

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

3 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

4 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

5 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

6 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

7 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Значения выходных переменных определяется следующими логическими выражениями:

y0 |

x |

3 |

x |

2 |

x |

1 , |

y1 |

x |

3 |

x |

2 x1 , |

y2 |

x |

3x2 |

x |

1 , |

y3 |

x |

3x2 x1 , |

|||||||

y4 |

x3 |

x |

2 |

x |

1 |

, |

y5 |

x3 |

x |

2 x1 |

, |

y6 |

x3x2 |

x |

1 |

, |

y7 |

x3x2 x1 |

. |

|||||||

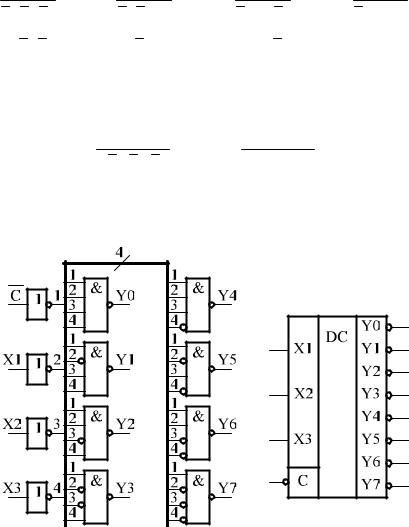

Реализуется такой дешифратор на восьми трёхвходовых ячейках И-НЕ.

С целью расширения функциональных возможностей заведём на вход каждой ячейки управляющий сигнал С. Логические функции входных сигналов при этом будут выглядеть следующим образом:

y0 cx3 x2 x1 , ÷ y7 c x3 x2 x1 .

Структура устройства реализующего данные функции приведена на рисунке

4.8, а.

a |

б |

Рис. 4.8. Функциональная схема – a; условное графическое изображение дешифратора – б

107

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Особенности данной схемы характерны для дешифраторов в интегральном исполнении. Входные сигналы инвертируются в самом дешифраторе, что уменьшает общее число входов, увеличивает входное сопротивление и уменьшает входную ёмкость. Вторая ступень – линейный дешифратор выполнен на восьми четырёхвходовых ячейках И-НЕ.

При высоком уровне стабилизирующего сигнала C дешифратор переходит в неактивное состояние, на всех его входах устанавливается лог. 1, поскольку на вход каждой логической ячейки поступает его инверсное значение, равное лог. 0. В связи с этим на вход C может быть возложена функция управления или выбора кристалла CS .

Вход C можно использовать в качестве информационного. Последовательный двоичный код, подаваемый на вход С, будет поступать на выход, определяемый входным адресом. Дешифратор при этом именуется демультиплексором («дешифратор-демультиплексор»).

При наращивании разрядности дешифратора на вход C подаётся инверсное значение старшего разряда адреса x4.

4.2.2. Ступенчатые дешифраторы

Принцип построения ступенчатых дешифраторов рассмотрим на примере построения дешифратора 4х16. Переключательные функции полного дешифратора с высоким активным уровнем на выходе выглядят следующим образом.

y0 |

x |

4 |

|

x |

3 |

x |

2 |

x |

1 , |

y4 |

x |

4 x3 |

x |

2 |

x |

1, |

y8 x4 |

x |

3 |

x |

2 |

x |

1 , |

y12 x4 x3 |

x |

2 |

x |

1, |

||||||||||||||||

y1 |

x |

4 |

x |

3 |

x |

2 x1 , |

y5 |

x |

4 x3 |

x |

2 x1 , |

y9 x4 |

x |

3 |

x |

2 x1 , |

y13 x4 x3 |

x |

2 x1 , |

|||||||||||||||||||||||||

y2 |

x |

4 |

x |

3x2 |

x |

1, |

y6 |

x |

4 x3x2 |

x |

1 , |

y10 x4 |

x |

3x2 |

x |

1, |

y14 x4 x3x2 |

x |

1, |

|||||||||||||||||||||||||

y3 |

x |

4 |

x |

3x2 x1 , |

y7 |

x |

4 x3x2 x1, |

y11 x4 |

x |

3x2 x1 , |

y15 x4 x3x2 x1 . |

|||||||||||||||||||||||||||||||||

Разобьем входные переменные x4, x3, x2, x1, весовые значения которых 8- 4-2-1 соответственно, на пары: x4, x3 и x2, x1 (при чём допускается любой другой вид разбивки). Каждую пару переменных используем для построения двухвходового линейного дешифратора первой ступени преобразования. В результате получим:

a0 |

x |

4 |

x |

3 , |

a1 |

x |

4 x3 , |

a2 x4 |

x |

3 , |

a3 x4 x3 , |

|||||||

b0 |

x |

2 |

x |

1 , |

b1 |

x |

2 x1 , |

b2 x2 |

x |

1, |

b3 x2 x1 . |

|||||||

Переменные y0-y15 получим на второй ступени преобразования путем логического перемножения переменных a0-a3 на b0-b3:

y0 a0 b0 , |

y4 a1 b0 , |

y8 a2 b0 , |

y12 a3 b0 , |

y1 a0 b1 , |

y5 a1 b1, |

y9 a2 b1, |

y13 a3 b1 , |

y2 a0 b2 , |

y6 a1 b2 , |

y10 a2 b2 , |

y14 a3 b2 , |

y3 a0b3 , |

y7 a1 b3 , |

y11 a2 b3 , |

y15 a3 b3 . |

108

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

На рисунке 4.9, а приведена функциональная схема двухступенчатого преобразователя, а на рисунке 4.9, б его условное графическое изображение. Функциональная схема содержит инверторы для переменных x4,…,x1, восемь двухвходовых ячеек И на первой ступени преобразования 16 во второй. Такую структуру преобразования иногда называют прямоугольной, а вторую ступень

– матричным преобразователем.

a |

б |

Рис. 4.9. Ступенчатый дешифратор на четыре входа: структурная схема a; условное обозначение б

Пирамидальные дешифраторы

Отличительной особенностью пирамидальной структуры построения дешифраторов является то, что на каждой ступени преобразования добавляется всего лишь одна переменная. Если входных переменных n, то число ступеней преобразования n – 1. Например, для четырёхвходового дешифратора на первой ступени преобразования получим функции двух переменных а0,…, а3, как в ступенчатом дешифраторе. На второй ступени преобразования переменные а0,…,а3 перемножим с входом переменной x2 , x2 и получим восемь проме-

жуточных сигналов: |

|

|

|

|

|

|

|

||||

b0 a0 |

x |

2 , |

b1 a0 x2 , |

b2 a1 |

x |

2 , |

b3 a1 x2 , |

||||

b4 a2 |

x |

2 , |

b5 a2 x2 , |

b6 a3 |

x |

2 , |

b7 a3 x2 . |

||||

На третьей, последней ступени преобразования сигналы b0,…,b7 умножаются на переменную x1,x1 , в результате чего оказываются сформированными все

входные сигналы:

y0 b0 |

x |

1 , |

y1 b0 x1, |

y2 b1 |

x |

1 , |

y3 b1 x1 ,…, |

y7 b3 x1 , |

||

y8 b4 |

x |

1 , |

y9 b4 x1 , |

y10 b5 |

x |

1 , |

y11 b5 x1 ,…, |

y15 b7 x1 . |

||

109

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)

Основным недостатком ступенчатых дешифраторов является увеличенная задержка распространения сигнала.

4.2.3. Формирование логических функций

Дешифраторы можно использовать в качестве узла комбинационных схем при формировании логических функций.

Пример 1. На базе дешифратора 3:8 реализовать 3-х аргументную переключательную функцию, заданную таблицей истинности, приведенной на рис. 4.10, а. Cудя по таблице, исходная функция представляет сумму пяти минтер-

мов: F = M1 M2 M3 M5 M7.

Поскольку рассматриваемая функция зависит от трех аргументов, то она может быть реализована с помощью двоично-десятичного дешифратора 3:8. В связи с тем, сигналы на выходе дешифратора инвертированы, то справедливо следующее соотношение (правило отрицания):

F = M0 M1 M3 M4 M6 M7 = М0 M1 М3 M4 M6 M7 .

Подключим указанные выходы дешифратора со входами 8-ми входового вентиля И-НЕ и на его выходе сформируется указанная функция. Функциональная схема устройства приведена на рис. 4. 10, б.

Управляющие сигналы E1,E2, E3 связаны между собой конъюнктивно и дешифратор переходит в активное состояние при Е1 = 0, Е2 = 0, Е3 = 1. При любых других сочетаниях этих сигналов выходы дешифраторов переходят в неактивное состояние с высокими выходными уровнями напряжения.

В том случае, когда число единиц в выходной функции меньше числа нулей, на выходе дешифратора предпочтительнее использовать логическую схему ИЛИ.

Учитывая, что количество нулей в заданной выходной функции (два) заметно меньше числа единиц (шесть) целесообразно реализовать инверсную функцию (сумму нулей). По таблице нетрудно заключить, что

F = М2 M5 .

М |

|

Входы |

F |

|

|

|

Y0 |

|

|

|

x3 |

x2 |

x1 |

|

|

1 |

DC |

& |

|

0 |

0 |

0 |

0 |

1 |

A |

Y1 |

|||

1 |

0 |

0 |

1 |

1 |

|

|

|

Y2 |

|

B |

2 |

|

Y3 |

F |

|||||

2 |

0 |

1 |

0 |

0 |

|

||||

|

4 |

|

Y4 |

||||||

3 |

0 |

1 |

1 |

1 |

C |

|

Y5 |

|

|

4 |

1 |

0 |

0 |

1 |

|

|

|

Y6 |

|

5 |

1 |

0 |

1 |

0 |

|

|

|

Y7 |

|

6 |

1 |

1 |

0 |

1 |

а |

|

|

|

б |

7 |

1 |

1 |

1 |

1 |

|

|

|

||

Рис. 4.10. а – Таблица истинности; б – cхемная реализация функции

Причем эта функция тождественно равна заданной:

110

Print to PDF without this message by purchasing novaPDF (http://www.novapdf.com/)