- •Челябинск

- •2002 Предисловие

- •От издательства

- •Часть 1 Операционные системы и среды

- •Глава 1 Основные понятия Понятие операционной среды

- •Понятия вычислительного процесса и ресурса

- •Диаграмма состояний процесса

- •Реализация понятия последовательного процесса в ос

- •Процессы и треды

- •Прерывания

- •Основные виды ресурсов

- •Классификация операционных систем

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 2 Управление задачами и памятью в операционных системах

- •Планирование и диспетчеризация процессов и задач Стратегии планирования

- •Дисциплины диспетчеризации

- •Вытесняющие и не вытесняющие алгоритмы диспетчеризации

- •Качество диспетчеризации и гарантии обслуживания

- •Диспетчеризация задач с использованием динамических приоритетов

- •Память и отображения, виртуальное адресное пространство

- •Простое непрерывное распределение и распределение с перекрытием (оверлейные структуры)

- •Распределение статическими и динамическими разделами

- •Разделы с фиксированными границами

- •Разделы с подвижными границами

- •Сегментная, страничная и сегментно-страничная организация памяти

- •Сегментный способ организации виртуальной памяти

- •Страничный способ организации виртуальной памяти

- •Сегментно-страничный способ организации виртуальной памяти

- •Распределение оперативной памяти в современных ос для пк

- •Распределение оперативной памяти вMs-dos

- •Распределение оперативной памяти вMicrosoftWindows95/98

- •Распределение оперативной памяти вMicrosoftWindowsNt

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 3 Особенности архитектуры микропроцессоровi80x86

- •Реальный и защищённый режимы работы процессора

- •Новые системные регистры микропроцессоров i80x86

- •Адресация в 32-разрядных микропроцессорахi80х86 при работе в защищённом режиме Поддержка сегментного способа организации виртуальной памяти

- •Поддержка страничного способа организации виртуальной памяти

- •Режим виртуальных машин для исполнения приложений реального режима

- •Защита адресного пространства задач

- •Уровни привилегий для защиты адресного пространства задач

- •Механизм шлюзов для передачи управления на сегменты кода с другими уровнями привилегий

- •Система прерываний 32-разрядных микропроцессоровi80x86

- •Работа системы прерываний в реальном режиме работы процессора

- •Работа системы прерываний в защищённом режиме работы процессора

- •Обработка прерываний в контексте текущей задачи

- •Обработка прерываний с переключением на новую задачу

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 4 Управление вводом/выводом и файловые системы

- •Основные понятия и концепции организации ввода/вывода в ос

- •Режимы управления вводом/выводом

- •Закрепление устройств, общие устройства ввода/вывода

- •Основные системные таблицы ввода/вывода

- •Синхронный и асинхронный ввод/вывод

- •Кэширование операций ввода/вывода при работе с накопителями на магнитных дисках

- •Функции файловой системы ос и иерархия данных

- •Структура магнитного диска (разбиение дисков на разделы)

- •Файловая системаFat

- •Структура загрузочной записиDos

- •Файловые системыVfaTиFat32

- •Файловая система hpfs

- •Файловая система ntfs (New Technology File System)

- •Основные возможности файловой системы ntfs

- •Структура тома с файловой системой ntfs

- •Возможности файловой системыNtfSпо ограничению доступа к файлам и каталогам

- •Основные отличияFaTи ntfs

- •Контрольные вопросы и задачи Вопросы для проверки

- •Задания

- •Глава 5 Архитектура операционных систем и интерфейсы прикладного

- •Принцип функциональной избирательности

- •Принцип генерируемости ос

- •Принцип функциональной избыточности

- •Принцип виртуализации

- •Принцип независимости программ от внешних устройств

- •Принцип совместимости

- •Принцип открытой и наращиваемой ос

- •Принцип мобильности (переносимости)

- •Принцип обеспечения безопасности вычислений

- •Микроядерные операционные системы

- •Монолитные операционные системы

- •Требования, предъявляемые к ос реального времени

- •Мультипрограммность и многозадачность

- •Приоритеты задач (потоков)

- •Наследование приоритетов

- •Синхронизация процессов и задач

- •Предсказуемость

- •Принципы построения интерфейсов операционных систем

- •Интерфейс прикладного программирования

- •Реализация функцийApIна уровне ос

- •Реализация функцийApIна уровне системы программирования

- •Реализация функцийApIс помощью внешних библиотек

- •Платформенно-независимый интерфейс posix

- •Пример программирования в различныхApiос

- •Текст программы дляWindows(WinApi)

- •Текст программы дляLinux(posixapi)

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 6 Проектирование параллельных взаимодействующих вычислительных процессов

- •Независимые и взаимодействующие вычислительные процессы

- •Средства синхронизации и связи при проектировании взаимодействующих вычислительных процессов

- •Использование блокировки памяти при синхронизации параллельных процессов

- •Возможные проблемы при организации взаимного исключения посредством использования только блокировки памяти

- •Алгоритм Деккера

- •Синхронизация процессов посредством операции «проверка и установка»

- •Семафорные примитивы Дейкстры

- •Мьютексы

- •Использование семафоров при проектировании взаимодействующих вычислительных процессов

- •Задача «поставщик – потребитель»

- •Пример простейшей синхронизации взаимодействующих процессов

- •Решение задачи «читатели – писатели»

- •Мониторы Хоара

- •Почтовые ящики

- •Конвейеры и очереди сообщений Конвейеры (программные каналы)

- •Очереди сообщений

- •Примеры создания параллельных взаимодействующих вычислительных процессов

- •Пример создания многозадачного приложения с помощью системы программированияBorlandDelphi

- •Пример создания комплекса параллельных взаимодействующих программ, выступающих как самостоятельные вычислительные процессы

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 7 Проблема тупиков и методы борьбы с ними

- •Понятие тупиковой ситуации при выполнении параллельных вычислительных процессов

- •Примеры тупиковых ситуаций и причины их возникновения

- •Пример тупика на ресурсах типаCr

- •Пример тупика на ресурсах типаCRиSr

- •Пример тупика на ресурсах типаSr

- •1: P(s2); 5: p(s1);

- •Формальные модели для изучения проблемы тупиковых ситуаций

- •Сети Петри

- •Вычислительные схемы

- •Модель пространства состояний системы

- •Методы борьбы с тупиками

- •Предотвращение тупиков

- •Обход тупиков

- •Обнаружение тупика

- •Обнаружение тупика посредством редукции графа повторно используемых ресурсов

- •Методы обнаружения тупика по наличию замкнутой цепочки запросов

- •Алгоритм обнаружения тупика по наличию замкнутой цепочки запросов

- •Контрольные вопросы и задачи Вопросы для проверки

- •Глава 8 Современные операционные системы

- •Семейство операционных системUnix Общая характеристика семейства операционных систем unix, особенности архитектуры семейства осunix

- •Основные понятия системыUnix

- •Виртуальная машина

- •Пользователь

- •Интерфейс пользователя

- •Привилегированный пользователь

- •Команды и командный интерпретатор

- •Процессы

- •Функционирование системыUnix

- •Выполнение процессов

- •Подсистема ввода/вывода

- •Перенаправление ввода/вывода

- •Файловая система

- •Структура файловой системы

- •Защита файлов

- •Межпроцессные коммуникации вUnix

- •Сигналы

- •Семафоры

- •Программные каналы

- •Очереди сообщений

- •Разделяемая память

- •Вызовы удаленных процедур (rpc)

- •Операционная системаLinux

- •Семейство операционных систем os/2WarpкомпанииIbm

- •Особенности архитектуры и основные возможности os/2Warp

- •Особенности интерфейса os/2Warp

- •Серверная операционная система os/2Warp4.5

- •Сетевая ос реального времениQnx

- •Архитектура системыQnx

- •Основные механизмы qnx для организации распредёленных вычислений

- •Контрольные вопросы и задачи Вопросы для проверки

- •Приложение а Тексты программы параллельных взаимодействующих задач

- •Приложение б Тексты программ комплекса параллельных взаимодействующих приложений

- •Текст программы а

- •Текст программы в

- •Текст программы d

- •Текст программы g

- •Список литературы

- •Часть 1 6

- •Глава 5 Архитектура операционных систем и интерфейсы прикладного 240

- •Глава 6 Проектирование параллельных взаимодействующих вычислительных 279

- •Глава 7 Проблема тупиков и методы 348

- •Глава 8 Современные операционные 391

Новые системные регистры микропроцессоров i80x86

Основные регистры микропроцессора i80x86, знание которых необходимо для понимания защищённого режима работы, приведены на рис. 3.2. Следует обратить внимание на следующее:

указатель команды EIP– 32 битовый регистр, младшие 16 разрядов этого регистра есть регистрIP;

регистр флагов EFLAGS– 32 бита, младшие 16 разрядов представляют регистрFLAGS;

регистры общего назначения ЕАХ, ЕВХ. ЕСХ, EDX, а такжеESP, ЕВР,ESI,EDI– 32-битовые, однако их младшие 16 разрядов представляют собой известные регистрыAX,BX,CX,DX,SP, ВР,SI,DI;

сегментные регистры CS,SS,DS,ES,FS,GS– 16-битовые. При каждом из регистровCS,SS,DS,ES,FS,GSизображены пунктиром скрытые от программистов (недоступны никому, кроме собственно микропроцессора) 64-битовые регистры, в которые загружаются дескрипторы соответствующих сегментов;

регистр-указатель на локальную таблицу сегментов текущей задачи – LDTR(16 битов). При этом регистре также имеется «теневой» (скрытый от программиста) 64-битовый регистр, в который микропроцессор заносит дескриптор, указывающий на таблицу дескрипторов сегментов задачи, описывающих её локальное виртуальное адресное пространство;

регистр-указатель задачи TR1(16 битов). Указывает на дескриптор в глобальной таблице дескрипторов, позволяющий получить доступ к дескриптору задачиTSS2– информационной структуре, которую поддерживает микропроцессор для управления задачами;

регистр GDTR1(48 битов) глобальной таблицыGDT, содержащей как дескрипторы общих сегментов, так и специальные системные дескрипторы. В частности, в GDTR находятся дескрипторы, с помощь которых можно получить доступ к сегментамTSS;

регистр IDTR(48 битов) таблицы дескрипторов прерываний.

Содержит информацию, необходимую

для доступа к «таблице прерываний»IDT;

регистр IDTR(48 битов) таблицы дескрипторов прерываний.

Содержит информацию, необходимую

для доступа к «таблице прерываний»IDT;

управляющие регистры CR0 –CR3 (32-битовые) и некоторые другие регистры.

Управляющий регистр CR0 содержит целый ряд флагов, которые определяют режимы работы микропроцессора. Подробно об этих флагах можно прочитать в книгах [2, 22, 48]. Мы же просто ограничимся тем фактом, что самый младший бит (РЕ,protectenable) этого регистра определяет режим работы процессора. При РЕ=0 процессор функционирует в реальном режиме работы, а при единичном значении микропроцессор переключается в защищённый режим. Самый старший бит регистра CR0 (битPG,paging) определяет, включен (PG=l) или нет (PG=0) режим страничного преобразования адресов.

Регистр CR2 предназначен для размещения в нем адреса подпрограммы обработки страничного исключения, то есть в случае использования страничного механизма отображения памяти обращение к отсутствующей странице будет вызывать переход на соответствующую подпрограмму диспетчера памяти, и для определения этой подпрограммы будет задействован регистр CR2.

Регистр CR3 содержит номер физической страницы, в которой располагается таблица каталогов таблиц страниц текущей задачи. Очевидно, что, приписав к этому номеру нули, мы попадем на начало этой страницы.

Адресация в 32-разрядных микропроцессорахi80х86 при работе в защищённом режиме Поддержка сегментного способа организации виртуальной памяти

Как мы уже знаем, для организации эффективной и надёжной работы вычислительной системы в мультипрограммном режиме необходимо иметь соответствующие аппаратные механизмы, поддерживающие независимость адресных пространств каждой задачи и в то же время позволяющие организовать обмен данными и разделение кода. Для этого желательно выполнение следующих двух требований:

чтобы у каждого вычислительного процесса могло быть свое собственное (личное, локальное) адресное пространство, которое никак не может пересекаться с адресными пространствами других задач;

чтобы существовало общее (разделяемое) адресное пространство.

Поэтому в микропроцессорах i80x86 реализован сегментный способ организации распределения памяти. Помимо этого, в этих микропроцессорах может быть задействована и страничная трансляция. Поскольку для каждого сегмента нужен дескриптор, устройство управления памятью поддерживает соответствующую информационную структуру. Формат дескриптора сегмента приведен на рис. 3.3.

Поля дескриптора (базовый адрес, поле предела) размещены в дескрипторе не непрерывно, а в разбивку, во-первых, из-за того, что разработчики постарались минимизировать количество перекрестных соединений в полупроводниковой структуре микропроцессора, а во-вторых – вследствие необходимости обеспечить полную совместимость1микропроцессоров (предыдущий микропроцессор i80286 работал с 16-битовым кодом и тоже поддерживал сегментный механизм реализации виртуальной памяти). Необходимо заметить, что формат дескриптора сегмента, изображенный на рис.3.3, справедлив только для случая нахождения соответствующего сегмента в оперативной памяти. Если же бит присутствия в поле прав доступа равен нулю (сегмент отсутствует в памяти), то все биты, за исключением поля прав доступа, считаются неопределенными и могут использоваться системными программистами (для указания адреса сегмента во внешней памяти) произвольным образом.

Локальное адресное пространствозадачи определяется через таблицуLDT(localdescriptortable). У каждой задачи может быть свое локальное адресное пространство. Общее илиглобальное адресное пространствоопределяется через таблицуGDT(globaldescriptortable). Само собой, что работу с этими таблицами (их заполнение и последующую модификацию) должна осуществлять операционная система. Доступ к таблицам LDT и GDT со стороны прикладных задач должен быть исключен.

Рис.3.3.Дескриптор сегмента

При переключении микропроцессора в защищённый режим он начинает совершенно другим образом, чем в реальном режиме, вычислять физические адреса команд и операндов. Прежде всего, содержимое сегментных регистров интерпретируется иначе: считается, что там содержится не адрес начала сегмента, а номер соответствующего сегмента. Для того чтобы подчеркнуть этот факт, сегментные регистры CS,SS,DS,ES,FS,GSв таком случае даже называются иначе –селекторами сегментов.При этом каждый селекторный регистр разбивается на следующие три поля (рис. 3.4):

поле индекса (index) – старшие 13 битов (3-15). Определяет собственно номер сегмента (его индекс в соответствующей таблице дескрипторов);

поле индикатора таблицы сегментов (tableindex,TI) – бит с номером 2. Определяет часть виртуального адресного пространства (общее или принадлежащее только данной задаче). Если ТI=0, тоIndexуказывает на элемент в глобальной таблице дескрипторовGDT, то есть идёт обращение к общей памяти. ЕслиTI=1, то идёт обращение к локальной области памяти текущей задачи; это пространство описывается локальной таблицей дескрипторов LDT;

поле уровня привилегий – биты 0 и 1. Указывает запрашиваемый уровень привилегий (RPL,requestedprivilegelevel).

Операционная система в процессе своего запуска инициализирует многие регистры и, прежде всего, GDTR. Этот регистр содержит начальный адрес глобальной таблицы дескрипторов (GDT) и её размер. Как мы уже знаем, в GDT находятся дескрипторы глобальных сегментов и системные дескрипторы.

Рис.3.4.Селектор сегмента

Для манипулирования задачами ОС имеет информационную структуру, которую мы уже определили как дескриптор задачи(см. раздел «Понятия вычислительного процесса и ресурса», глава 1). Микропроцессор поддерживает работу с наиболее важной частью дескриптора задачи, которая меньше всего зависит от операционной системы. Эта инвариантная часть дескриптора, с которой и работает микропроцессор, названасегментом состояния задачи(taskstatesegment,TSS). Перечень полейTSSизображен на рис. 3.5. Видно, что в основном этот сегмент содержит контекст задачи. Процессор получает доступ к этой структуре с помощью регистра задачи (taskregister,TR).

Регистр TR содержит индекс (селектор) элемента в GDT. Этот элемент представляет собой дескриптор сегмента TSS. Дескриптор заносится в теневую часть регистра (см. рис. 3.2). К рассмотрению TSS мы ещё вернемся, а сейчас заметим, что в одном из полей TSS содержится указатель (селектор) на локальную таблицу дескрипторов данной задачи. При переходе процессора с одной задачи на другую содержимое поля LDTRзаносится микропроцессором в одноименный регистр. Инициализировать регистр TR можно и явным образом.

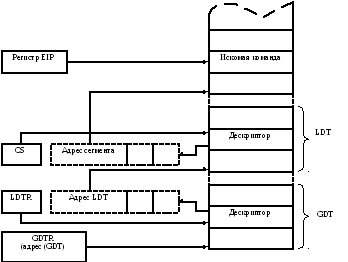

Итак, регистр LDTR содержит селектор, указывающий на один из дескрипторов глобальной таблицы GDT. Этот дескриптор заносится микропроцессором в теневую часть регистра LDTR и описывает таблицу LDT для текущей задачи. Теперь, когда у нас определены как глобальная, так и локальная таблица дескрипторов, можно рассмотреть процесс определения линейного1адреса. Для примера рассмотрим процесс получения адреса команды. Адреса операндов определяются по аналогии, но задействованы будут другие регистры.

Микропроцессор анализирует бит TIселектора кода и в зависимости от его значения, извлекает из таблицы GDT или LDT дескриптор сегмента кода с номером (индексом), который равен полюindex(биты 3-15 селектора, см. рис. 3.4). Этот дескриптор заносится в теневую (скрытую) часть регистра CS.Далее микропроцессор сравнивает значение регистра EIP2с полем размера сегмента, содержащегося в извлеченном дескрипторе, и если смещение относительно начала сегмента не превышает размера предела, то значение EIP прибавляется к значению поля начала сегмента и мы получаем искомый линейный адрес команды.

Рис. 3.5.Сегмент состояния задачи (TSS)

Линейный адрес – это одна из форм виртуального адреса. Исходный двоичный виртуальный адрес, вычисляемый в соответствии с используемой адресацией, преобразуется в линейный. В свою очередь, линейный адрес будет либо равен физическому (если страничное преобразование отключено), либо с помощью страничной трансляции преобразуется в физический адрес. Если же смещение из регистра EIP превышает размер сегмента кода, то эта аварийная ситуация вызывает прерывание и управление должно передаваться супервизору ОС.

Р ассмотренный

нами процесс получения линейного адреса

проиллюстрирован на рис. 3.6. Стоит

отметить, что поскольку межсегментные

переходы происходят нечасто, то, как

правило, определение линейного адреса

заключается только в сравнении значения

EIP с полем предела сегмента и в прибавлении

смещения к началу сегмента. Все необходимые

данные уже находятся в микропроцессоре,

и операция получения линейного адреса

происходит очень быстро.

ассмотренный

нами процесс получения линейного адреса

проиллюстрирован на рис. 3.6. Стоит

отметить, что поскольку межсегментные

переходы происходят нечасто, то, как

правило, определение линейного адреса

заключается только в сравнении значения

EIP с полем предела сегмента и в прибавлении

смещения к началу сегмента. Все необходимые

данные уже находятся в микропроцессоре,

и операция получения линейного адреса

происходит очень быстро.

Рис.3.6. Процесс получения линейного адреса команды

Итак, линейный адрес может считаться физическим адресом, если не включен режим страничной трансляции адресов. Аппаратные средства микропроцессора для поддержки рассмотренного способа двойной трансляции виртуальных адресов в физические явно недостаточны, и при наличии большого количества небольших сегментов приводят к медленной работе. В самом деле, теневой регистр при каждом селекторе имеется в единственном экземпляре, и при переходе на другой сегмент потребуется вновь находить и извлекать соответствующий дескриптор сегмента, а это требует времени. Страничный же способ трансляции виртуальных адресов, как мы знаем, имеет немало своих достоинств. Поэтому в защищённом режиме работы, при котором всегда действует описанный выше механизм определения линейных адресов, может быть включен ещё и страничный механизм.