Konyukhova_arhitektura

.pdfНаличие сигнала прерывания не обязательно должно вызывать прерывание исполняющейся программы, процессор может иметь систему защиты от прерываний: отключение системы прерываний, запрет или маскирование отдельных сигналов прерываний. Программное управление этими средствами позволяет операционной системе регулировать обработку сигналов прерываний. Процессор может либо обрабатывать прерывания сразу по их приходу, либо откладывать их обработку на некоторое время, либо полностью игнорировать. Например, если установлен в единицу флажок трассировки TF, то процессор выполняет одну команду программы, а затем генерирует прерывание типа 1, т.е., программа выполняется по шагам. Если сброшен флаг прерываний IF, то процессор не реагирует на внешние прерывания (за исключением немаскируемых). Для маскирования отдельных прерываний используется регистр масок. Управляется командами CLI (запретить прерывания) и STI (разрешить прерывания).

С каждым отдельным типом прерывания или исключения связан идентифицирующий его номер в диапазоне от 0 до 255 и соответствующий обработчик. Исключениям и немаскируемым прерываниям присвоены номера из интервала от 0 до 31, а маскируемым прерываниям – от 32 до 255. Не все из этих значений используются процессорами в настоящее время; неназначенные номера зарезервированы для использования в будущем. Номера прерываний, исключений и адреса (векторы) соответствующих обработчиков хранятся в специальной таблице – таблице векторов прерываний, расположенной в памяти. При возникновении прерывания или исключения по его номеру в таблице векторов прерываний определяется адрес соответствующей процедуры обработки прерывания или исключения, к которой осуществляется переход. Рассмотрим более подробно, каким образом выполняется вызов и возврат из обработчика прерываний или исключений.

Механизмы обработки прерываний и исключений во многом схожи, но есть некоторые различия, связанные с возвратом из обработчика. Механизм обработки прерываний включает в себя следующие этапы:

1.Установление факта прерывания.

2.Запоминание в стеке состояния прерванного процесса, которое определяется содержимым регистра флагов PSW, счётчика команд IP, сегментного регистра CS. При необходимости, также запоминается содержимое регистров, которые будут использоваться процедурой

80

прерывания и, следовательно, изменяться. Некоторые типы исключений и прерываний также помещают в стек код ошибки, для того чтобы диагностировать причину, вызвавшую исключение.

3.Определение адреса процедуры обработки прерывания по номеру прерывания в таблице векторов прерываний и осуществление перехода к этому обработчику путём загрузки адреса в регистры CS

иIP.

4.Обработка прерывания. Процедура обработки прерывания выполняет свои команды.

5.Восстановление состояния прерванной программы. После успешного выполнения процедуры обработки прерывания при достижении команды IRET (этой командой завершаются обработчики прерываний) из стека восстанавливается старое содержимое сохраненных в нём регистров (старое состояние), в т.ч., и адрес возврата – значения регистров CS и IP.

6.Возврат в прерванную программу. На основании адреса возврата осуществляется переход к прерванному процессу. Возврат должен осуществляться на команду, следующую за командой, выполненной до возникновения прерывания. Процедура обработки прерываний, обладающая таким свойством, называется прозрачной.

При возникновении сбоя адрес возврата является адресом команды, вызвавшей сбой, поэтому возврат осуществляется снова к этой команде для попытки её повторного выполнения (рестарта). Обработка ловушек аналогична обработке прерываний. При аварийных завершениях вычислительный процесс завершается без возможности восстановления исходного состояния программы, в которой произошло данное исключение.

Поскольку сигналы прерываний возникают в произвольные моменты времени, то на момент прерывания может существовать несколько сигналов прерываний, которые могут быть обработаны только последовательно. Для этого прерываниям присваиваются приоритеты. Существуют две дисциплины обслуживания приоритетных прерываний:

1) прерывание с более высоким приоритетом может прервать обработку прерывания с более низким приоритетом;

2) прерывание с более низким приоритетом обслуживается до конца, после чего обрабатывается прерывание с более высоким приоритетом.

81

В следующей главе рассмотрим вопросы, касающиеся организацией памяти ВМ.

Вопросы для самопроверки

1.Дайте пояснение понятию «система команд». На какие группы можно разделить команды процессора?

2.Что такое машинная операция, микрооперация, микропрограмма, машинный такт?

3.Из каких частей состоит команда процессора? Какие существуют форматы команд? В чём заключается суть естественной и принудительной адресации команд?

4.Какие существуют режимы адресации данных? Назовите особенности каждого из них, укажите принципы формирования эффективного адреса; приведите примеры. Каким образом осуществляется доступ к элементам массива, записи, массива записей?

5.Раскроете особенности внутрисегментных и межсегментных режимов адресации команд, приведите примеры.

6.Каким образом вычисляется физический адрес ячейки памяти

вреальном и защищенном режимах работы процессора?

7.Что представляет собой поток управления? При каких условиях осуществляется передача управления?

8.Каким образом изменяют поток управления команды условных и безусловного переходов, вызовов подпрограмм, сопрограмм? В чём заключается особенность взаимодействия вызывающей и вызываемой процедур и взаимодействия сопрограмм?

9.Дайте определения следующим терминам: прерывание, исключение, сбой, ловушка, аварийное завершение. В чём заключается различие между прерываниями и исключениями?

10.Что представляет собой таблица векторов прерываний, процедура обработки прерываний (исключений)? Поясните свойство прозрачности процедуры обработки прерываний.

11.В чём заключается механизм обработки прерываний? Какие регистры в обязательном порядке сохраняются в стеке? Что представляет собой адрес возврата? Назовите особенности возврата при возникновении исключений.

12.В чём заключается управление обслуживанием прерываний, приоритетных прерываний? Дайте определение маскируемым и немаскируемым прерываниям.

82

6.СОВРЕМЕННОЕ СОСТОЯНИЕ И ТЕНДЕНЦИИ РАЗВИТИЯ ПРОЦЕССОРОВ

Всоответствии с [2], в настоящее время доминирующее положение среди процессоров, используемых для персональных компьютеров, серверов, индустриальных систем, занимают CISC-процессоры Pentium фирмы «Intel» и их клоны с системой команд х86 (более 80 %). Архитектура и тенденции развития этих процессоров отражают достижения всей компьютерной индустрии. Остальную долю занимают процессоры (большинство из них являются RISCпроцессорами) других семейств, например, SPARC компании «SUN», Alpha компании «DEC» и др.

Особенности организации и функционирования современных процессоров рассмотрим на примере процессоров Pentium фирмы

«Intel».

6.1. Архитектурные особенности процессоров Pentium

В соответствии с [2], микропроцессор Pentium (1993 год) является первым суперскалярным процессором для персональных компьютеров. Включает в себя следующие функциональные блоки:

1)блок ШИ;

2)два 5-ступенчатых конвейера (U и V) выполнения команд целочисленных вычислений;

3)раздельные кэши команд и данных уровня L1 объёмом 8 Кбайт каждый;

4)блок вычислений с плавающей точкой FPU, организованный

ввиде конвейера;

5)блок предсказания ветвлений;

6)блок управления памятью.

Большинство команд выполняется за один такт. В случае выполнения сложных команд используется расширенный микрокод из ПЗУ микропрограмм сложных команд.

Конвейеры Pentium реализуют традиционные пять этапов выполнения команд (выборку, декодирование операции, чтение операндов, записи результатов). При вычислении операций с плавающей точкой добавляются ещё три шага: X1 – преобразование данных в формате расширенной сложности, X2 – выполнение FPU-команды, WF – округление результата и его запись в регистровый файл FPU. Конвейер

83

U может выполнять как целочисленные, так и команды с плавающей точкой. При этом команды арифметики с плавающей точкой не могут запускаться в паре с целочисленными командами. Кроме того, конвейер U содержит многоразрядный сдвигатель, используемый при выполнении арифметических, логических, циклических сдвигов, операций умножения и деления. Конвейер V выполняет только целочисленные команды.

Использование независимых кэшей обеспечивает одновременный бесконфликтный доступ к ним. Кэш-память команд связана с буфером предварительной выборки 256-битовой шиной. Если выбираемая команда в кэш-памяти отсутствует, то выполняется чтение искомой команды из основной памяти и её загрузка в буфер предвыборки с одновременной записью в кэш команд.

Кэш-память данных соединяется с конвейерами U и V при помощи двух 32-разрядных шин, что обеспечивает возможность одновременного обращения к ней со стороны каждого конвейера.

Блок управления памятью осуществляет двухступенчатое формирование физического адреса ячейки памяти сначала в пределах сегмента, а потом в пределах страницы. Для управления работой внешнего кэша используются специальные аппаратные средства.

Архитектурным нововведением Pentium является специальный режим системного управления (SMM – System Management Mode),

который разработан для перевода системы в состояние пониженного энергопотребления. Этот режим недоступен приложениям и управляется программой из ПЗУ на кристалле процессора. В режиме SMM Pentium использует иное, изолированное от других режимов пространство памяти.

Блок ШИ обеспечивает связь процессора с другими устройствами через системную шину, включающую в себя 64-разрядную шину данных и 32-разрядную шину адреса и шину управления. Процессор Pentium поддерживает работу систем с физической памятью до 4 Гбайт.

Развитие процессоров Pentium связано, прежде всего, с усовершенствованием технологии их производства, расширением системы команд, развитием алгоритмов предсказания переходов, методов загрузки конвейеров, способов взаимодействия с кэш-памятью.

Отличительной особенностью процессоров Pentium 6-го (Pentium Pro, Pentium II, Pentium III) и 7-го (Pentium IV) поколений от ранних моделей Pentium является иной подход к реализации принципа мно-

84

гооперационной обработки данных. Он заключается в том, что вместо увеличения числа конвейеров исполнения команд, что требует значительных аппаратных затрат, используется один конвейер с большим количеством исполнительных блоков. Например, обработка команд в Pentium IV осуществляется 20-ступенчатым конвейером (гиперконвейером), который условно можно разделить на три относительно независимых конвейера:

1.Входной конвейер упорядоченной обработки, который обеспечивает выборку команд из памяти, декодирование их во внутренние RISC-команды и устранение ложных взаимосвязей по данным и ресурсам.

2.Конвейер неупорядоченной обработки, собственно реализующий исполнение команд. При неупорядоченной обработке происходит более интенсивная загрузка конвейеров суперскалярного процессора. Чтобы гарантировать правильное исполнение программы, результаты команд, выполненных вне очереди, должны записываться по целевым адресам в том же порядке, в каком они следуют в исходной программе. Эту работу осуществляет специальный блок процессора – блок временного хранения результатов, выполненных вне очереди.

3.Конвейер вывода результатов исполнения команд, который осуществляет запись результатов в архитектурные регистры процессора и память в порядке, предусмотренном программой.

Эффективная работа гиперконвейера Pentium IV обеспечивается также за счёт спекулятивного исполнения команд, когда для непрерывной загрузки конвейера выполняются действия, не предусмотренные программным кодом.

В блоке предсказания ветвлений используется более совершенный, по сравнению с более ранними моделями процессоров Pentium, алгоритм предсказания ветвлений. Адреса команд переходов и метки ветвлений с подробной предысторией сохраняются в буфере (объёмом 4 Кбайта) блока предсказания ветвлений.

Ещё одним важным отличием процессора Pentium IV от ранних моделей является использование в его структуре вместо кэша команд кэша трасс. Трассы – это последовательности микрокоманд, в которые декодированы команды x86, принадлежащие одной или нескольким ветвям исходной программы. В кэше могут размещаться до 12 Кбайт микрокоманд. В кэш трасс не попадают команды, которые никогда не будут использоваться. Кэш трасс совместно с блоком выборки образуют устройство предварительной обработки.

85

Использование гиперконвейера, кэша трасс и более производительного исполнительного ядра позволило достигнуть в Pentium IV существенного повышения производительности.

6.2. Программная модель процессоров Pentium

Объединяющей характеристикой рассмотренных микропроцессоров Pentium является то, что все они, несмотря на существенные различия в архитектуре, имеют одинаковую программную модель. Совокупность всех программно доступных регистров процессора образует его программную модель [2], показывающую ресурсы процессора, которыми может пользоваться программист.

Программная модель подразделяется на прикладную и систем-

ную. В состав прикладной программной модели (ППМ) процессора входят полный набор регистров, которые доступны прикладным программистам; особенности организации памяти и доступные способы адресации; типы данных и команд. Системная программная модель (СПМ) процессора объединяет его программно доступные системные ресурсы, с помощью которых обеспечивается доступ к встроенным механизмам защиты и многозадачности. СПМ процессора в основном используется системными программистами.

6.2.1. Прикладная программная модель процессоров Pentium

Старшие модели процессоров Pentium программно совместимы с младшими моделями. Регистры ППМ удобно представить в виде четырёх групп 32-разрядных регистров [1]:

1.РОН, которые могут использоваться в формате двойного слова

(32 бита), слова (16 бит) и байта (8 бит): EAX (AX, AH, AL), EBX (BX, BH, BL), ECX (CX, CH, CL), EDX (DX, DH, DL).

2.Регистры-указатели ESP (SP), EBP (BP) и индексные регистры

ESI (SI), EDI (DI), которые доступны в формате двойного слова

ислова.

3.Указатель команд EIP (IP).

4.Регистр флагов FLAGS или PSW.

Функции, выполняемые регистрами, в подавляющем большинстве аналогичны функциям рассмотренных ранее регистров. Регистр FLAGS, помимо уже известных флагов состояния и управления, содержит системные флаги, которые управляют обработкой исключений, вводом – выводом и рядом других функций. Большинство системных флагов предназначено для использования операционной системой.

86

6.2.2. Системная программная модель процессоров Pentium

СПМ включает в себя следующий набор регистров [2]:

1)6-байтовые регистры GDTR (Global Descriptor Table Register)

иIDTR (Interruption Descriptor Table Register) адресов глобальной де-

скрипторной таблицы (GDT) и дескрипторной таблицы прерываний

(IDT);

2)16-битный регистр LDTR (Local Descriptor Table Register), со-

держащий селектор сегмента локальной дескрипторной таблицы (LDT), и 16-битный регистр TR (Task Register), содержащий селектор сегмента состояния задачи TSS (Task State Segment);

3)16-битные сегментные регистры CS, SS, DS, ES, FS, GS, содержащие селекторы дескрипторов текущих сегментов кода, стека

иданных;

4)32-битные регистры управления процессором CR (Control Register): CR0, CR2, CR3, CR4. Они хранят признаки состояния процессора, общие для всех задач;

5)8-байтовые программно недоступные кэш-регистры для хранения текущих дескрипторов сегментов: стека – регистр SSt, кода – регистр CSt, данных – регистры DSt, ESt, FSt, GSt, а также сегментов

LDT и TSS;

6)32-разрядные регистры отладки DR (Debug Register): DR0 – DR7, предназначенные для аппаратной отладки программ;

7)32-разрядные регистры тестирования TR (Test Register): TR1 – TR12, используемые для тестирования внутренних устройств про-

цессора.

Начиная с Pentium 286, процессоры Intel могли работать в защищённом режиме, что обеспечивало аппаратную поддержку многозадачности. Защищённый режим работы процессора Pentium сохранил сегментную модель памяти. Однако сегмент в защищённом режиме – это не просто область памяти, это объект, имеющий строго определённый размер и обладающий набором атрибутов, по которым выполняется аппаратная защита памяти со стороны процессора. В соответствии с [6, 8], каждый сегмент имеет свой дескриптор (описатель сегмента). Дескрипторы сегментов хранятся в специальных системных сегментах – дескрипторных таблицах. Существует три типа дескрипторных таблиц: глобальная GDT (одна в системе), локальная LDT (своя для каждой задачи) и таблица прерываний IDT. Каждый элемент (дескриптор) таблицы описывает свой сегмент памяти. Сег-

87

менты памяти не пересекаются. Размер таблиц находится в диапазоне 8 байт – 64 Кбайт. Адреса начала GDT и IDT хранятся в специальных программно доступных регистрах процессора GDTR и IDTR соответственно. Из 48 байт (длина регистров) 32 байта указывают линейный адрес начала соответствующей таблицы, а остальные 16 байт – её размер (предел). Регистры LDTR и TR содержат селекторы (индексы дескрипторов), с помощью которых из таблицы GDT выбираются дескрипторы с базовыми адресами LDT и TSS отдельных задач.

6.2.3. Система команд и режимы адресации процессоров

Pentium

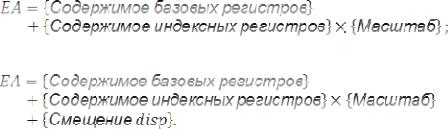

Система команд процессоров Pentium поддерживает типы команд, рассмотренные ранее. С эволюцией системы команд для различных моделей процессоров Pentium можно ознакомиться в [1, 2]. Набор команд обеспечивает выполнение операций над 8-, 16- и 32разрядными операндами; содержит безадресные, 1-адресные и 2- адресные команды. Система команд процессоров Pentium обеспечивает поддержку 11 режимов адресации [1]: 9 рассмотренных ранее и 2 дополнительных – базовый индексный с масштабированием и относительный базовый индексный с масштабированием. Вычисление эффективного адреса (32-разрядного внутрисегментного смещения) выполняется по формулам 15 и 16 соответственно.

(15)

(16)

Двухбитное поле Масштаб (Scale) кодирует значение масштабного множителя (1, 2, 4, 8), который указывает размер элементов массива при использовании индексной адресации.

6.3. Аппаратная организация защиты в процессорах Pentium

Современные ВМ поддерживают многопрограммный (мультипрограммный) и многозадачный (мультизадачный) режимы работы [2].

Многопрограммный режим предполагает одновременное выполнение процессором нескольких программ, переключаясь между ними. Естественно, в каждый конкретный момент времени процессор может выполнять команды только определённой программы.

88

Многозадачностью называется способ организации работы компьютера, при котором в его оперативной памяти содержатся программы и данные для одновременного выполнения нескольких процессов обработки информации (задач). Один из способов реализации многозадачности, называемый разделением времени, заключается

впредоставлении каждой задаче некоторого интервала времени (кванта обслуживания), в течение которого процессор выполняет команды соответствующей программы. Если по истечении выделенного кванта времени обработка программы не заканчивается, она прерывается и становится в очередь программ, ожидающих обработки. При реализации многозадачности необходимо обеспечить взаимную защиту программ и данных, относящихся к различным задачам.

Для обнаружения и идентификации ошибок современные процессоры, в т.ч., и процессоры Intel, сконструированы со встроенным механизмом защиты. Этой цели способствует организация памяти, которая предусматривает взаимное разделение адресных пространств различных задач с помощью сегментов. Система привилегий жёстко регламентирует взаимоотношения задач с памятью, операционной системой (ОС) и друг с другом. Для эффективного управления всей системой ОС разрешён доступ к памяти всех программ, а пользовательским программам обеспечивается доступ к программам ОС только в разрешённых точках входа. Для поддержки указанных функций

всистему команд процессоров Intel введены некоторые привилегированные команды, которые могут выполняться только ОС. Кроме того,

вструктуре процессора имеется ряд регистров, доступ к которым со стороны пользовательских программ закрыт.

Основной единицей защиты является сегмент. При каждом обращении к сегменту проверяется ряд параметров защиты, задаваемых

вдескрипторе, в т. ч. предел, тип сегмента, права, уровень привилегий.

Специальное поле предел определяет границы сегмента. С его помощью процессор обнаруживает такие распространённые ошибки, как переполнение стека, неверные указатели и индексы массивов, неправильные адреса вызовов и переходов. Ошибки нарушения границы обнаруживаются в момент их возникновения, что существенно

89