Konyukhova_arhitektura

.pdfщих битам информации. В основе работы этих элементов лежит двоичная (булева) логика, когда используются только два значения: «истина» (логическая 1) и «ложь» (логический 0). Узлы обеспечивают одновременную обработку групп сигналов – информационных слов. Блоки реализуют некоторую функционально обособленную часть машинных операций по обработке информационных слов (например, блок выборки команд). Устройства предназначаются для выполнения отдельных машинных операций и их последовательностей.

Базовыми элементами являются инверторы (строятся на основе транзистора), вентили (на базе двух транзисторов), триггеры (состоят из двух вентилей).

По своему назначению элементы делятся на следующие классы: формирующие, логические (комбинационного типа) и запоминающие (последовательного типа) [5]. К формирующим элементам относятся различные формирователи, усилители и т.п., которые служат для выработки определённых электрических сигналов, восстановления их параметров (полярности, мощности, амплитуды и т.д.). Элементы комбинационного типа – это цифровые устройства, выполняющие определённую логическую операцию («И», «ИЛИ», «НЕ» и т.д.). Логические элементы являются основой построения комбинационных схем (цепей). Особенностью логических элементов и построенных на их основе комбинационных схем является то, что их выходные сигналы зависят только от входных сигналов (т.е., они не содержат памяти). Элементы последовательного типа используются для построения более сложных цифровых устройств – автоматов с памятью. В них результат обработки информации зависит не только от входных сигналов, но и от внутреннего состояния автомата.

Рассмотрим элементы последних двух классов более подробно.

2.1. Комбинационные схемы

Для описания законов функционирования комбинационных схем используется специальный математический аппарат булевой логики. Рассмотрим функционально полную систему булевых функций

иреализующие их логические элементы [5, 10].

1.Конъюнкция (логическое умножение) y x1 x2 .

Эта функция реализуется логическим элементом «И» – вентилем, на выходе которого формируется уровень логической 1 тогда и только тогда, когда на все его входы будет подан уровень логической 1.

20

Условное обозначение логического элемента «И» представлено на рис. 6, а закон функционирования отражает табл. 1.

x1 |

|

y |

|

& |

|||

x2 |

|||

|

|||

|

|

||

|

|

|

|

Рис. 6. Логический элемент «И» |

|||

|

|

Таблица. 1 |

|

Таблица истинности «И» |

|||

X1 |

X2 |

Y |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

2. Дизъюнкция (логическое сложение) y x1 x2.

Эта функция реализуется логическим элементом «ИЛИ» – вентилем, на выходе которого формируется уровень логического 0 тогда и только тогда, когда на все его входы будет подан уровень логического 0.

Условное обозначение логического элемента «ИЛИ» представлено на рис. 7, а закон функционирования отражает табл. 2.

x1 |

|

y |

|

1 |

|||

x2 |

|||

|

|

||

|

|

|

Рис. 7. Логический элемент «ИЛИ»

Таблица. 2

Таблица истинности «ИЛИ»

X1 |

X2 |

Y |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

3. Отрицание (инверсия) y x.

Эта функция реализуется логическим элементом «НЕ» – инвертором, который изменяет входной сигнал на противоположный.

Условное обозначение логического элемента «НЕ» представлено на рис. 8, а закон функционирования отражает табл. 3.

21

x1 |

y |

Рис. 8. Логический элемент «НЕ»

Таблица 3

Таблица истинности «НЕ»

X Y

01

10

4.Конъюнкция и инверсия (Штрих Шеффера) y x1 x2 .

Эта операция реализуется логическим элементом «И-НЕ» – вентилем, на выходе которого формируется уровень логического 0 тогда и только тогда, когда на все его входы будет подан уровень логической 1. Функция названа по фамилии американского логика Генри Мориса Шеффера (Henry M. Sheffer, 1882 – 1964).

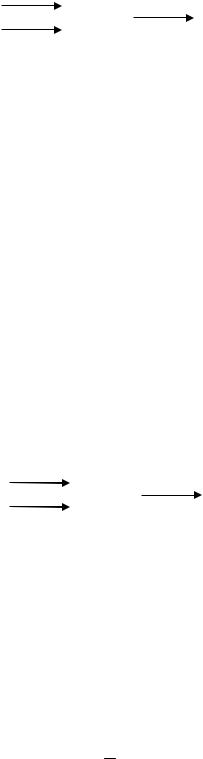

Условное обозначение логического элемента «И-НЕ» представлено на рис. 9, а закон функционирования отражает табл. 4.

x1 |

|

y |

|

& |

|||

x2 |

|||

|

|||

|

|

||

|

|

|

Рис. 9. Логический элемент «И-НЕ»

Таблица 4

Таблица истинности «И-НЕ»

X1 |

X2 |

Y |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

5. Дизъюнкция и инверсия (Стрелка Пирса) y x1 x2 .

Эта функция реализуется логическим элементом «ИЛИ-НЕ» – вентилем, на выходе которого формируется уровень логической 1 тогда и только тогда, когда на все его входы будет подан уровень логического 0. Название этой операции дано по фамилии американского математика Чарлза Сандерса Пирса (Charles S. Peirce, 1839 – 1914).

Условное обозначение логического элемента «ИЛИ-НЕ» представлено на рис. 10, а закон функционирования отражает табл. 5.

22

x1 |

|

y |

|

1 |

|||

x2 |

|||

|

|

||

|

|

|

Рис. 10. Логический элемент «ИЛИ-НЕ»

Таблица 5

Таблица истинности «ИЛИ-НЕ»

X1 |

X2 |

Y |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

6. Эквивалентность y x1 x2.

Эта функция реализуется логическим элементом «Исключающее ИЛИ-НЕ» – вентилем, на выходе которого формируется уровень логического 0 тогда и только тогда, когда на его входы подаются одинаковые сигналы (оба 0 или обе 1).

Условное обозначение логического элемента «Исключающее ИЛИ-НЕ» представлено на рис. 11, а закон функционирования отражает табл. 6.

x1 |

|

y |

|

= 1 |

|||

x2 |

|||

|

|

||

|

|

|

Рис. 11. Логический элемент «Исключающее ИЛИ-НЕ»

Таблица 6

Таблица истинности «Исключающее ИЛИ-НЕ»

X1 |

X2 |

Y |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

7. Отрицание эквивалентности y x1 x2 .

Эта функция реализуется логическим элементом «Исключающее ИЛИ» – вентилем, на выходе которого формируется уровень логической 1 тогда и только тогда, когда на один вход подаётся уровень логической 1, а на другой – уровень логического 0.

23

Условное обозначение логического элемента «Исключающее ИЛИ» представлено на рис. 12, а закон функционирования отражает табл. 7.

x1 |

|

y |

|

= 1 |

|||

x2 |

|||

|

|

||

|

|

|

Рис. 12. Логический элемент «Исключающее ИЛИ»

Таблица 7

Таблица истинности «Исключающее ИЛИ»

X1 |

X2 |

Y |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

На основе перечисленных выше логических элементов строятся комбинационные схемы, которые, в свою очередь, служат базой для построения таких функциональных узлов, как шифраторы и дешифраторы, компараторы, сумматоры и другие. В них результат обработки зависит только от комбинации входных сигналов и вырабатывается сразу после их подачи.

Некоторые функциональные узлы комбинационного типа будут рассмотрены ниже.

2.2. Автоматы с памятью

Узлы и устройства, содержащие элементы памяти, относятся к классу автоматов с памятью (цифровых автоматов). Наличие элементов памяти позволяет автомату иметь некоторое внутреннее состояние Q, определяемое совокупностью состояний всех элементов памяти. В зависимости от внутреннего состояния автомат с памятью по-разному реагирует на один и тот же набор входных сигналов X. При этом автомат переходит в новое состояние и вырабатывает набор выходных сигналов Y [5, 10].

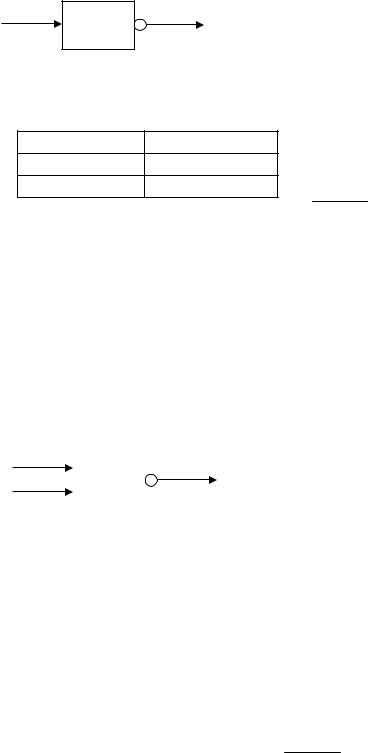

Общую схему автомата с памятью условно можно представить следующим образом (рис. 13).

24

Переходы автомата из одного состояния в другое начинаются с некоторого исходного состояния Q0. При этом переход из текущего состояния в новое выполняется по правилам, задаваемым функцией переходов f: Qн f (Qт,Xт)и зависит как от текущего состояния Qт, так и от входных сигналов в текущий момент времени Xт. Выходные сигналы в текущий момент времени Yт формируются по правилам, задаваемым функцией выходов φ: Yт (Qт,Xт) и зависят от текущего состояния автомата Qт и текущих входных сигналов Xт. Вся последовательность входных сигналов определяет последовательность состояний автомата и его входных сигналов. Это объясняет название «последовательные схемы», применяемое также и для обозначения автоматов с памятью [5].

X |

Q |

Y |

|

|

|

|

|

|

Рис. 13. Общая схема автомата с памятью:

X – совокупность одновременно действующих входных сигналов;

Y – совокупность выходных сигналов;

Q – совокупность внутренних состояний

Структурно автоматы с памятью отличаются от комбинационных цепей наличием в их (автоматов) схемах обратных связей, вследствие чего в них проявляются свойства запоминания состояний. Согласно [5, 10], в каноническом представлении цифровые автоматы подразделяют на две части: память и комбинационную цепь. На входы комбинационной цепи подаются входные сигналы и сигналы состояния автомата, на выходе комбинационной цепи вырабатываются выходные сигналы и сигналы перевода автомата в новое состояние.

Состояние автомата с памятью называется устойчивым, если возникнув под действием входных сигналов, оно продолжает неограниченно долго сохраняться при сохранении или повторении этих входных сигналов.

По видам зависимости состояний перехода и выходных сигналов цифровые автоматы делят на два класса [5, 10]:

1. Автоматы Мили – в них новое состояние и выходные сигналы зависят как от текущего состояния автомата, так и от текущих входных сигналов, что описывают формулы 6 и 7.

Qн f (Qт,Xт); |

(6) |

Yт (Qт,Xт). |

(7) |

25 |

|

2. Автоматы Мура – в них новое состояние зависит от текущего состояния и текущих входных сигналов, а выходные сигналы – только от текущего состояния, что описывают формулы 8 и 9.

Qн f (Qт,Xт); |

(8) |

Yт (Qт). |

(9) |

Названия автоматов даны по фамилиям их изобретателей Джорд-

жа Мили (George H. Mealy, 1927 – 2010) и Эдварда Мура (Edvard F. Moore, 1925 – 2003), американских профессоров в области математики и информатики.

Автономный автомат с памятью – это цифровой автомат, не имеющий информационных входов и переходящий из одного состояния в другое под действием тактирующих сигналов по алгоритму, заданному структурой автомата.

Элементарный автомат с памятью – это цифровой автомат,

обладающий следующими свойствами:

1)является автоматом Мура;

2)число состояний автомата равно двум;

3)является детерминированным (правило переходов и выходов являются однозначными);

4)имеет полную систему переходов и выходов (функции переходов f и выходов φ описаны для всех допустимых состояний и входных сигналов);

5)структурные каналы автомата несут двоичную информацию. Обычно элементарный автомат имеет два выхода: один прямой,

другой инверсный, которые рассматриваются как один структурный канал. Принципы разработки, проектирования и реализации автоматов с памятью описывает теория автоматов. Ярким примером элементарного цифрового автомата является триггер, который более подробно будет рассмотрен ниже.

2.3. Триггеры

Триггером называют элементарный автомат с положительной обратной связью, который может многократно переходить из одного устойчивого состояния в другое. В структуре триггера можно выделить собственно элементы памяти (фиксатор) и схему управления. Фиксатор строится на двух элементах «ИЛИ-НЕ» или двух элементах «И-НЕ», связанных друг с другом «накрест», так, что выход одного соединён со входом другого. Состояние триггера оценивается по его прямому выходу.

26

Триггеры можно классифицировать по различным признакам [5]. 1. По логическому функционированию триггеры подразделяют на следующие типы: RS, D, T, JK, комбинированные, со сложной

логикой.

Простейшим из них является RS-триггер, на примере которого познакомимся с принципами функционирования триггеров. Схемы RSтриггера на элементах «ИЛИ-НЕ» и «И-НЕ» показаны на рис. 14.

R |

1 |

Q |

S |

& |

Q |

|

|

|

|

||

S |

1 |

Q |

R |

& |

Q |

|

|

Рис. 14. Схема RSтриггера на элементах «ИЛИ-НЕ» и «И-НЕ»

Буквой R (Reset) обозначается сигнал сброса триггера в 0, а буквой S (Set) – сигнал установки триггера в 1. Для RS-триггера на элементах «ИЛИ-НЕ» при подаче на его входы R и S нулевых сигналов сохраняется одно из двух его устойчивых состояний. Например, если значение на выходе Q равно 1, то этот единичный сигнал поступает по цепи обратной связи на вход второго элемента и вызывает появление на выходе Q логического 0. В свою очередь, этот 0, поступая на вход первого элемента, поддерживает выход Q в единичном состоянии. Такой режим работы RS-триггера называется режимом хранения. Подача единичного сигнала на вход S переводит RS-триггер в единичное состояние (состояние установки). Подача единичного сигнала на вход R сбрасывает RS-триггер в нулевое состояние (состояние сброса). Одновременная подача сигнала установки (логической 1 на вход S) и сигнала сброса (логической 1 на вход R) не допускается и является запрещённой.

Условное обозначение RS-триггера и таблица его состояний представлены соответственно на рис. 15 и в табл. 8.

D-триггер (от слова Delay – задержка) также имеет два устойчивых состояния. Его выход Q повторяет входной сигнал, но с задержкой, определяемой тактовым генератором.

T-триггер изменяет своё состояние каждый раз при поступлении входного сигнала. Его называют счётным триггером.

S |

|

|

|

|

Q |

|||

S |

T |

|||||||

|

|

|

|

|

|

|||

R |

R |

|

|

|

Q |

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Рис. 15. Условное обозначение RS-триггера

27

|

|

|

Таблица 8 |

|||

Состояния RSтриггера |

||||||

|

|

|

|

|

|

|

S |

R |

Q |

|

|

Q |

|

0 |

0 |

без изменения |

||||

0 |

1 |

0 |

|

1 |

|

|

1 |

0 |

1 |

|

0 |

|

|

1 |

1 |

запрещено |

||||

Триггер JK является универсальным, имеет входы установки (J) и сброса (K), подобно входам RS-триггера. JK-триггер может принимать два единичных сигнала по своим входам J и K, переходя при этом в противоположное текущему состояние.

2.По способу записи информации различают асинхронные (не-

тактируемые) и синхронные (тактируемые) триггеры. В первых переход в новое состояние вызывается непосредственно изменением входных информационных сигналов. В тактируемых триггерах имеется специальных вход C (от слова Clock – часы). Переход осуществляется при подаче на этот вход тактовых сигналов.

Триггер может запомнить один бит информации. Триггеры входят

всостав устройств, где требуется запоминание данных: регистры, счётчики, последовательные сумматоры и другие.

Элементная база составляет основу любой ВМ, поэтому следующий вопрос посвящён тому, какие на сегодняшний день существуют проблемы в развитии элементной базы и каковы перспективные направления создания новых элементов для ВМ.

2.4.Проблемы и перспективы развития элементной базы вычислительных машин

Согласно [9], одним из главных факторов достижения высокой производительности ВМ является построение их на новейшей элементной базе. Смена поколений ВМ в значительной степени связана

спереходом на новые поколения элементной базы (от зубчатого колеса и электромеханического реле до интегральных схем [3, 4, 6]).

Подавляющее большинство устройств современных ВМ и ВС реализуются на базе полупроводниковых технологий в виде больших и сверхбольших интегральных схем (БИС и СБИС соответственно). Повышение производительности ВМ и ВС, прежде всего, связано

сувеличением числа элементов на кристалле БИС или СБИС. Решение этой задачи средствами традиционных технологий возможно ли-

28

бо путём увеличения размеров кристалла, либо за счёт уменьшения площади, занимаемой простейшим элементом, с одновременным увеличением плотности упаковки этих элементов на кристалле [3, 9].

Одним из направлений увеличения числа элементов на кристалле является увеличение размеров самого кристалла, в частности, диаметра его подложки. Например, увеличение её диаметра на 10 % позволяет увеличить прирост числа элементов на кристалле до 60 %. Однако увеличение размера подложки приводит к ухудшению однородности её свойств, что приводит к техническим сложностям при её изготовлении. Переход на подложки увеличенного диаметра происходит в среднем каждые девять лет, но, очевидно, что бесконечно увеличивать размеры кристалла невозможно и нецелесообразно.

Увеличение числа элементов на кристалле достигается также за счёт уменьшения размеров самих элементов и размеров проводников, соединяющих элементы между собой. Создание интегральных микросхем выполняется по технологии литографии. Согласно этой технологии, сначала формируется маска, определяющая структуру будущей микросхемы. Затем маска накладывается на полупроводниковую пластину. После этого пластина облучается, в результате чего и образуется микросхема. Уменьшение размеров элементов на кристалле напрямую зависит от типа литографии. До настоящего времени доминирующей оставалась оптическая литография, что позволяло реализовывать кристаллы с топологическим размером (размер элемента) 0,5 – 0,35 мкм. Дальнейшие достижения в микроэлектронике связываются с лазерной, ионной и рентгеновской литографией, что позволяет выйти на размеры элементов 0,25 – 0,08 мкм. (Для сравнения толщина человеческого волоса составляет 100 мкм). Такие высокие технологии сопровождаются следующими проблемами.

1.Микроскопические размеры элементов требуют высокой чистоты используемых и напыляемых материалов, применения вакуумных установок и снижения рабочих температур. Поэтому новые заводы по производству микросхем имеют уникальное оборудование, размещаемое в «сверхчистых» помещениях.

2.Уменьшение размеров микросхем и повышение уровня их интеграции приводит к дилемме между потребляемой и рассеиваемой мощностью кристалла. При сокращении линейных размеров микросхем в два раза их объёмы изменяются в восемь раз. Пропорционально этим цифрам должны изменяться и значения мощностей, иначе

29