Konyukhova_arhitektura

.pdf

однородность всех ядер и единообразие включения всех ядер в общую схему системы.

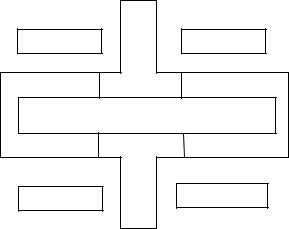

В симметричных конфигурациях между ядрами разделяется общая память, например, кэш L2, как показано на рис. 59. Минимальное число ядер в таких системах равно двум. Достоинством является относительная простота разработки, интенсивное взаимодействие ядер, простота программирования. В соответствии с [23], все ядра равноправно участвуют и в управлении вычислительным процессом, и в выполнении прикладных задач. Модули ОС выполняются в любом доступном ядре. Ресурсы выделяются для каждой выполняемой задачи по мере возникновения потребностей в них и никак не закрепляются за ядром. В решении одной задачи могут участвовать сразу несколько ядер, если она допускает распараллеливание на несколько потоков. В случае отказа одного из ядер, симметричные системы, как

Ядро 1

Регистры

Ядро 2

Регистры

Межсоединение/ Кэш-память L2

Ядро 3

Регистры

Ядро 4

Регистры

правило, сравнительно просто реконфигурируются, что является их большим преимуществом. В то же время, такие системы плохо масштабируются: увеличение числа ядер ограничивается наличием разделяемой памяти.

Рис. 59. Симметричная многоядерная архитектура с общей кэшпамятью L2

Примечание. Выше говорилось, что параллельное выполнение вычислений может выполняться на разных уровнях: отдельных задач (процессов), последовательностей команд (процедур), отдельных команд. Если рассматривать процесс как выполняющуюся программу с необходимыми для этого ресурсами (памятью, регистрами, стеком и т.п.), то поток (тред, от англ. Thread – нить) – это последовательность команд. Несколько потоков могут существовать в рамках одно-

160

го и того же процесса и совместно использовать его ресурсы. То есть отдельная программа может быть разбита на фрагменты (потоки), содержащие последовательности команд, и эти потоки могут выполняться параллельно.

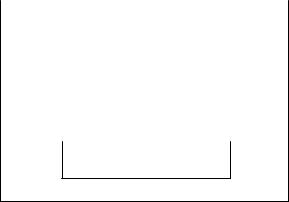

Применение различных способов организации внутрикристалльной памяти (регистров, кэшей) и механизмов динамического назначения команд на исполнение [2] позволяет организовать параллельное выполнение нескольких тредов (потоков) в одном процессорном ядре с совместным использованием ресурсов на кристалле. На рис. 60

приведён план кристалла многопотоковой мультиядерной системы с общим кэшем. Такие системы называются мультиплексорными

системами на кристалле SMT (Simultaneous Multi-Threading).

По сравнению с обычными симметричными системами, сложность разработки SMT-систем возрастает.

|

Ядро 1 |

|

|

|

Ядро 2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рег. |

Рег. |

|

|

|

Рег. |

|

Рег. |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рег. |

Рег. |

|

|

|

Рег. |

|

Рег. |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Общий кэш L2

Рис. 60. Многопотоковая многоядерная архитектура

собщим кэшем

Вассиметричных кластерных мультипроцессорных системах

ACCMP (Asymetric Cluster CMP) на кристалле размещается ассиметричный кластер процессорных ядер с различной специализированной аппаратурой. Например, кластер может содержать RISC-ядро процессора, ядра специализированных процессоров для цифровой обработки сигналов, блоки памяти, средства коммуникаций. Согласно [23], функциональная неоднородность в таких архитектурах влечёт за собой структурные различия во фрагментах системы, содержащих разные процессорные ядра и блоки. Например, они могут различаться схемами подключения процессорных ядер к СШ, способами взаимодействия процессорных ядер с устройствами и т.д. Ассиметричные кластерные архитектуры являются хорошо масштабируемыми. В ас-

161

симетричных архитектурах функции управления вычислительным процессом полностью централизованы, и ОС работает только на одном процессоре. Этот процессор является ведущим, а все остальные – ведомыми. Ведущий берёт на себя функции распределения задач и ресурсов, а ведомые работают только как обрабатывающие устройства. Ассиметричные архитектуры позволяют повысить производительность по сравнению с симметричными, но при этом требуется разработка специализированных ядер. Кроме того, такая специализация снижает надёжность системы, поскольку процессоры не являются взаимозаменяемыми.

Можно выделить три варианта конструктивного расположения ядер на кристалле:

1.Независимые процессорные ядра (каждое со своей памятью)

расположены на одном кристалле и для связи используют общую системную шину.

2.Несколько одинаковых ядер расположены на разных кристаллах, но объединены вместе в одном корпусе процессора (многочиповый процессор).

3.Ядра могут быть тесно переплетены между собой на одном кристалле и использовать некоторые общие ресурсы кристалла (например, шину и кэш-память).

Преимущества и недостатки мультиядерных процессоров вытекают из преимуществ и недостатков параллельных ВС. Следует отметить, что в настоящее время многоядерные процессоры используются крайне неэффективно. Прирост быстродействия во многом зависит от типа приложения. У программ, которые не рассчитаны на работу

смногоядерными процессорами, быстродействие увеличивается всего на 5 %. А вот оптимизированные под многоядерные процессоры приложения работают быстрее уже на 50 % [22].

10.4.Тенденции развития ВС

Существует два направления развития высокопроизводительных вычислений [2]. Первое связано с применением дорогих суперкомпьютеров с уникальной архитектурой (специальные векторные процессоры, дорогостоящая сверхбыстрая память, уникальное периферийное оборудование), например, суперкомпьютеров CRAY, NEC, IBM, Эльбрус и т.д. Второе направление связано с созданием ВС массового параллелизма. Основной упор при этом делается на увеличение числа процессоров и повышение степени параллелизма про-

162

грамм. При этом большую популярность приобретают COWсистемы, которые постепенно вытесняют MPP.

Мультипроцессорные высокопроизводительные ВС находят своё применение в таких областях, как исследовательская, промышленная, образовательная, административная, при производстве самих ВС. Такие системы требуются для точного прогнозирования погоды и климата, развития современного промышленного дизайна, создания новых фармацевтических средств и т.д. Среди установленных мультипроцессорных систем системы с архитектурой MPP составляют подавляющее большинство (65 %), системы SMP – 21, системы с векторными процессорами – 12, кластерные системы – 2 %. Доля кластерных систем постепенно возрастает.

Относительно многоядерных процессоров [22] можно сказать, что лидерами по их производству являются компании «Intel» и «AMD» продолжающие наращивать количество ядер в процессорах. Например, «Intel» планирует выпускать процессоры, содержащие до сотни ядер. Появление мультиядерных процессоров, в свою очередь, стимулирует разработку ОС и прикладного программного обеспечения, поддерживающих многоядерность. Кроме того, в корпорации «Intel» планируют выпускать многоядерный процессор с новой архитектурой, в составе которого будет находиться одно мощное центральное ядро, окружённое множеством вспомогательных ядер. Это поможет более эффективно обрабатывать сложные мультимедийные приложения в многопоточном режиме. Кроме ядер общего назначения, процессоры будут обладать специализированными ядрами для выполнения различных классов задач: графика, алгоритмы распознавания речи и т.п.

Вопросы для самопроверки

1.Дайте определение ВС. Назовите уровни, на которых может выполняться параллельная обработка информации.

2.Что такое гранулярность? Какие уровни параллелизма выделяют по степени гранулярности? В чём заключаются их особенности?

3.Перечислите преимущества и недостатки параллельных ВС.

4.Что представляет собой классификация Флинна? На какие группы делятся ВС, согласно этой классификации? Назовите их особенности. В чём заключается классификация ВС, предложенная профессором Головкиным?

163

5. По какому признаку параллельные ВС делят на мультипроцессоры и мультикомпьютеры? В чём заключается принципиальное различие между ними? Назовите преимущества и недостатки мультипроцессоров и мультикомпьютеров.

6.На какие категории делятся мультипроцессоры? Назовите особенности каждого класса мультипроцессоров.

7.На какие категории делятся мультикомпьютеры? Назовите особенности каждого класса мультикомпьютеров.

8.Что представляют собой ВС на кристалле? Какие существуют направления создания кристаллов однокристальных ВС?

9.Дайте определение понятию CMP-системы, ядра, многоядерного процессора.

10.Перечислите особенности многоядерных систем с симметричной архитектурой (SGP), многопотоковых многоядерных систем (SMT), кластерных многоядерных систем (ACCMP).

11.Расскажите об основных тенденциях развития ВС.

11.ОРГАНИЗАЦИЯ МИКРОКОНТРОЛЛЕРОВ И МИКРОКОНТРОЛЛЕРНЫХ СИСТЕМ

Наряду с многоядерными ВС, ещё одним направлением развития ВС на кристалле являются микроконтроллеры (МК) и ВС на их основе – микроконтроллерные системы (МКС), работающие в режиме реального времени. Рассмотрим обобщённую структуру типовой системы управления.

11.1. Общие сведения о системах управления

Согласно [2], в состав типовой системы управления (контроллера), представленной на рис. 61, входят следующие компоненты:

|

|

|

|

|

|

|

Объект управления |

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Устройство |

|

|

ИУ |

|

|

|

|

Цифровой регулятор |

|

|

|

|

Объект |

|

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|||||||

|

|

|

|

сопряжения |

|

|

|

|

или |

|

|

|

|

|

с объектом |

|

|

|

|

процесс |

|

|

|

|

|

|

ИУ |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Пульт управления |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Датчики

164

Рис. 61. Обобщённая структура типового контроллера

1.Объект управления (ОУ), содержащий собственно объект или процесс, исполнительные устройства (ИУ) и систему датчиков контролируемых параметров объекта.

2.Устройство сопряжения с объектом (УСО). Используется для связи цифрового регулятора с датчиками и ИУ, а также обеспечивает согласование сигналов (управляющих и информационных) цифрового регулятора и ОУ.

3.Пульт управления. Предоставляет оператору возможность контролировать параметры ОУ и при необходимости вносить в него коррективы.

4.Цифровой регулятор. Устройство, которое получает необходимую информацию о текущем состоянии ОУ от датчиков, и, в соответствии с заложенным в него алгоритмом управления, вырабатывает управляющие воздействия, поступающие на ОУ через ИУ. Конкретная реализация цифрового регулятора определяется типом системы управления и зависит от сложности ОУ. Большинство цифровых регуляторов реализуются на базе МК, более сложные регуляторы – на базе ВМ, вычислительных комплексов. Существенной особенностью работы цифровых регуляторов в контроллерах является то, что все операции, связанные с ОУ, должны выполняться в реальном масштабе времени при постоянном информационном взаимодействии регулятора с ОУ.

Сложные системы управления включают в контур управления не только ВМ, но и человека и являются не автоматическими, а автоматизированными.

Во всех случаях в системах управления существуют несколько параллельно протекающих процессов. Требования ко времени выполнения у различных процессов различны, а для их выполнения используются общие ресурсы системы, поэтому необходимо чёткое упорядочение выполнения процессов. Для этого установлены абсолютные приоритеты.

В основу организации управления заложена модель реально протекающего дискретного процесса. Реальное непрерывное время делится на кванты τ, длительность кванта задаётся в зависимости от инерционности объекта. В цифровых регуляторах деление времени на кванты осуществляет таймер. Последовательность квантов, отражающая течение времени, нумеруется:

Для программного

Для программного

165

управления объектом при работе с моделью минимально необходимы три компонента: 1) идентификация текущего состояния модели q(i) на основе показаний датчиков; 2) расчёты, связанные с определением следующего состояния q(i+1); 3) формирование управляющих воздействий на ИУ, обеспечивающих переход в состояние q(i+1). По сигналу от таймера происходит прерывание выполняемой в фоновом режиме программы, и осуществляется переход к программам идентификации состояния объекта, расчёта следующего состояния, формирования управляющих воздействий и вывода их на объект. Выполнение этих программ должно завершиться раньше, чем закончится квант. В оставшуюся часть кванта времени выполняются программы, имеющие более низкий приоритет. Процессы периодически повторяются. Привязка инициализации приведённых выше процессов к сигналам от таймера и обеспечивает работу системы управления объектом в режиме реального времени.

Для управления сложными распределёнными в пространстве объектами организуют аппаратно-программные управляющие комплексы с иерархической (двухили трёхуровневой) структурой. На верхнем уровне находятся ВМ, выполняющие роль пультов управления. На нижних уровнях находятся ВМ, непосредственно осуществляющие сбор информации от датчиков, её обработку и формирование управляющих сигналов. Если ОУ находится на значительном расстоянии, то помощью встраиваемых систем на базе МК осуществляется первичная обработка сигналов в непосредственной близости от ОУ, и реализуются алгоритмы локального управления без выхода на ВМ. Обмен между МК и ВМ более высокого уровня выполняется с использованием передачи сообщений на базе стандартных каналов связи.

Далее остановимся на вопросах организации МКС и структуре МК.

11.2.Организация микроконтроллеров и микроконтроллерных систем

Наиболее часто МК используются во встраиваемых системах управления различными объектами. Под встраиваемой системой управления будем понимать систему управления, пространственно приближенную к датчикам и ИУ и конструктивно интегрированную

166

в оборудование – механизм, технологическую установку, робот

ипр. [2].

Всоответствии с [2, 5], МК – это программируемое однокристальное вычислительное устройство со встроенным набором средств для ввода и вывода, применяемое для решения задач управления

ипервичной обработки данных в технических системах. В отличие от универсальной микро-ЭВМ, МК имеют значительно меньший объём памяти и менее разнообразный состав внешних устройств, реализуют несложные алгоритмы.

Встраиваемые средства на базе МК относительно просты, имеют низкую стоимость, малые размеры. Обычно на них возлагают следующие функции:

1) сбор, первичную обработку и преобразование сигналов датчиков объекта в сообщения стандартного формата, передачу их в ВМ;

2) приём, накопление и трансляцию команд управления от ВМ; 3) самодиагностику и первичную диагностику объекта.

Взависимости от сложности задач встраиваемые системы управ-

ления бывают одноуровневыми и многоуровневыми. В последнем слу-

чае на нижнем уровне управления решаются задачи локального управления отдельными подсистемами, а на более высоких – общие задачи управления системой в целом. Одноуровневые системы управления реализуются, как правило, на базе МК, а при построении многоуровневых систем на верхних уровнях используются ВМ для обеспечения интерфейса с человеком-оператором.

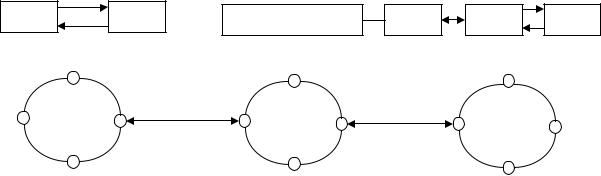

Существуют МКС следующих типов [2]: автономная МКС, локальная МКС, МКС сетевой конфигурации (рис. 62):

МК |

МК |

Пульт оператора |

ВМ |

МК |

ОУ |

|

а |

|

б |

|

|

|

Сеть ВМ |

Сеть МК |

|

Рассредото- |

|

|

|

|

|

ченный ОУ |

|

в

Рис. 62. Типы МКС

а– автономная МКС; б – локальная МКС;

в– МКС сетевой конфигурации

167

Автономные системы управления являются самыми простыми и дешёвыми, но их возможности ограничены. Более сложные локальные МКС обладают большими возможностями при управлении объектами различной природы. Наиболее сложными системами управления являются МКС сетевой конфигурации с распределённым многоуровневым управлением (сеть ВМ и сеть МК) и распределённым (рассредоточенным) ОУ.

По общим архитектурным принципам все МК объединяют в семейства. Все МК одного семейства имеют одинаковое ядро: систему команд, организацию памяти команд и памяти данных, базовый набор внутренних ПУ и систему прерываний.

Типичный МК содержит в своём составе процессорное ядро с развитой системой команд, память программ IROM, регистровый файл (память) данных RRAM, а также набор программируемых интерфейсных схем, выполняющих ряд важных функций внутри МК и обеспечивающих связь с внешней средой (рис. 63)[2, 5].

Большинство из перечисленных блоков являются обязательными компонентами любого МК, некоторые, например, память IROM, могут отсутствовать. Состав и назначение интегрированных на кристалле ПУ определяется областью применения МК. Поэтому эти средства делаются многофункциональными, с программной настройкой на тот или иной режим работы. При инициализации МК информация о типе настройки заносится в специальные регистры и в процессе дальнейшей работы МК обычно не меняется.

Рассмотрим представленные функциональные блоки более детально.

168

|

|

Генератор |

|

|

|

|

|

|

|

|

|

|

|

Адрес/ |

||

|

|

тактовых |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

импульсов |

|

|

|

|

|

|

|

|

|

|

|

данные |

||

|

|

|

|

|

Память |

|

Регистровый |

|

Интерфейс |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

ЦПУ |

|

программ |

|

файл данных |

|

внешней |

Управление |

||||

|

Сторожевой |

|

|

|

|

IROM |

|

RRAM |

|

магистрали |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

таймер |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Средства связи с объектом |

Поддержка систем реального |

|

времени |

Многофункцио- |

|

Последо- |

|

АЦП |

|

Блок тай- |

|

нальные порты |

|

вательный |

|

|

|

|

меров |

|

|

|

|

||||

ввода-вывода |

|

порт |

|

|

|

|

(счётчиков) |

|

|

Мультип- |

|||||

|

|

|

|

|

|

||

|

|

|

|

|

|||

|

|

|

|

лексор |

|

|

|

|

|

|

|

|

|

|

|

КонтролВнутренние лер препрерывания рываний

КонтролВнутренние лер препрерывания рываний

Входы и выходы |

Вход и выход |

Аналоговые |

Входные (вы- |

Внешние |

парал. портов |

послед. порта |

входные сигналы |

ходные) события |

прерывания |

Рис. 63. Функциональная схема МК

1. ЦПУ представляет собой n-разрядный микропроцессор с фиксированной разрядностью и списком команд. Основой ЦПУ является операционный блок, включающий АЛУ и файл регистров. Взаимодействие отдельных блоков МК, как внутри ЦПУ, так и с внутренними ПУ, осуществляется по внутренней шине. В МК применяются как одноадресные, так и многоадресные ЦПУ (см. гл. 4). Система команд типового МК ориентирована на решение задач управления, алгоритмы которых большей частью обеспечивают контроль состояния объекта и реализацию функций логического управления. Доля вычислительных алгоритмов в таких задачах относительно невелика. Наряду с традиционными группами команд (пересылок, арифметических, логических и пр.), система команд МК обычно включает команды операций над отдельными битами. В МК применяются режимы прямой и косвенной адресации. Почти все команды МК выполняются за один такт машинного времени, что позволяет повысить его производительность. В нормальном режиме работы конвейера параллельно выполнению текущей команды производится выборка и декодирование следующей. При выполнении команд переходов в работе конвейера возникает разрыв; время выполнения команды увеличивается на 2 – 4 такта.

Начало выполнения программы инициируется сигналом сброса, после которого МК обращается к адресу стартовой команды. В ходе

169