- •Министерство образования и науки украины

- •1.3 Мпвс с перекрестной коммутацией

- •1.4 Мпвс с многовходовыми озу

- •1.5. Характеристики мпвс

- •1.6 Свойства мпвс

- •2 К о н в е й е р н ы е в с (к в с)

- •2.4 Структура конвейерного процессора

- •3 Вс с матричной структурой

- •4. Матричные процессоры

- •5. Ассоциативные вс (авс)

- •6 Систолические массивы

- •7 Однородные системы и среды

- •8 Многопроцессорная система с программируемой архитектурой (мпспа)

- •9 Функционально распределенные вычислительные системы

- •10.1 Структура соо

- •10.2. Сетевые модели соо

- •10.3. Теорема Джексона

- •10.4. Постановка задач синтеза соо

- •10.5. Синтез соо с заданным временем ответа (с заданной производительностью)

- •10.6. Синтез соо с заданной стоимостью

- •11. Планирование работ в вычислительных системах

- •11.1. Планирование по критерию минимума суммарного времени выполнения работ

- •11.1.3. Эвристический алгоритм планирования работ в вс

- •11.2. Планирование работ по критерию максимальной загрузки устройств

2.4 Структура конвейерного процессора

Рассмотрим структуру и функционирование скалярного конвейерного процессора .

Рис.2.8.

ЦМП- центральная многоблочная память;

БАО- буфер адресов операндов;

АЛУ- конвейеризированные арифметико-логические устройства;

К',К"- коммутаторы памяти и АЛУ соответственно;

БС РОН- блок состояния РОН;

УПК- указатель номера пропущенной команды;

СчК- счетчик команд;

БП- буфер памяти;

1- шина адреса команд;

2- шина управления выполнением команд обращения к памяти;

3- шина заполнения БК;

4- шина смены состояния РОН;

5- шина управления выполнением регистровых команд.

Процессор содержит несколько конвейерных АЛУ. Это позволяет одновременно выполнять смежные арифметико-логические операции, что соответствует реализации не только параллелизма служебных операций, но и локального параллелизма. Для разных операций, АЛУ имеют различную длину конвейера ( в примере она равна 6,7,14 позициям).В процессоре используются команды двух классов: команды обращения в память и регистровые команды для работы с РОН . Буфер команд имеет многостраничную структуру ,что позволяет во время работы УУ с одной страницей производить заранее смену других страниц.

Конвейерный процессор для векторной обработки

Для выполнения операций над векторами также используются арифметические конвейеры

Структура устройства управления (УУ) аналогична структуре УУ скалярного конвейерного процессора (отличия в том, что при векторной команды код операции не меняется).

Главная особенность векторного процессора- наличие ряда векторных регистров V (обычно до 8), каждый из которых позволяет хранить вектор длиной до 64 слов.

Важной особенностью векторных конвейерных процессоров является механизм зацепления, используемый для ускорения вычислений. Зацепление- такой способ вычислений, когда одновременно над векторами выполняется несколько операций.

Быстродействие конвейерного процессора зависит от L - размерности вектора и от n- числа одновременно выполняемых операций.

Структура векторного конвейерного процессора

Рис.2.9.

3 Вс с матричной структурой

В ВС с матричной структурой ускорение достигается не за счет совмещения операций, как в конвейерных ВС, а за счет параллельного во времени исполнения одинаковых этапов команды для разных единиц данных. Чем больше процессоров в таких ВС, тем меньше время выполнения нужной векторной операции. Длительность такта для конвейерных и матричных ЭВМ находится примерно в отношении 1:5.

Итак, матрица процессоров (процессорная матрица)- совокупность идентичных процессорных элементов, объединенных коммутационной сетью.

Эта совокупность элементов называется процессорным полем (ПП) и управляется центральным устройством управления (ЦУУ).

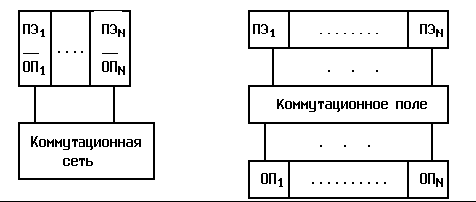

Структура ПП имеет два варианта (рис.3.1):

- с локальной памятью (а);

- с общедоступной памятью (б).

а) б)

Рис.3.1.

Сеть коммутации представляет собой множество связей между на-

борами узлов.

Процессорная матрица (ПМ) с локальной памятью

ПМ

БМ- базовая машина;

ПП- процессорное поле;

ПМ- процессорная матрица;

СМ- системная магистраль;

МД- магистраль данных;

МУ- магистраль управления;

ЦУУ- центральное устройство управления.

Рис.3.2.

Число процессорных элементов от десятков до нескольких тысяч. ЦУУ связано с ПП тремя магистралями:

1) по МД из ЦУУ в ПП передаются общие адреса и данные, а из отдельных ПЭ в ЦУУ производится выборка необходимых единиц информации;

2) по СМ, которая имеет физическую шину на каждый ПЭ, в ПП передается (или считывается вектор активности процессорных элементов.

3) по МУ из ЦУУ всем ПЭ передаются одни и те же микрокоманды для одновременного исполнения.