- •Розділ 1. Суматори і арифметично-логічні пристрої

- •1.1. Однорозрядні суматори

- •1.2. N-розрядні (паралельні)суматори

- •Розділ 2. Основні мікросхемисуматорів

- •2) Об'ємобладнання, що оцінюється кількістю входів, рівному 15 (це одне з кращих значень даного параметра). Рис. 2.1. Схема (а) і умовне графічне позначення (б)однорозрядногосуматора(к155им1)

- •2.1. Мікросхеми к155им2 – к155им3

- •2.2. Мікросхема к155ип3

- •Розділ 3. Модульні операції

- •Висновки

- •Література

2.2. Мікросхема к155ип3

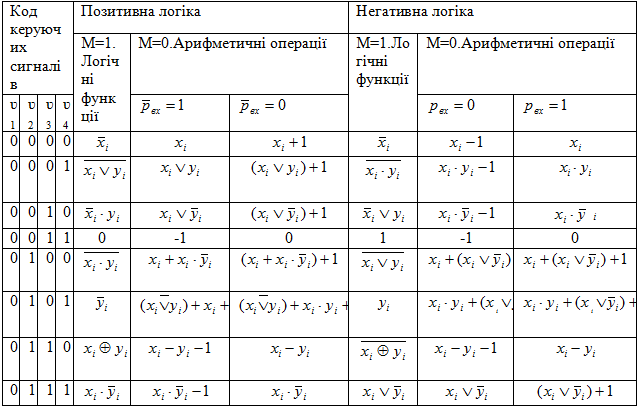

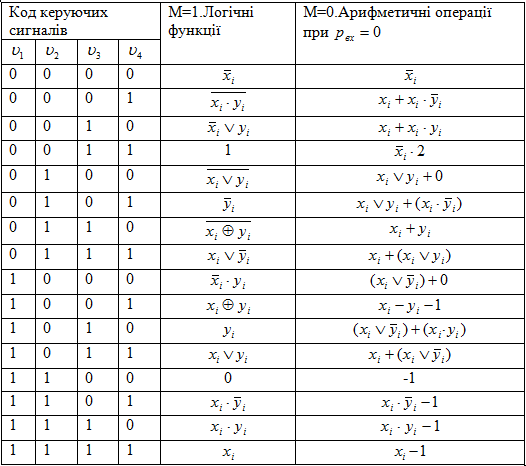

Суматориз одночаснимперенесеннямреалізовані у вигляді спеціальних мікросхем, що виконують функції 4-розрядногоарифметично-логічногопристрою(АЛП(в серії К155 – мікросхема К155ИП3). Умовні графічні позначення мікросхеми К155ИП3 наведені на рис. 2.7, деxi–x1 і уi–у1 – 4‑розрядні коди, що поступають на входи схеми;F4–F1– 4-розрядний код результату (логічної або арифметичної операцій, що виконуються схемою);υ4–υ1– код керуючих сигналів (можливі 24= 16 комбінацій керуючих сигналів, кожна з яких визначає логічну або арифметичну операцію, що виконується схемою );М – керуючий сигнал, якийвизначаєрежим роботи схеми: виконання логічних або арифметичних операцій;рвх,Р, Σ іРгр – входи і виходи одночасного перенесення;хі – уі, – окремий вихід, що є тільки в схемі К155ИП3, сигнал на якому з'являється лише у разі ідентичності вхідних кодів при будь-якому значенні М.

Рис. 2.7. Умовні графічні позначення мікросхеми К155ИП3:

а– в режимі позитивної логіки;б – в режимінегативноїлогіки

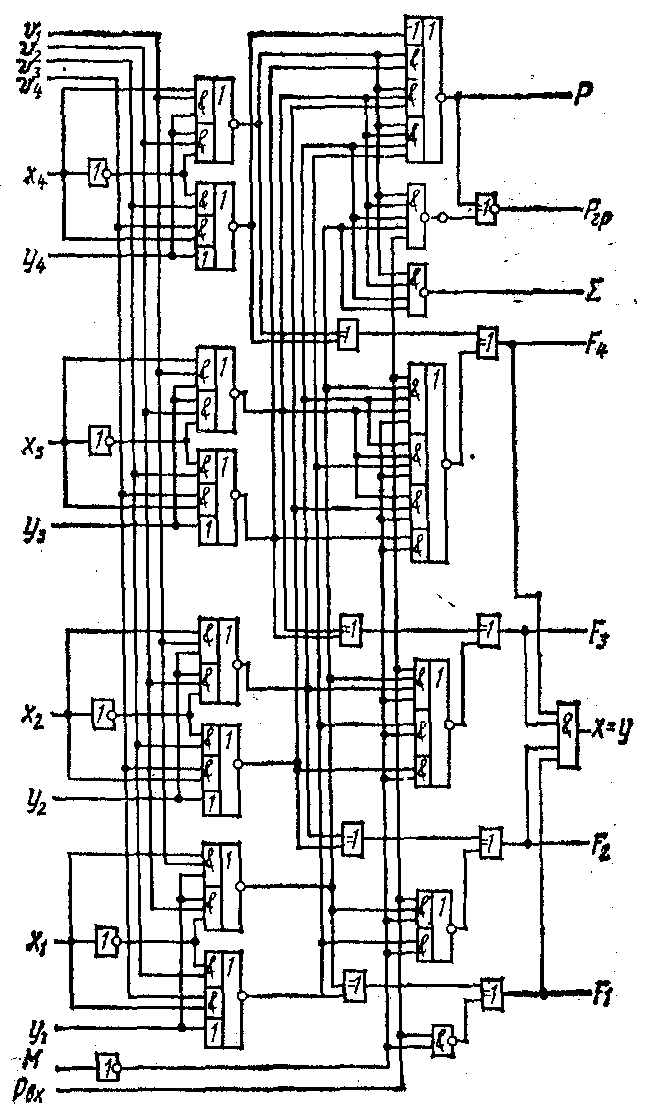

Рис. 2.8. Схема АЛП(К155ИП3)

Мікросхема К155ИП3. Мікросхема може працювати в режимах позитивної логіки інегативноїлогіки (тут верхньому рівню відповідає код «0», нижньому рівень-код «0»).

Умовні графічні зображення мікросхеми К155ИП3, що використовується в режимі позитивної і негативноїлогіки, відповідно показані на рис. 2.7,а,б. Перелік всіх логічних і арифметичних операцій, що виконуються даною мікросхемою,відображенийв табл. 2.2.

Таблиця 2.2

Операції підсумовування в даній мікросхемі виконуються з одночасним перенесенням. Реалізація одночасногоперенесенняв мікросхемі виконана по еквівалентних канонічних рівняннях.

Рис. 2.9. Схема (а) прискореногопоширенняперенесеннядля АЛП(К155ИП4)

і її умовне графічне позначення (б)

У загальномувиглядіканонічні рівняння одночасногоперенесеннявиглядають так:

![]() ,

,![]() ;

;

У мікросхемі, що розглядається,реалізовані рівняння:

для позитивної логіки

![]() ,

,![]() ;

;

для негативної логіки

![]() ,

,![]() ;

;

Реалізація в мікросхемі саме даних рівнянь є результатом емпіричного підходу (направленого перебору варіантів). Прицьомувраховувалисяпитаннятехнологічностівиготовлення мікросхеми, зменшенняоб'ємуобладнанняі часу затримки вихідних сигналівпризабезпеченні виконання всіх передбачених арифметичних і логічних операцій.

Схема АЛП,наведенана рис.

2.8, реалізована наодномукристалі, де використане 5інверторів;

33 схеми І з числом входів 2-4; 13 схем АБО-НІ

з числом входів 2-4; 2чотиривходовісхеми І – НІ; 8 схем

![]() .

.

Розглянемотимчасові параметри схеми. Код результату будь-якої логічної або арифметичної операціїз'являєтьсяна виході (з моменту одночасної подачі вхідних сигналів) через 24 нс.ПоширенняперенесеннявідрвхдоРгр відбуваєтьсяза 10,5 нс;tзд.рсигналу відхі,уі доРгррівний 15 нс;tзд.рвідхі,уі дорвх рівний 23 нс;tзд.рвідрвхдоFірівний 12нс. На основі даної мікросхеми легко реалізовуєтьсяп‑розряднийсуматорз послідовнимпоширеннямперенесенняміж групами (див. рис. 2.5,б). Тут не потрібно додатковогообладнання. Максимальнийчаспідсумовуванняп-розрядних кодів (п = 40) рівний

01010…0101

00110…1011

___________

10000…000

Мікросхема К155ИП4. У серії К155 для реалізації п-розряднихсуматорівз одночасним багатоступінчастимперенесеннямвипускається спеціальна мікросхема К155ИП4 – схема прискореногопоширенняперенесеннядля арифметичного вузла. Умовне графічне позначення схеми, що використовується в режимі позитивної логіки,наведенена рис. 2.9,б. Розмірність цієї схемиm= 4 і функції, що виконуються нею, визначаються рівняннями (2.9). Ця мікросхема, що так само як і об'єднувана з нею мікросхемаАЛП, реалізована не по канонічних рівняннях.Роботамікросхеми К155ИП4 в режимінегативноїлогіки визначається рівняннями

![]()

![]() ;

;

![]() ;

;

і наведенана рис. 2.9,а. Мікросхема реалізована, на 13 схемах І,одномуінверторі, двох схемах АБО і трьох схемах АБО – НІ. Тимчасові параметри мікросхемиtзд.рвід будь-якого входу до будь-якого виходу рівні 22 нс.

Схема 16-розрядного суматора,побудованана

мікросхемах К155ИП3 і К155ИП4,наведенана рис. 2.10.

Рис. 2.10. Схема 16-розрядного суматора,

побудованана мікросхемах К155ИП3 і К155ИП4

Рис. 2.11. Умовні графічні позначення мікросхем К500181 (а) і К500179 (б)

Мікросхеми К500ІП181 і К500ІП179.

Мікросхеми випускаються в серії К500. Вони виконують функції, аналогічні мікросхемам К155ИПЗ і К155ИП4 відповідно. Умовні графічні позначення мікросхем К500181 і К500179наведеніна рис. 2.11. Функції, що виконуються мікросхемою К500181 в режимі позитивної логіки,наведенівтабл.2.3.

Мікросхеми серії, К500 мають деякі

відмінності від відповідних мікросхем

серії К155: мікросхема К500181 в режимі

позитивної логіки реалізовує функції

Р, Σ,Pгр= f (xi,

yi, рвх)

іF= (x1

![]() y1)

y1)

![]() рі–1;

мікросхема К500179 – функціїP1,P2,Р і Σ відРі,

Σі, 2*,pвх, мікросхема

К500179 має не три виходиP1, P2,P3(як в мікросхемі К155ИП4), а

два.

рі–1;

мікросхема К500179 – функціїP1,P2,Р і Σ відРі,

Σі, 2*,pвх, мікросхема

К500179 має не три виходиP1, P2,P3(як в мікросхемі К155ИП4), а

два.

Таблиця 2.3

Канонічні рівняння, відповідно до яких виробляються сигнали на виходах P1 іP2, маютьвигляд:

![]()

![]()

Схема 16-розрядного суматора,побудованана мікросхемах К500181 і К500179,наведенана рис. 2.12. Тут нарівні з одночаснимперенесенняммає місце послідовнепоширенняперенесенняміжАЛП1 іАЛП2 і міжАЛП3, іАЛП4.

Рис. 2.12. Схема 16-розрядного суматора,