- •Список прийнятих скорочень

- •1. Математичні основи цифрової техніки

- •1.1. Відображення інформації у цифровій техніці

- •1.2. Системи числення та кодування

- •1.3. Перетворення числової інформації

- •1.4. Двійкова арифметика

- •1.5. Основні поняття та закони бульової алгебри

- •1.6. Визначення та позначення логічних функцій.

- •1.7. Форми зображення логічних функцій.

- •2. Імпульсні схеми на логічних елементах.

- •2.1. Загальні відомості.

- •2.2. Формувачі імпульсів.

- •2.3. Генератори імпульсів.

- •3. Комбінаційні пристрої цифрової техніки.

- •3.1. Шифратори.

- •3.2. Дешифратори.

- •3.3. Мультиплексори.

- •3.4. Демультиплексори.

- •4. Арифметичні пристрої.

- •4.1. Комбінаційні суматори.

- •4.2. Накопичувальні суматори.

- •5. Послідовні пристрої цифрової техніки.

- •5.1. Тригер – двостановий запам’ятовувач інформації.

- •5.2. Класифікація тригерів.

- •5.3. Різновиди тригерів.

- •5.4. Регістри.

- •6. Лічильники.

- •6.1. Загальні відомості.

- •6.2. Класифікація лічильників.

- •6.3. Лічильники з послідовним переносом.

- •6.4. Лічильники з паралельним переносом.

- •6.5. Реверсивні лічильники.

- •6.6. Лічильники з довільним модулем лічби.

- •6.7. Кільцеві лічильники. Лічильник Джонсона.

- •7. Цифро-аналогові та аналого-цифрові перетворювачі

- •7.1. Загальні відомості.

- •7.5. Перемножувальний цап.

- •7.7. Ацп послідовного наближення.

- •7.8. Ацп паралельного кодування.

- •7.9. Ацп подвійного інтегрування.

- •8.1. Загальні відомості.

- •8.2. Оперативні запам’ятовуючі пристрої.

- •8.3. Постійні запам’ятовувальні пристрої.

- •8.4. Програмовані логічні матриці.

- •Література.

- •Додатки.

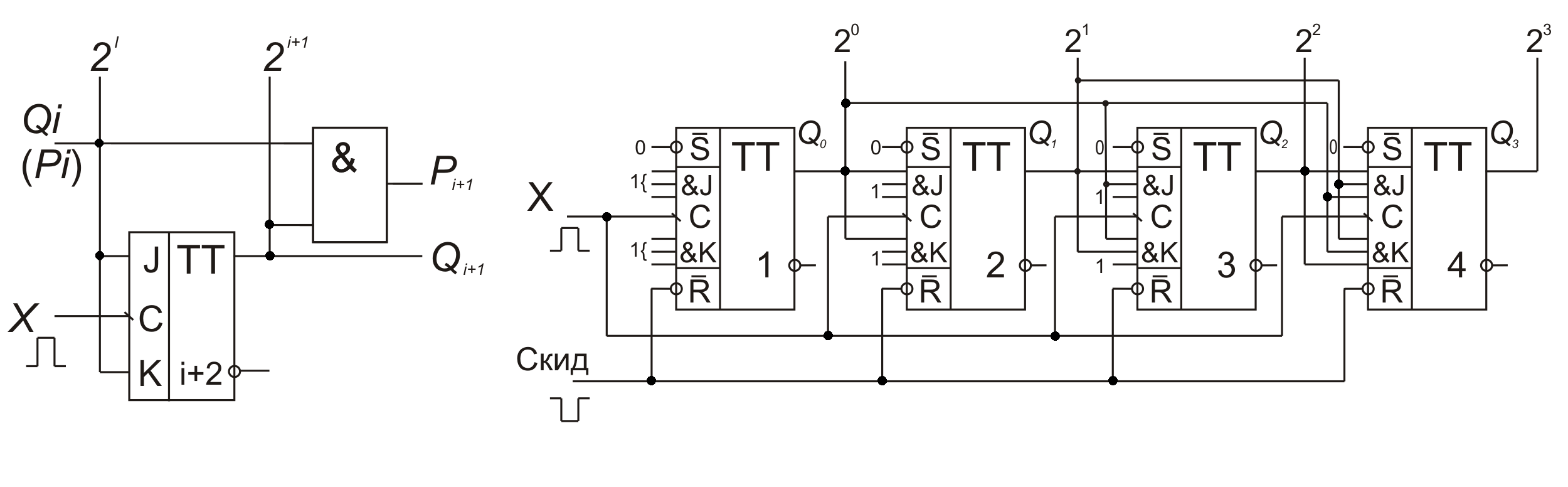

6.4. Лічильники з паралельним переносом.

Це

синхронні лічильники, у яких вхідні

сигнали (імпульси) ![]() приходять на синхровходи

приходять на синхровходи

![]() тригерів в усіх розрядах

одночасно (паралельно) будуються вони,

як правило. Не базі двоступеневих RS-,

JK-

або D-тригерів.

тригерів в усіх розрядах

одночасно (паралельно) будуються вони,

як правило. Не базі двоступеневих RS-,

JK-

або D-тригерів.

На

рис.6.2,а

з метою ілюстрації способу паралельного

(наскрізного) переносу показано фрагмент

схеми формування одного розряду

лічильника, а на рис.6.2,б

− функціональну схему чотирирозрядного

синхронного лічильника (зa

модулем 16), що побудований на базі

універсальних JK-тригерів,

у яких використано потроєні входи

тригерів ![]() і

і ![]() .

.

а) б)

Рис. 6.2. Лічильник з паралельним переносом.

Суть

способу паралельного (наскрізного)

переносу полягає у тому, що імпульс

переносу ![]() з попереднього розряду

з попереднього розряду

![]() лічильника подається одночасно на

інформаційні входи

лічильника подається одночасно на

інформаційні входи ![]() і

і ![]() даного (

даного (![]() )

− тригера і на вхід

схеми збігу, керуючий вхід якого

під’єднаний до прямого виходу цього

тригера. Імпульс переносу

)

− тригера і на вхід

схеми збігу, керуючий вхід якого

під’єднаний до прямого виходу цього

тригера. Імпульс переносу ![]() на виході схеми збігу

з’явиться

лише у тому випадку, коли

на виході схеми збігу

з’явиться

лише у тому випадку, коли ![]() .

Після формування переносу даний тригер,

як і у послідовному лічильнику, по зрізу

вхідного імпульса, що подаються на вхід

.

Після формування переносу даний тригер,

як і у послідовному лічильнику, по зрізу

вхідного імпульса, що подаються на вхід

![]() ,

повернеться у стан 0. Наступний вхідний

імпульс стан цього тригера не змінить,

а лише при появі фронту

,

повернеться у стан 0. Наступний вхідний

імпульс стан цього тригера не змінить,

а лише при появі фронту

![]() переведе його перший

ступінь (тобто його М-тригер) у стан 1.

Таким чином, імпульс переносу проникатиме

тільки до того розряду лічильника,

тригер якого знаходиться у стані 0, тобто

у режимі запису інформації, і який під

дією імпульсу переносу треба перевести

у стан 1.

переведе його перший

ступінь (тобто його М-тригер) у стан 1.

Таким чином, імпульс переносу проникатиме

тільки до того розряду лічильника,

тригер якого знаходиться у стані 0, тобто

у режимі запису інформації, і який під

дією імпульсу переносу треба перевести

у стан 1.

Перший

розряд синхронного лічильника змінює

свій стан на протилежний під дією кожного

вхідного імпульсу і участі у формуванні

імпульсу переносу не бере (на його входах

![]() ).

Наступні розряди лічильника змінюють

свій стан на протилежний під дією вхідних

імпульсів

).

Наступні розряди лічильника змінюють

свій стан на протилежний під дією вхідних

імпульсів ![]() тільки тоді, коли з

прямих виходів

тільки тоді, коли з

прямих виходів ![]() попередніх тригерів на кон’юнктивні

входи

попередніх тригерів на кон’юнктивні

входи ![]() і

і ![]() подається дозволяючий

рівень 1. Для побудови віднімального

лічильника з паралельним переносом

досить у розглянутій схемі замінити

виходи у тригерах всіх розрядів

подається дозволяючий

рівень 1. Для побудови віднімального

лічильника з паралельним переносом

досить у розглянутій схемі замінити

виходи у тригерах всіх розрядів ![]() на

на

![]() .

.

Швидкодія

роботи синхронних лічильників значно

вища, ніж асинхронних. Час реєстрації

розглянутих синхронних лічильників

дорівнює часу перемикання одного тригера

![]() .

Готовність до зчитування результату з

регістра синхронного лічильника, таким

чином, визначається паузою між вхідними

імпульсами. Тому розрізняльне здатність

лічильника

.

Готовність до зчитування результату з

регістра синхронного лічильника, таким

чином, визначається паузою між вхідними

імпульсами. Тому розрізняльне здатність

лічильника ![]() підвищується тільки у

випадку, коли час спрацювання

підвищується тільки у

випадку, коли час спрацювання ![]() ЛЕ менший за час перемикання тригера

ЛЕ менший за час перемикання тригера

![]() .

Отже, чим менший період проходження

.

Отже, чим менший період проходження ![]() вхідних імпульсів, тим вища розрізняльна

здатність

вхідних імпульсів, тим вища розрізняльна

здатність ![]() лічильника, тобто тим швидше синхронний

лічильник реагуватиме на зміну числа

вхідних імпульсів, які він має підрахувати

і зареєструвати на своєму регістрі.

Отже, розрізняльна здатність синхронного

лічильника

лічильника, тобто тим швидше синхронний

лічильник реагуватиме на зміну числа

вхідних імпульсів, які він має підрахувати

і зареєструвати на своєму регістрі.

Отже, розрізняльна здатність синхронного

лічильника

![]() ,

(6.2)

,

(6.2)

де ![]() − необхідна умова оптимальної роботи

синхронного лічильника;

− необхідна умова оптимальної роботи

синхронного лічильника; ![]() − тривалість активного

перепаду вхідного імпульсу.

− тривалість активного

перепаду вхідного імпульсу.

Останній

JK-тригер

4 розглянутого синхронного лічильника

має всі заповнені кон’юнктивні входи

![]() і

і![]() .

Це означає, то із

збільшенням розрядності лічильника

виникає необхідність у застосуванні

зовнішніх ЛЕ. Це ускладнює схему і

зменшує переваги багатовходових

JK-тригерів.

.

Це означає, то із

збільшенням розрядності лічильника

виникає необхідність у застосуванні

зовнішніх ЛЕ. Це ускладнює схему і

зменшує переваги багатовходових

JK-тригерів.

Для

отримання великих значень модуля лічби

![]() застосовують каскадне

з’єднання

лічильників. Для цього їх розбивають

на групи, кожну з яких будують за принципом

лічильника з паралельним переносом.

Лічильники з груповим переносом є

найбільш швидкодіючими − час реєстрації

дорівнює

застосовують каскадне

з’єднання

лічильників. Для цього їх розбивають

на групи, кожну з яких будують за принципом

лічильника з паралельним переносом.

Лічильники з груповим переносом є

найбільш швидкодіючими − час реєстрації

дорівнює ![]() ,

а розрізняльна здатність

,

а розрізняльна здатність

![]() (6.3)

(6.3)

де ![]() − число

груп лічильника.

− число

груп лічильника.

Повний цикл роботи лічильника визначається періодом його роботи, після якого він повертається у початковий (нульовий) стан. У кінці циклу після заповнення всіх розрядів регістра, тобто при 11..1, черговий імпульс встановлює лічильник у нульовий стан і його робота поновлюється. Якщо вхідні імпульси подаються на вхід лічильника неперервно, тобто на розрядах його регістра відбувається неперервний підрахунок кількості імпульсів і скид в нуль, такий режим роботи лічильника називається циклічним.