- •1Лабороторна робота №1 аналіз і синтез комбінаційних схем

- •1.1 Основні положення

- •1.2 Варіанти індивідуальних завдань

- •1.3 Загальні зауваження до виконання індивідуальних завдань

- •1.4 Порядок виконання роботи

- •1.5 Зміст звіту

- •1.6 Література

- •2 Лабороторна робота №2 комбінаційні схеми

- •2.1 Варіанти індивідуальних завдань

- •2.2 Порядок виконання роботи

- •2.3 Зміст звіту

- •Лабораторна робота № 3 регістри й лічильники на основі тригерів. Аналіз і синтез

- •3.1 Регістри.Основнiположення

- •3.2 Лічильники. Основні положення

- •3.3 Індивідуальні завдання. Дослідження готових імс регістрів і лічильників в інтегральному виконанні

- •3.4 Порядок виконання роботи

- •3.5 Зміст звіту

- •3.5 Література

- •4 Лабороторна робота №4 аналіз і синтез моделей цифрових автоматів

- •4.1 Основні положення

- •4.1.1 Математичні моделі цифрових автоматів

- •4.1.2 Табличний спосіб завдання ца

- •4.1.3 Канонічний метод синтезу ца

- •4.1.4 Приклад синтезу ца канонічним методом

- •4.1.5 Завдання ца графом

- •4.2 Приклад синтеза ца із «жорсткою» логікою управління

- •4.2.1 Принцип роботи мікропрограмного автомата із жорсткою логікою управління

- •4.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

- •4.3 Варіанти індивідуальних завдань (із)

- •4.4 Зміст звіту

2.2 Порядок виконання роботи

Для виконання роботи необхідно:

- добудувати ТІ згідно завдання;

- скласти та мінімізувати отримані логічні функції функції;

- забезпечити в середовищі EWB на «робочому столі» ПК: відповідну комутацію входів, виходів ІС, підключення живлення, кнопок і тумблерів комутації, віртуальних вимірювальних приладів (двухканального осцилографа, амперметра, вольтметра, генератора слів, логічного аналізатора, ін. при необхідності) і одержати діаграми функціонування, щопідтверджують ТІ;

- при утрудненнях у виконанні ЛР скористатися літературою, що зазначена в роботі й наприкінці методичних вказівок.

2.3 Зміст звіту

2.3.1 Короткий інформаційно-аналітичний огляд суті завдання.

2.3.2 Добудовані повні ТІ пристроїв за відповідними завданням рисунками, їх ДНФ (КНФ), мінімізація або спрощення складених функцій.

2.3.3 Реалізація відповідних схем на основі наявних у БМ програми EWB схем (у вигляді електричної схеми, її креслення, перевірки її функціонування):

а − мінімального базису АБО-НІ, НІ (стрілка Пірса);

б − мінімального базису І-НІ, НІ (штрих Шеффера);

в − розширеного базису АБО-НІ, НІ, І-НІ(базис Буля).

Для цього необхідно вибрати із складу наявних цифрових ІС у БМ програми EWB зазначені схеми.

2.3.4 Характеристика, призначення входів і виходів, умовне позначення обраної ІС (позначення входів, виходів, цокльовка виводів); назва, тип логіки, напруга живлення й аналоги (наприклад: схеми АБО-НІ, І-НІ реалізовані наборами ІС типу 74…,741…,742…, ін. варіанти).

2.3.5 Аналіз і обґрунтування вибору зі складу наявних цифрових ІС (БМ програми EWB) мікросхем, що відповідають заданій ТІ або їх розширені функціональні варіанти. Характеристика й призначення входів і виходів, умовне позначення ІС (позначення входів, виходів, цокльовка виводів); назва, тип логіки й аналог СНД (наприклад: порівняння схеми з рис 2.2 з інтегральною схемою 74148 пріоритетного шифратора 83, її СНД аналогК155ВЕРБ1, визначення типу логіки, указання аналогів в інших серіях ІС).

2.3.6 Висновки до роботи.

Лабораторна робота № 3 регістри й лічильники на основі тригерів. Аналіз і синтез

Метою лабораторної роботи №3 є:

- знайомство із принципом дії регістрів і лічильників різних типів;

- оволодіння методикою синтезу паралельних і послідовних регістрів і їхніх комбінацій; синхронних прямих, зворотних (з довільним модулем рахунку) і реверсивних лічильників;

- ознайомлення з особливостями роботи типових схем регістрів і лічильників в інтегральному виконанні на різних типах мікросхем.

3.1 Регістри.Основнiположення

Послідовністні схеми регістрів виконуються на основі тригерів і мають такі основні типи:

- з паралельним входом і виходом-регістр пам`яті(Р.Пар.Вх.Пар.Вих. інформація при завантаженні,розвантаженні входи/виходирегiстру надходить одночасно-паралельно);

- з паралельним входом і послідовним виходом (Р.Пар.Вх.Посл.Вих. інформація при завантаженні регістру навсi йоговходи надходить одночасно-паралельно, а прирозвантаженнінадходить з одного виходу послідовно біт за бітом);

-з послідовним входом і паралельним виходом (Р.Посл.Вх.Пар.Вих. інформація при завантаженні надходить на один вхід послідовно, а прирозвантаженнізнімається одночасно-паралельно з усіх його розрядів-виходів);

- з послідовними входом і виходом (Р.Посл.Вх.Вих. інформація подається на один вхід при його завантаженні та знімається з одного виходу при йогорозвантаженніпослідовнобіт за бітом);

- комбінаційні з різними засобами приймання/видаванняінформації. Вони поділяються на однофазні (сигнал передається по одному каналу) і паро фазніпо двох каналах (прямий, обернений код).

Функція регістрів зберігання, зсув даних і отримання прямих, обернених і доповняльних кодів.

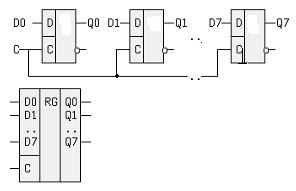

Аналіз паралельних регістрів (1, 2

варіант). Регістри з паралельним

входом/виходом (тип1) називаються

регістрами пам’яті і використовуються,

як прозорі тригери типу«затвор»та тригери з динамічним керуванням. На

рис. 3.1приведена схема

8-ми розрядного паралельного регістру

пам’яті (що

виконаний на 8-миD-тригерах:

схеми 7477, 7475) із загальним входом керування

записом інформації і його умовне

позначення. Високий рівень на входіC

переписує інформацію з входуDна вихідQ(Di=Qi),

низький рівень зберігає дані за«затвором». Дані зберігаються

або зчитуються з виходівQi

тригерів на наступному кроці

виконання алгоритму, наприклад

«додати до суматора вміст регістру А».

Обернений код даних в регістрі присутній

по виходах![]() .

До регістрів типу 2 відноситься 8-ми

розрядний регістр, реалізований на

схемі 74165(3, 4 варіант).

.

До регістрів типу 2 відноситься 8-ми

розрядний регістр, реалізований на

схемі 74165(3, 4 варіант).

Рисунок 3.1 – Схема 8-ми розрядного регістру пам’яті

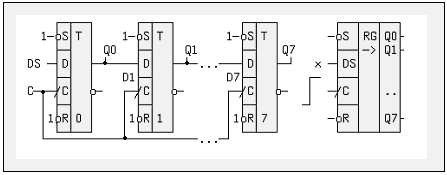

Аналіз послідовних регістрів (3, 4 варіант). Такі регістри зсуву (рис. 3.2, тип 3, 4) виконуються на основі тригерів із динамічною синхронізацією (справедливо для регістрів з одним тактовим сигналом). У двотактних можна використати і прозорі регістри типу«затвор».Функція запису вn-розрядному регістрі зсуву наD-тригерах задається у вигляді умов:D0=DS, Di=Q(i−1); i=1, 2, …, n−1.

Рисунок 3.2 −Варіант послідовного регістру, тип 2:DS −вхід послідовного запису,RіS−входи попередньої установки

Із

приходом чергового позитивного фронту

синхроімпульсу C, сигнал із входуi-го тригера через часtзт.п.

з’явиться на його виході і піде на

вхід наступного (![]() )-го

тригера. Однак, на його вихід ця інформація

не перепишеться, тому що тривалість

активного фронтуt(0,1)менше

)-го

тригера. Однак, на його вихід ця інформація

не перепишеться, тому що тривалість

активного фронтуt(0,1)менше![]() .

На цьому процес зсуву даних на один

розряд закінчиться до приходу наступного

позитивного фронту тактового сигналу.

Звідси зрозуміло, чому не можна використати

тригери зі статичним керуванням. Щораз

при

.

На цьому процес зсуву даних на один

розряд закінчиться до приходу наступного

позитивного фронту тактового сигналу.

Звідси зрозуміло, чому не можна використати

тригери зі статичним керуванням. Щораз

при![]() весь ланцюжок виявиться прозорим від

входуDSдо виходуQ7 і значенняDS=D0

буде записано в усі тригери

послідовного регістру. В умовних

позначеннях регістрів зсуву напрямок

стрілки, що вказує зсув, умовний. У різних

довідниках її напрямок дається по-різному.

Умовно приймається, що зсув робиться

від молодшого розряду до старшого.

Практичні схеми регістрів доповнюються

схемами, що підключають до кожного

тригера, які мають вхід паралельного

записуDi, загальний вхід дозволу

записуLі загальний асинхронний

вхід скидання в 0 (R) всіх тригерів.

Ці схеми підключаються до незадіяних

входівRi,Si

тригерів. За подібною схемою виконаний

регістр 74164(5, 6 варіант).Уяву проуніверсальні регістри зсуву(тип

5) дає опис Generic 4-bit Universal Shift Register з БМEWB(7, 8 варіант).

весь ланцюжок виявиться прозорим від

входуDSдо виходуQ7 і значенняDS=D0

буде записано в усі тригери

послідовного регістру. В умовних

позначеннях регістрів зсуву напрямок

стрілки, що вказує зсув, умовний. У різних

довідниках її напрямок дається по-різному.

Умовно приймається, що зсув робиться

від молодшого розряду до старшого.

Практичні схеми регістрів доповнюються

схемами, що підключають до кожного

тригера, які мають вхід паралельного

записуDi, загальний вхід дозволу

записуLі загальний асинхронний

вхід скидання в 0 (R) всіх тригерів.

Ці схеми підключаються до незадіяних

входівRi,Si

тригерів. За подібною схемою виконаний

регістр 74164(5, 6 варіант).Уяву проуніверсальні регістри зсуву(тип

5) дає опис Generic 4-bit Universal Shift Register з БМEWB(7, 8 варіант).

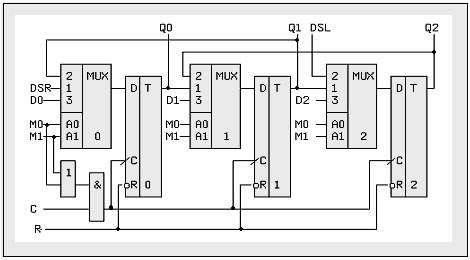

Реверсивний

регістр зсуву даних.Зсув даних від

розряду до розряду може робитися, як в

одну сторону, так і в іншу. Одна з можливих

схем реверсивного регістру зсуву на

три розряди даних із двома послідовними

інформаційними входами для зсуву

інформації вліво DSL і вправо DSR, з

паралельними входами запису![]() ,

входом синхроімпульсів C, входом R

установки в 0 усіх тригерів і двома

входами вибору режиму M1, M0, приведена

на рис. 3.3.

,

входом синхроімпульсів C, входом R

установки в 0 усіх тригерів і двома

входами вибору режиму M1, M0, приведена

на рис. 3.3.

Рисунок 3.3 − Варіант реверсивного трирозрядного регістру зсуву (тип 5)

До

D-входу будь-якого розряду, за винятком

крайніх, підключені, через входи 1 і 2

мультиплексори, виходи лівого і правого

сусідніх тригерів. Якщо![]() ,

а

,

а![]() ,

то до входівDпідключені перші входи

мультиплексорів і інформація в кожний

тригер, крім нульового, записується від

лівого сусіда (відбувається зсув вправо).

ВхідDSRслужить, у цьому режимі, для

послідовного введення інформації. Якщо

,

то до входівDпідключені перші входи

мультиплексорів і інформація в кожний

тригер, крім нульового, записується від

лівого сусіда (відбувається зсув вправо).

ВхідDSRслужить, у цьому режимі, для

послідовного введення інформації. Якщо![]() ,

,![]() ,

то до входівDпідключені інші входи

мультиплексів і інформація в кожний

тригер, крім останнього, записується

від правого сусіда, відбувається зсув

вліво. Для послідовного введення даних

у цьому режимі використовується вхідDSL. При

,

то до входівDпідключені інші входи

мультиплексів і інформація в кожний

тригер, крім останнього, записується

від правого сусіда, відбувається зсув

вліво. Для послідовного введення даних

у цьому режимі використовується вхідDSL. При![]() робиться паралельний запис

робиться паралельний запис![]() позитивним

фронтом тактового сигналу. Для зберігання

інформації необхідно подати комбінацію

позитивним

фронтом тактового сигналу. Для зберігання

інформації необхідно подати комбінацію![]() .

У цьому випадку доD-входів тригерів

підключаться нульові входи мультиплексів

(на схемі не показані). Щоб не відбулося

несанкціонованого запису схеми2АБО

і 2І забороняє в цьому режимі (

.

У цьому випадку доD-входів тригерів

підключаться нульові входи мультиплексів

(на схемі не показані). Щоб не відбулося

несанкціонованого запису схеми2АБО

і 2І забороняє в цьому режимі (![]() )проходження синхроімпульсівС. За

такою схемою виконаний 8-розрядний

регістр 1533ИР13.

)проходження синхроімпульсівС. За

такою схемою виконаний 8-розрядний

регістр 1533ИР13.