- •1Лабороторна робота №1 аналіз і синтез комбінаційних схем

- •1.1 Основні положення

- •1.2 Варіанти індивідуальних завдань

- •1.3 Загальні зауваження до виконання індивідуальних завдань

- •1.4 Порядок виконання роботи

- •1.5 Зміст звіту

- •1.6 Література

- •2 Лабороторна робота №2 комбінаційні схеми

- •2.1 Варіанти індивідуальних завдань

- •2.2 Порядок виконання роботи

- •2.3 Зміст звіту

- •Лабораторна робота № 3 регістри й лічильники на основі тригерів. Аналіз і синтез

- •3.1 Регістри.Основнiположення

- •3.2 Лічильники. Основні положення

- •3.3 Індивідуальні завдання. Дослідження готових імс регістрів і лічильників в інтегральному виконанні

- •3.4 Порядок виконання роботи

- •3.5 Зміст звіту

- •3.5 Література

- •4 Лабороторна робота №4 аналіз і синтез моделей цифрових автоматів

- •4.1 Основні положення

- •4.1.1 Математичні моделі цифрових автоматів

- •4.1.2 Табличний спосіб завдання ца

- •4.1.3 Канонічний метод синтезу ца

- •4.1.4 Приклад синтезу ца канонічним методом

- •4.1.5 Завдання ца графом

- •4.2 Приклад синтеза ца із «жорсткою» логікою управління

- •4.2.1 Принцип роботи мікропрограмного автомата із жорсткою логікою управління

- •4.2.2 Приклад проектування мікропрограмного автомата із жорсткою логікою управління

- •4.3 Варіанти індивідуальних завдань (із)

- •4.4 Зміст звіту

3.2 Лічильники. Основні положення

Лічильником

називають цифровий пристрій (цифровий

автомат), сигнали на виході якого, у

певному коді, відображають число

імпульсів, що надійшли на рахунковий

вхід. Крім того, у лічильниках виконуються

такі мікрооперації, як установка у

вихідний стан, зберігання й видача слів.

По мірі надходження вхідних сигналів

лічильник послідовно міняє свої стани,

утворені комбінаціями станів тригерів

з рахунковим входом. Число дозволених

станів лічильника називають модулем

рахунку,коефіцієнтом перерахуванняабоємністюM (у загальному

випадку![]() ,

деn- число тригерів або двійкових

розрядів лічильника). Лічильники

класифікують за значенням модуля,

напрямком рахунку й способом організації

міжрозрядних зв’язків.

,

деn- число тригерів або двійкових

розрядів лічильника). Лічильники

класифікують за значенням модуля,

напрямком рахунку й способом організації

міжрозрядних зв’язків.

За

значенням модуля рахунку розрізняють:

двійкові(![]() ),двійково-кодовані з довільним модулем,з одинарним кодуваннямі ін.

),двійково-кодовані з довільним модулем,з одинарним кодуваннямі ін.

За напрямком рахунку: підсумовуючі (прямого рахунку -Up-counter), що віднімають (зворотного рахунку -Down-counter) іреверсивні (Up-Down-counter).

За способом організації міжрозрядних зв’язків розрізняють лічильники з послідовним,паралельнимікомбінованимпереносами.

Крім того, всі перераховані типи лічильників прийнято ділити на два види: синхроннійасинхронні. При цьому в асинхронних лічильниках зміна його стану, викликана впливом чергового імпульсу, характеризується послідовною у часі зміною станів тригерів (як правило, це лічильники з послідовним переносом). У синхронних лічильниках зміна станів характеризується одночасною у часі зміною станів його тригерів. У цій якості синхронні лічильники утворять один з видів синхронних автоматів, тому до них може бути застосована й стандартна методика синтезу цього класу автоматів.

Визначимо деякі закономірності двійкових лічильників. Відповідність між числом вхідних імпульсів і станами 3-розрядного двійкового лічильника (прямій і зворотний рахунок) представлена в табл. 3.1. Розглядаючи її для прямого рахунку, можна відзначити дві закономірності:

- значення змінної Qiзмінюється тоді, коли змінна в сусідньому молодшому розрядіQi-1 переходить зі стану «1» у стан «0».

- значення вихідний змінної Qiзмінюється при надходженні чергового імпульсу рахунку в тому випадку, коли змінні у всіх молодших розрядахQi-1, …,Q1 перебувають у стані «1».

Таблиця 3.1 − Відповідність між числом вхідних імпульсів і станами 3-розрядного двійкового лічильника

|

Число вхідних імпульсів |

Підсумовуючий |

Що віднімає | ||||

|

|

Q3 |

Q2 |

Q1 |

Q3 |

Q2 |

Q1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

0 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

1 |

|

5 |

1 |

0 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

0 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

Перша закономірність указує на можливість реалізації лічильника асинхронного типу, друга дозволяє побудувати синхронний лічильник. Для лічильника, що віднімає, аналогічні закономірності можна сформулювати так:

- значення вихідний змінної Qiзмінюється, коли змінна в сусідньому молодшому розрядіQi-1 переходить зі стану «0» в «1».

- значення вихідний змінної Qiзмінюється при надходженні чергового імпульсу рахунку у випадку, коли всі змінні в попередніх молодших розрядахQi-1, ...,Q1 перебувають у стані «0».

Асинхронні

послідовні лічильники будуються у

вигляді ланцюжка тригерів з рахунковим

входом (JK-тригер зJ=K=1 абоD-тригер

з інверсним зворотним зв’язком,![]() ),

коли тактовий вхід кожного наступного

підключений до виходуQабо

),

коли тактовий вхід кожного наступного

підключений до виходуQабо![]() попереднього, що залежить як від напрямку

рахунку, так і від типу входу тригера,

що тактує. Схема підсумовуючого

лічильника наJK-тригерах і часовій

діаграмі його роботи наведені на рис.

3.4. Якщо тактові входиJK-тригерів

з’єднати з інверсними виходами попередніх

тригерів, то вийде схема лічильника, що

віднімає. Аналогічно, якщо в схемі

лічильника, що віднімає, наD-тригерах

(рис. 3.5) тактові входи тригерів з'єднати

з інверсними виходами попередніх

тригерів, то лічильник стане підсумовуючої.

попереднього, що залежить як від напрямку

рахунку, так і від типу входу тригера,

що тактує. Схема підсумовуючого

лічильника наJK-тригерах і часовій

діаграмі його роботи наведені на рис.

3.4. Якщо тактові входиJK-тригерів

з’єднати з інверсними виходами попередніх

тригерів, то вийде схема лічильника, що

віднімає. Аналогічно, якщо в схемі

лічильника, що віднімає, наD-тригерах

(рис. 3.5) тактові входи тригерів з'єднати

з інверсними виходами попередніх

тригерів, то лічильник стане підсумовуючої.

Отримані лічильники називають послідовними, тому що в них кожний тригер перемикається вихідним сигналом попередні. Ці лічильники відрізняються простою схемою, але низькою швидкодією врежимі реєстраціївхідних сигналів, тому що в цьому режимі не можна подавати черговий вхідний сигнал, поки не зафіксований попередній стан лічильника. Часустановленнякоду дорівнюєtуст =ntзт.тр, деtзт.тр- час затримки перемикання тригера. Очевидно, що максимальна частота вхідних сигналів у режимі реєстрації становитьfмакс.рег=1/tуст. Втім, урежимі розподілувхідних імпульсів максимальна частота їхнього надходження буде обмежуватися швидкодією молодшого тригера й складеfмакс.справ=1/tзт.тр.

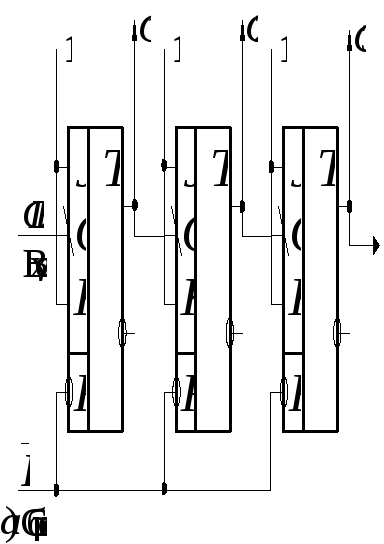

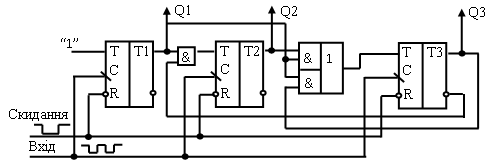

Р исунок

3.4 − Асинхронний підсумовуючий лічильник

наJK- тригерах (а) і часова діаграма

його роботи (б)

исунок

3.4 − Асинхронний підсумовуючий лічильник

наJK- тригерах (а) і часова діаграма

його роботи (б)

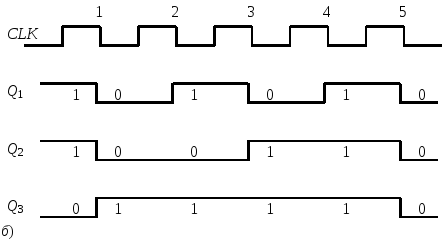

Рисунок 3.5 − Асинхронний лічильник, що віднімає, на D-тригерах (а), часова діаграма його роботи (б).

Другий недолік складається в тім, що через нагромадження часових зрушень у розрядах у процесі встановлення коду, у лічильнику на короткі проміжки часу виникають помилкові стани. Тому, якщо до вихідних розрядів такого лічильника підключити дешифратор, то на його виходах можуть з’явитися помилкові сигнали, що відповідають проміжним фазам переходу лічильника з одного стану в інший. Від названих недоліків вільні синхронні лічильники.

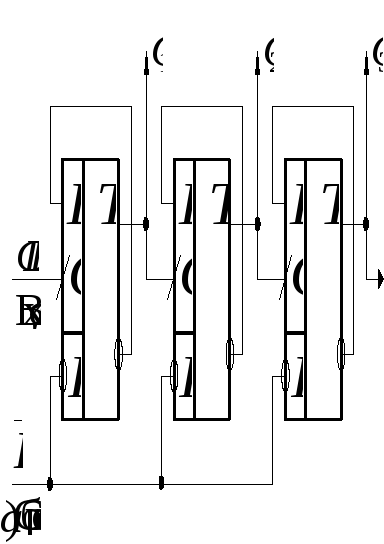

Синхронні

двійкові лічильники. Схему синхронного

лічильника можна представити узагальненою

структурною схемою (рис. 3.6), що включає

тригери з рахунковим входомTі

комбінаційну схему, що формує функції

порушенняfiдля цих

рахункових входів. ВJK-тригерах

рахунковий вхід організується шляхом

з’єднання входівJіK. Вхід![]() управляє режимом роботи схеми (

управляє режимом роботи схеми (![]() − прямий рахунок,

− прямий рахунок,![]() − зворотний рахунок), а вихідний сигнал

переносу/позикиCR/BR(Carry/Borrow) може

використовуватися для нарощування

розрядності лічильника.

− зворотний рахунок), а вихідний сигнал

переносу/позикиCR/BR(Carry/Borrow) може

використовуватися для нарощування

розрядності лічильника.

Рисунок 3.6 −

Структурна схема синхронного лічильника

Рисунок 3.6 −

Структурна схема синхронного лічильника

Як треба з аналізу табл. 3.1 (правило 2), перемикання тригера молодшого розряду здійснюється із приходом рахункового сигналу CLK, а інших тільки в тому випадку, коли всі тригери молодших розрядів установлені в «1» (прямій рахунок) або в «0» (зворотний рахунок).

Отже, у загальному випадку, функція порушення тригера fiдля синхронногодвійковоголічильника може бути визначена виразом:

![]() ,

, ![]() . (3.1)

. (3.1)

Для

молодшого розряду: f1=1. Сигнал переносу/займу

може формуватися у двох випадках, а

саме, коли в лічильнику зберігається

максимальне значення коду

![]() при

при![]() й мінімальне значення

й мінімальне значення![]() при

при![]() :

:

![]() . (3.2)

. (3.2)

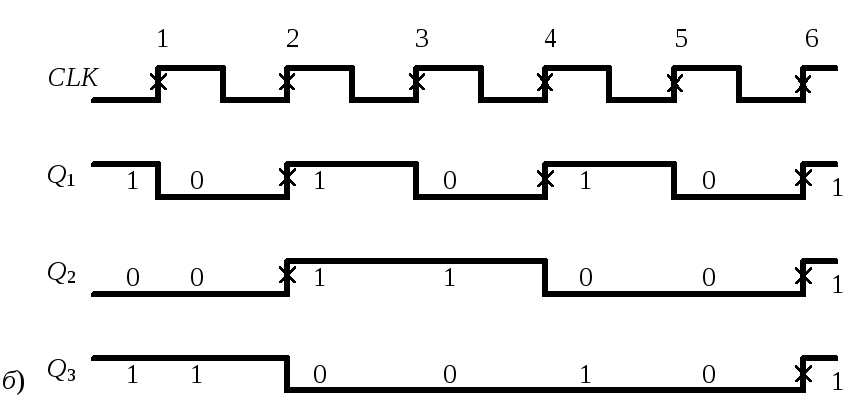

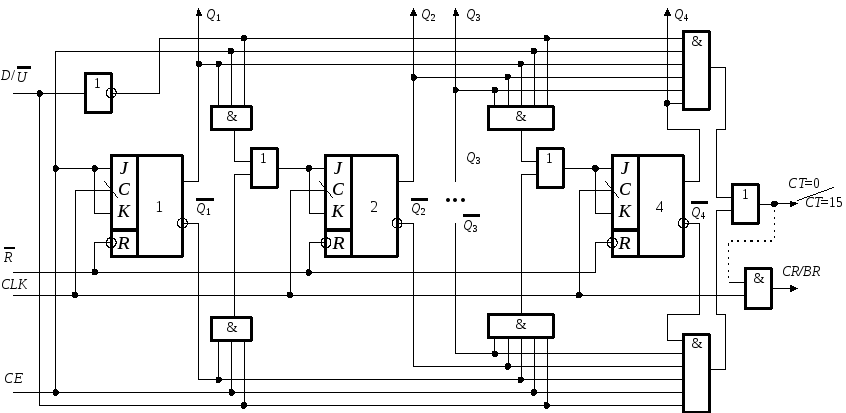

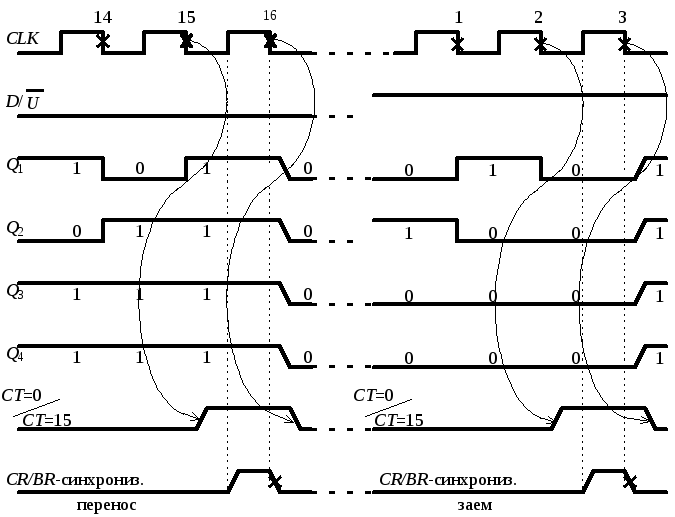

На рис. 3.7 представлена схема 4-розрядного синхронного двійкового лічильника зі змінюваним напрямком рахунку, побудованого відповідно до виразів (3.1) і (3.2) з тією відмінністю, що в схему введений додатковий керуючий вхід CE(Count Enable− дозвіл рахунку). Часові діаграми роботи лічильника (рис. 3.8) пояснюють особливості формування переносу в режимі прямого рахунку й заёма - у зворотному зурахуванням запізнюванняв їхньому формуванні щодо рахункового (тактового) сигналуCLK.

Рисунок 3.7 − Двійковий лічильник зі змінюваним напрямком рахунку

(![]() − прямий,

− прямий,![]() − зворотний)

− зворотний)

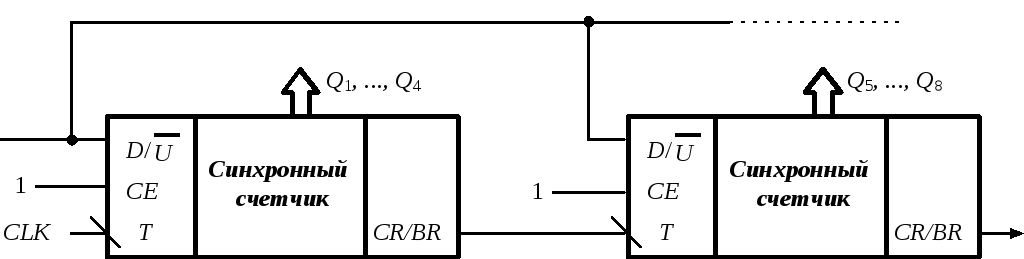

Каскадувати

рахункові групи можна двома способами:

з використанням послідовного або

паралельного переносів. При паралельному

переносі (рис. 3.9) дві рахункові групи

як би поєднуються в єдину синхронну

схему 8-розрядного лічильника. Наявність

керуючого входу дозволу рахунку CEпри такому способі об’єднання є просто

обов’язковим. Іноді, коли висока

швидкість не потрібна, рахункові групи

можна з’єднатипослідовно(рис.

3.10), при цьому сигнал переносу (займу)

служить тактовим сигналом наступної

старшої групи. У цьому випадку (див.

діаграми рис. 3.8) замість виходу![]() доцільно використати той же сигнал,

тільки синхронізований тактовим сигналом

(CR/BR). Схему ж лічильника при цьому

можна спростити, забравши вхід дозволу

рахункуCE.

доцільно використати той же сигнал,

тільки синхронізований тактовим сигналом

(CR/BR). Схему ж лічильника при цьому

можна спростити, забравши вхід дозволу

рахункуCE.

Рисунок 3.8 − Діаграма формування переносу й позики в 4-розрядному синхронному лічильнику (CE=1)

Рисунок 3.9 − Каскадування синхронних лічильників з паралельним переносом

Рисунок 3.10 − Каскадування синхронних лічильників за допомогою послідовного переносу

Синтез лічильників із довільним модулем. Різні області застосування вимагають використання лічильників з різними модулями (наприклад, як дільники частоти імпульсної послідовності використаються лічильники зM<2n, для роботи в 10-вій системі числення застосовуються декадні лічильники зM=10 і т.д.).

Ті

методи побудови лічильників з довільним

модулем рахунку, що вже існують дуже

різноманітні й зводяться по суті до

різних підходів в усуненні надлишкових

станів

![]() ,

де 2n− модуль рахункуn-

розрядного двійкового лічильника [2, 3,

4, 8]. У лабораторній роботі використаються

лише два способи:

,

де 2n− модуль рахункуn-

розрядного двійкового лічильника [2, 3,

4, 8]. У лабораторній роботі використаються

лише два способи:

- класичний метод синтезу лічильника з довільним модулем M, що розглядає поводження лічильника як синхронного автомата із заданою таблицею переходів;

- метод виключення групи надлишкових станів.

Класичний метод. Коротко перелічимо основні етапи синтезу.

1. На

основі заданого значення модуля M

визначаємо число тригерів n, округливши

до найближчого більшого цілого величину![]() .

.

2. Вибираємо (якщо він не є заданим) тип тригера, у якому є або легко реалізується рахунковий режим.

3. Вибираємо природний порядок рахунку, починаючи з 0 (у діапазоні 0...M-1), або з α (у діапазоні від α до 2n-1) і складаємо таблицю переходів лічильника за формою табл. 3.2 (обрані JK-тригер і M=5).

Таблиця 3.2 – Таблиця переходів лічильника

Таблиця 3.2

|

Стани лічильника |

Функції збудження тригерів | ||||||||||

|

Вихідний (t) |

Наступний (t+1) |

|

|

|

|

|

| ||||

|

Q3 |

Q2 |

Q1 |

Q3 |

Q2 |

Q1 |

J3 |

K3 |

J2 |

K2 |

J1 |

K1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

* |

0 |

* |

1 |

* |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

* |

1 |

* |

* |

1 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

* |

* |

0 |

1 |

* |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

* |

* |

1 |

* |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

* |

1 |

0 |

* |

0 |

* |

4.

Складаємо карти Карно для кожної з

функцій порушення

![]() від аргументів

від аргументів![]() і знаходимо відповідні мінімальні

форми:

і знаходимо відповідні мінімальні

форми:

J3=Q2Q1, J2=Q1,J1=![]() ,

,![]()

![]()

K3=1,K2=Q1,K1=1.![]()

5. На основі відомих виразів для функцій збудження будуємо схему синхронного лічильника із заданим модулем.

Метод

виключення.Використання методу

припускає знання виразу для функції

збудження рахункового входуi-го

розряду лічильника(1).Виклад методу проведемо на конкретному

прикладі синтезу підсумовуючого

лічильника, для якого вираз (3.1) при![]() прийме вид

прийме вид

![]() ,

,

![]() . (3.3)

. (3.3)

Для молодшого i=1 розрядуf1=1. Значення модуля рахункуM=6. Як тригер,Т-тригер.

1. На

основі заданого значення модуля Mвизначаємо число тригерівn, округливши

до найближчого більшого цілого величину![]() ,

тобтоn=3.

,

тобтоn=3.

2. Складається таблиця станів лічильника по модулю 2n.

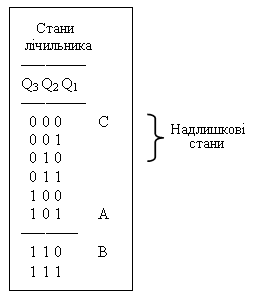

3. Виключається з таблиці група надлишкових станів з виділенням у таблиці наступних кодових комбінацій (наборів): A, B, C. При цьому: А − стан попередній групі надлишкових станів, В − перший в групі надлишкових станів, а С - наступний за групою надлишкових станів (рис. 3.11).

Рисунок 3.11 – Стани лічильника

4. Виконується функція корекції порозрядних функцій порушення fi(i=1, 2, 3) за наступними правилами:

а) Якщо i-ті розряди для станів В і С збігаються, то корекція не потрібна: Qi(B) =Qi(C), тодіfi*= fi..

Тут fi* −відкоректоване значення порозрядної функції збудження. У даному прикладі

f1*= f1=1. (3.4)

Якщо i-ті розряди для станів В і С не збігаються, то корекція виконується за правилами.

б) Qi(А) ≠Qi(C) − має місце перемикання стану тригера для знову встановлених суміжних станів. Тодіfi*= fi VφА, де функціяφА= 0 для всіх наборів, за винятком набору А, для якогоφА = 1. Отже, іfi*=1, що забезпечить перемикання тригераi-го розряду при переході з набору станів А до В.

в) Qi(А)

=Qi(C) – відсутнє перемикання

стану тригера для знову встановлених

суміжних станів. Тодіfi*=

![]() ,

у цьому випадку значення порозрядної

функції порушенняfi*=0

буде блокувати перемикання тригераi-го розряду при переході з набору

станів А до В.

,

у цьому випадку значення порозрядної

функції порушенняfi*=0

буде блокувати перемикання тригераi-го розряду при переході з набору

станів А до В.

![]() Оскільки

надлишкові стани виключені зі станів

лічильника, то вираз для функціїφАможна мінімізувати з врахуванням цих

надлишкових станів. У цьому випадку, як

це неважко одержати, будемо матиφА

=Q3Q1. У розглянутому

прикладі синтезу лічильника має місце

корекція як за правилом (3.4,б):

Оскільки

надлишкові стани виключені зі станів

лічильника, то вираз для функціїφАможна мінімізувати з врахуванням цих

надлишкових станів. У цьому випадку, як

це неважко одержати, будемо матиφА

=Q3Q1. У розглянутому

прикладі синтезу лічильника має місце

корекція як за правилом (3.4,б):

f3*=f3V φА=Q1Q2 V Q3Q1, (3.5)

так і за правилом (3.4, с):

f2*=![]() =Q1*

=Q1*![]() =

=![]() . (3.6)

. (3.6)

У виразах (3.5) і (3.6) f2=Q1 і f3= Q1Q2 представляють порозрядні функції збудження для 2-го й 3-го розрядів відповідно. На рис 3.12 зображена схема лічильника, побудована у відповідності до виразу (3.4) − (3.6). Індивідуальні завдання для синтезу синхронних лічильників з довільним модулем зведені в табл. 3.3.

Рисунок 3.12 – Лічильник з модулем М=6