- •Архитектура эвм

- •Введение

- •Структура мпс

- •Основные понятия в архитектуре мпс

- •Архитектура фон Неймана

- •Гарвардская архитектура

- •Параллельная архитектура

- •Конвейерная архитектура

- •Суперскалярная архитектура

- •АрхитектурыCisc

- •Архитектуры risc

- •Архитектуры misc

- •Ассемблеры

- •Программа Ассемблер

- •Язык Ассемблер

- •Основы 32-битного программирования в Windows

- •Api функции

- •Сообщения Windows

- •Версии ассемблеров

- •Среды разработки

- •Представление данных в эвм

- •Системы счисления и преобразования между ними

- •Форматы представления чисел

- •Форматы представления двоичных чисел

- •Формат с плавающей точкой

- •Типы адресаций операндов

- •Интерфейсы

- •Последовательный интерфейс rs-232c

- •Интерфейс параллельного порта

- •Инфракрасный интерфейс

- •Интерфейс Bluetooth

- •Интерфейс usb

- •Интерфейс ieee 1394 - FireWire

- •Сопроцессоры

- •Система прерываний и исключений

- •Интерфейс jtag

- •Символы и строки

- •Архитектура cisc от Intel

- •Введение

- •Микроархитектура Intel

- •Микроархитектура р6

- •Микроархитектура NetBurst

- •Микроархитектура Pentium 4

- •Микроархитектура Intel Pentium Mobile

- •Микроархитектура Intel Core

- •Микроархитектура Intel Core Duo

- •Микроархитектура Intel Nehalem

- •Адресация памяти в ia_32

- •Наборырегистров

- •Целочисленныйпроцессор

- •Регистры общего назначения (рон)

- •Регистры флагов eflags

- •Регистр указателя команд

- •Сегментные регистры

- •Управляющие регистры

- •Системные адресные регистры

- •Прямой и обратный порядок следования байтов

- •Виды адресации операндов в памяти

- •Цикл выполнения команды

- •Распределение адресного простраства

- •Образ программы в памяти.

- •Математический сопроцессор

- •Xmm технология

- •Система команд

- •Формат команды

- •Классификация команд

- •Целочисленный процессор

- •Команды общего назначения

- •Команды ввода-вывода

- •Инструкции работы со стеком

- •Арифметико-логические инструкции

- •Цепочечные операции

- •Команды управления

- •Команды поддержки языков высокого уровня

- •Команды прерываний

- •Команды синхронизации процессора

- •Команды обработки цепочки бит

- •Команды управления защитой

- •Команды обмена с управляющими регистрами

- •Команды идентификации и управления архитектурой

- •Управление кэшированием

- •Команды управления кэшированием

- •Сопроцессор с плавающей точкой

- •Классификация команд

- •Команды управления сопроцессором

- •Команды передачи данных

- •Команды сравнения данных

- •Арифметические команды

- •Трансцендентные функции

- •Целочисленное mmx расширение

- •Синтаксис ммх-команд

- •Классификация команд

- •Инициализация

- •Передача данных

- •Упаковка данных

- •Распаковка данных

- •Арифметика

- •Сравнения

- •Дополнительные команды

- •XmMрасширение с плавающей точкой

- •Типы данных

- •Передача данных

- •Арифметика

- •Сравнения

- •Преобразования

- •Управление состоянием

- •Распаковка данных

- •Управление кэшированием

- •Дополнительные команды

- •Цикл трансляции, компоновки и выполнения

- •Ассемблер cisc

- •Введение

- •Средства программирования и отладки

- •Описание masm

- •Структура программы на ассемблере

- •Типы данных

- •Макросредства

- •Директивы

- •Архитектура risc

- •Система команд

- •Архитектура misc

- •Архитектура vliw

- •Архитектура вычислительных систем со сверхдлинными командами

- •Архитектура ia-64

- •Многоядерные архитектуры

- •Микроконтроллер avr от Atmel

- •Архитектура avr от Atmel

- •Ассемблер

- •Команды ассемблера

- •Директивы ассемблера

- •Выражения

- •Микроконтроллеры c28x

- •Архитектура c28x

- •Архитектура f28x

- •Инструментальные средства разработки по

- •Ассемблер

- •Команды ассемблера

- •Формат объектного файла

- •Директивы ассемблера

- •Макроязык и макрокоманды

- •Компоновщик

- •Архиватор

- •Абсолютный листер

- •Листер перекрестных ссылок

- •Утилита 16-ричного преобразования

- •Архитектура VelociTi

- •Структура и состав цсп с6x

- •Средства разработки цсп с6x

- •Ассемблер цсп с6x

- •Команды ассемблера

- •Выражения

- •Листинги

- •Листинги программ

- •Директивы ассемблера

- •Макроязык и макрокоманды

- •Компоновщик

- •Утилиты

- •Поддержка в matlab

- •Введение

- •Встроенные платы для цсп ‘c6x

Суперскалярная архитектура

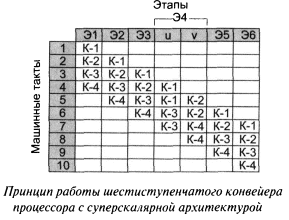

Процессор, построенный по суперскалярной архитектуре, имеет 2 (или больше) конвейера для выполнения команд. Это позволяет одновременно выполнять 2 (или больше) команды. Чтобы лучше понять целесообразность применения суперскалярной архитектуры в процессоре, давайте рассмотрим предыдущий пример конвейерной обработки, в котором мы для упрощения предполагали, что этап выполнения команды (Э4) длится всего 1 машинный такт. А что же произойдет, если этап выполнения команды Э4 длится 2 машинных такта? Тогда в работе конвейера возникнут сбои, как показано на рисунке.

Процессор не сможет перейти к фазе выполнения Э4 команды K2, пока он полностью не завершит фазу выполнения команды K1. В результате цикл выполнения команды К-2 увеличится на 1 машинный такт, т.е. на время ожидания освобождения конвейера на этапе Э4. По мере поступления на конвейер дополнительных команд, некоторые его ступени будут работать вхолостую (на рисунке они выделены серым цветом).

Для борьбы с простоями оборудования используются нескольео конвеййеров. В процессоре Intel Pentium было применено 2 конвейера. Он стал первым процессором семейства IA-32, построенным по суперскалярной архитектуре. В процессоре Pentium Рго впервые было применено 3 конвейера.

Продолжим рассмотрение нашего примера шестиступенчатого конвейера и введем в него еше один (т.е. второй) конвейер. Как и раньше мы будем предполагать, что фаза выполнения команды Э4 длится 2 машинных такта. Как показано на рисунке, команда с нечетным номером поступает на u-конвейер, а команда с четным номером — на v-конвейер. Подобный подход позволяет ликвидировать простои в работе конвейера.

В МП с такой архитектурой применяется распараллеливание исполнения команд между несколькими конвейерами, причём решение о параллельном исполнении команд принимается аппаратурой процессора на этапе исполнения. Эффективное использование такой архитектуры требует специальной оптимизации машинного кода в компиляторе для генерации пар независимых команд (когда результат одной команды не является аргументом другой).

Суперскалярные МП могут выдавать на выполнение в каждом такте переменное число команд, и работа их конвейеров может планироваться как статически с помощью компилятора, так и с помощью аппаратных средств динамической оптимизации. Суперскалярные машины используют параллелизм на уровне команд путем посылки нескольких команд из обычного потока команд в несколько функциональных устройств.

В типичной суперскалярной машине аппаратура может осуществлять выдачу от 1 до 8 команд в одном такте. Обычно эти команды должны быть независимыми и удовлетворять некоторым ограничениям, например таким, что в каждом такте не может выдаваться более одной команды обращения к памяти. Если какая-либо команда в потоке команд является логически зависимой или не удовлетворяет критериям выдачи, на выполнение будут выданы только команды, предшествующие данной. Поэтому скорость выдачи команд в суперскалярных машинах является переменной

АрхитектурыCisc

Архитектуры risc

MCS-51

MCS-51 (Intel 8051) — классическая архитектура микроконтроллера. Для неё существует кросс-ассемблер ASM51, выпущенный корпорацией MetaLink.

Кроме того, многие фирмы — разработчики программного обеспечения, такие как IAR или Keil, представили свои варианты ассемблеров. В ряде случаев применение этих ассемблеров оказывается более эффективным благодаря удобному набору директив и наличию среды программирования, объединяющей в себе профессиональный ассемблер и язык программирования Си, отладчик и менеджер программных проектов.

AVR

На данный момент существуют 2 компилятора производства Atmel (AVRStudio 3 и AVRStudio4). Вторая версия — попытка исправить не очень удачную первую.

В рамках проекта AVR-GCC (он же WinAVR) существует компилятор avr-as(это портированный под AVR ассемблер GNU as изGCC).

Также существует свободный минималистический компилятор avra[1].

ARM