- •Архитектура эвм

- •Введение

- •Структура мпс

- •Основные понятия в архитектуре мпс

- •Архитектура фон Неймана

- •Гарвардская архитектура

- •Параллельная архитектура

- •Конвейерная архитектура

- •Суперскалярная архитектура

- •АрхитектурыCisc

- •Архитектуры risc

- •Архитектуры misc

- •Ассемблеры

- •Программа Ассемблер

- •Язык Ассемблер

- •Основы 32-битного программирования в Windows

- •Api функции

- •Сообщения Windows

- •Версии ассемблеров

- •Среды разработки

- •Представление данных в эвм

- •Системы счисления и преобразования между ними

- •Форматы представления чисел

- •Форматы представления двоичных чисел

- •Формат с плавающей точкой

- •Типы адресаций операндов

- •Интерфейсы

- •Последовательный интерфейс rs-232c

- •Интерфейс параллельного порта

- •Инфракрасный интерфейс

- •Интерфейс Bluetooth

- •Интерфейс usb

- •Интерфейс ieee 1394 - FireWire

- •Сопроцессоры

- •Система прерываний и исключений

- •Интерфейс jtag

- •Символы и строки

- •Архитектура cisc от Intel

- •Введение

- •Микроархитектура Intel

- •Микроархитектура р6

- •Микроархитектура NetBurst

- •Микроархитектура Pentium 4

- •Микроархитектура Intel Pentium Mobile

- •Микроархитектура Intel Core

- •Микроархитектура Intel Core Duo

- •Микроархитектура Intel Nehalem

- •Адресация памяти в ia_32

- •Наборырегистров

- •Целочисленныйпроцессор

- •Регистры общего назначения (рон)

- •Регистры флагов eflags

- •Регистр указателя команд

- •Сегментные регистры

- •Управляющие регистры

- •Системные адресные регистры

- •Прямой и обратный порядок следования байтов

- •Виды адресации операндов в памяти

- •Цикл выполнения команды

- •Распределение адресного простраства

- •Образ программы в памяти.

- •Математический сопроцессор

- •Xmm технология

- •Система команд

- •Формат команды

- •Классификация команд

- •Целочисленный процессор

- •Команды общего назначения

- •Команды ввода-вывода

- •Инструкции работы со стеком

- •Арифметико-логические инструкции

- •Цепочечные операции

- •Команды управления

- •Команды поддержки языков высокого уровня

- •Команды прерываний

- •Команды синхронизации процессора

- •Команды обработки цепочки бит

- •Команды управления защитой

- •Команды обмена с управляющими регистрами

- •Команды идентификации и управления архитектурой

- •Управление кэшированием

- •Команды управления кэшированием

- •Сопроцессор с плавающей точкой

- •Классификация команд

- •Команды управления сопроцессором

- •Команды передачи данных

- •Команды сравнения данных

- •Арифметические команды

- •Трансцендентные функции

- •Целочисленное mmx расширение

- •Синтаксис ммх-команд

- •Классификация команд

- •Инициализация

- •Передача данных

- •Упаковка данных

- •Распаковка данных

- •Арифметика

- •Сравнения

- •Дополнительные команды

- •XmMрасширение с плавающей точкой

- •Типы данных

- •Передача данных

- •Арифметика

- •Сравнения

- •Преобразования

- •Управление состоянием

- •Распаковка данных

- •Управление кэшированием

- •Дополнительные команды

- •Цикл трансляции, компоновки и выполнения

- •Ассемблер cisc

- •Введение

- •Средства программирования и отладки

- •Описание masm

- •Структура программы на ассемблере

- •Типы данных

- •Макросредства

- •Директивы

- •Архитектура risc

- •Система команд

- •Архитектура misc

- •Архитектура vliw

- •Архитектура вычислительных систем со сверхдлинными командами

- •Архитектура ia-64

- •Многоядерные архитектуры

- •Микроконтроллер avr от Atmel

- •Архитектура avr от Atmel

- •Ассемблер

- •Команды ассемблера

- •Директивы ассемблера

- •Выражения

- •Микроконтроллеры c28x

- •Архитектура c28x

- •Архитектура f28x

- •Инструментальные средства разработки по

- •Ассемблер

- •Команды ассемблера

- •Формат объектного файла

- •Директивы ассемблера

- •Макроязык и макрокоманды

- •Компоновщик

- •Архиватор

- •Абсолютный листер

- •Листер перекрестных ссылок

- •Утилита 16-ричного преобразования

- •Архитектура VelociTi

- •Структура и состав цсп с6x

- •Средства разработки цсп с6x

- •Ассемблер цсп с6x

- •Команды ассемблера

- •Выражения

- •Листинги

- •Листинги программ

- •Директивы ассемблера

- •Макроязык и макрокоманды

- •Компоновщик

- •Утилиты

- •Поддержка в matlab

- •Введение

- •Встроенные платы для цсп ‘c6x

Система прерываний и исключений

Прерывания и исключения - это события, которые указывают на возникновение в системе или в выполняемой в данный момент задаче определенных условий, требующих вмешательства процессора. Возникновение таких событий вынуждает процессор прервать выполнение текущей задачи и передать управление специальной процедуре либо задаче, называемой обработчиком прерывания или обработчиком исключения. Различные синхронные и асинхронные события в системе можно классифицировать следующим образом:

Прерыванияобычно возникают в произвольный момент времени. Прерывания бывают аппаратные (или внешние) и программные.

Внешние прерывания генерируются по аппаратному сигналу, поступающему от периферийного оборудования, когда оно требует обслуживания. Процессор определяет необходимость обработки внешнего прерывания по наличию сигнала на линии прерывания При появлении сигнала на линии INTR# внешний контроллер прерываний должен предоставить процессору вектор (номер) прерывания.

Прерывания всегда обрабатываются на границе инструкций, т.е. при появлении сигнала прерывания процессор сначала завершит выполняемую в данный момент инструкцию (или итерацию при наличии префикса повторения), а только потом начнет обрабатывать прерывание. Помещаемый в стек обработчика адрес очередной инструкции позволяет корректно возобновить выполнение прерванной программы.

Исключенияявляются для процессора внутренними событиями и сигнализируют о каких-либо ошибочных условиях при выполнении той или иной инструкции. Источниками исключений являются три типа событий:

генерируемые программой исключения, позволяющие программе контролировать определенные условия в заданных точках программы (проверка на переполнение, контрольная точка, проверка границ массива);

исключения машинного контроля, возникающие в процессе контроля операций внутри чипа и транзакций на шине процессора;

обнаруженные процессором ошибки в программе (деление на ноль, отсутствие страницы и т.п.)

Все прерывания и исключения имеют номер (иногда именуемый вектором) в диапазоне от 0 до 255.

Интерфейс jtag

Термином JTAGобозначают совокупность средств и операций, позволяющих проводить тестирование БИС/СБИС без физического доступа к каждому ее выводу. АббревиатураJTAGвозникла по наименованию разработчика - объединенной группы по тестамJointTestActionGroup. Термином "периферийное сканирование" (ПС) или по-английскиBoundaryScanTesting(BST) называют тестирование поJTAGстандарту (IEEEStd1149.1).

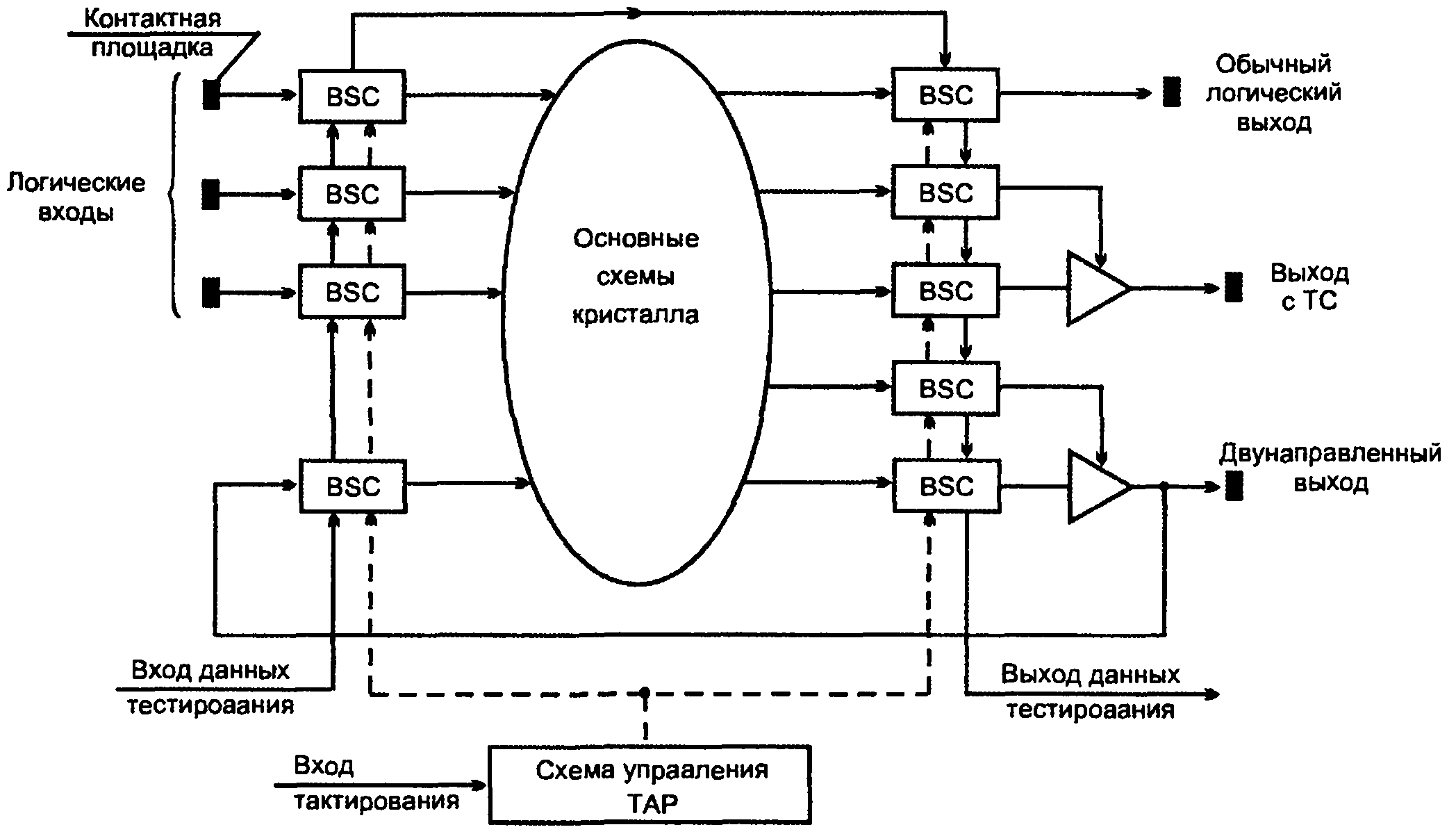

Такое тестирование возможно только для микросхем, внутри которых имеется набор специальных элементов - ячеек периферийного сканирования (ячеек ПС), в английской терминологии BSC (Boundary Scan Cells) и схем управления их работой.

Ячейки BSC размещены между каждым внешним выводом микросхемы и схемами кристалла, образующими само проверяемое устройство. Все большее число современных микросхем снабжается интерфейсом JTAG, т. е. возможностями периферийного сканирования.

Основная концепция периферийного сканирования иллюстрируется рисунком.

Ячейки сканирования BSC могут работать в разных режимах. В рабочем режиме они просто пропускают сигналы через себя слева направо и не изменяют функционирования устройства. При этом для выходов обычного логического типа нужна одна BSC, для выходов с третьим состоянием - две (вторая для выработки сигнала управления буфером), для двунаправленных выводов - три. Входные сигналы проходят через ячейки BSC прямо к соответствующим точкам основных схем кристалла.

В режиме тестирования пропуск сигналов через ячейки прекращается, а сами они, соединяясь последовательно, образуют сдвигающий регистр, обладающий также некоторыми дополнительными функциями. В такой сдвигающий регистр со входа данных тестирования может быть введен тестовый код для подачи на входные точки основной схемы кристалла. Результат, который выработает основная схема, загружается в ячейки BSC на ее выходах и затем выводится последовательно для сравнения с ожидаемым правильным результатом вне устройства.

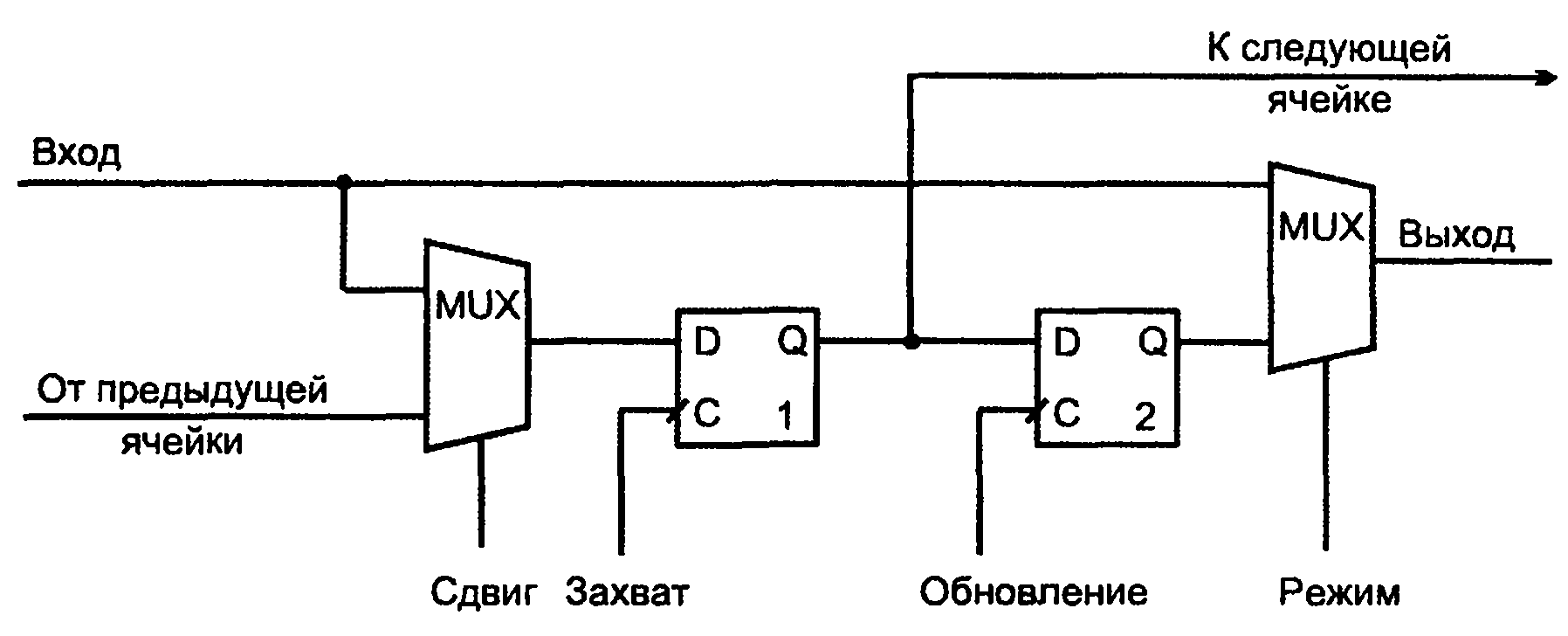

Схема BSC содержит два мультиплексора MUXи два D-триггера.

В зависимости от адресного входа "Режим" выходного мультиплексора, ячейка либо свободно пропускает сигнал со входа на выход, либо передает на выход состояние второго триггера. Адресный сигнал входного мультиплексора "Сдвиг" управляет подачей на первый триггер входного сигнала (от логических входов микросхемы) или же сигнала от предыдущей ячейки. Таким образом, по синхросигналу для первых триггеров и при передаче через входной мультиплексор сигнала "Вход" осуществляется параллельная загрузка этих триггеров во всех ячейках. При передаче через входной мультиплексор сигнала от предыдущей ячейки тактовый сигнал производит сдвиг на один разряд в регистре, образованном последовательным соединением ячеек.

По синхросигналу "Обновление" текущее содержимое регистра, составленного из цепочки первых триггеров, переписывается в статический регистр, составленный из вторых триггеров. Сдвиги в регистре на триггерах 1 не будут влиять на содержимое регистра на триггерах 2.

Периферийное сканирование позволяет проверять работу самих микросхем, монтажные межсоединения микросхем между собой на печатной плате, считывать сигналы на выводах микросхемы во время ее работы или управлять этими сигналами.