Цифровые устройства и микропроцессоры

.pdf

60

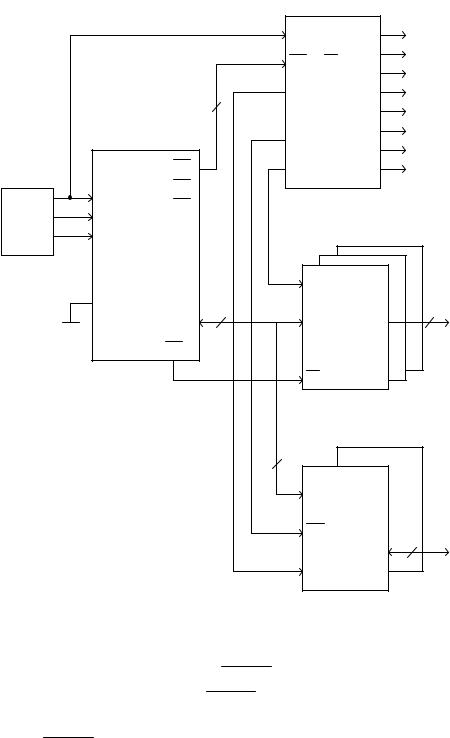

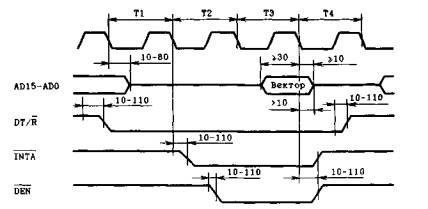

Рис. 13. Максимальный режим

Активный сигнал на выводе LOCK = 0 вырабатывается с помощью

специальной команды (префикса) LOCK и позволяет запретить захват шин микропроцессора внешними устройствами на время выполнения следующей

за префиксом LOCK команды. Выводы QS0, QS1 несут информацию о со-

стоянии очереди команд микропроцессора, комбинации сигналов на этих выводах приведены с таблице 7.

Сигналы QS0, QS1 действуют в течение такта синхронизации после выполнения операции над очередью, они предназначены для сопроцессора, который воспринимает команды и операции с помощью команды ECS . Подробнее эта ситуация будет рассмотрена в разделе 4.2. «Сопроцессорные конфигурации».

61

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 11. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Назначение выводов в мак- |

||||

Минимальный режим |

Максимальный режим |

|||||||||||||||||||||||||||||

(MN / |

|

|

|

|

|

|

=1) |

(MN / |

|

|

|

|

|

|

=0) |

симальном режиме |

||||||||||||||

MX |

MX |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блокировка |

|||

|

|

|

WR |

|

|

|

|

|

|

|

LOCK |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

QS0 |

Состояние очереди команд |

|||||||||||||||

|

INTA |

|

|

|||||||||||||||||||||||||||

|

STB |

|

|

QS1 |

|

|||||||||||||||||||||||||

M / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Состояние МП |

|||||||

IO |

|

|

|

|

|

ST 2 |

||||||||||||||||||||||||

OP / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

IP |

|

|

|

ST1 |

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

DE |

|

|

|

|

ST 0 |

Запрос/предоставление |

||||||||||||||||||||||

|

HLD |

|

|

|

|

|

/ |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

RO |

GT 0 |

|||||||||||||||||||||||||||

HLDA |

|

|

|

|

|

|

/ |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RO |

GT1 |

|

|

|||||||||||||

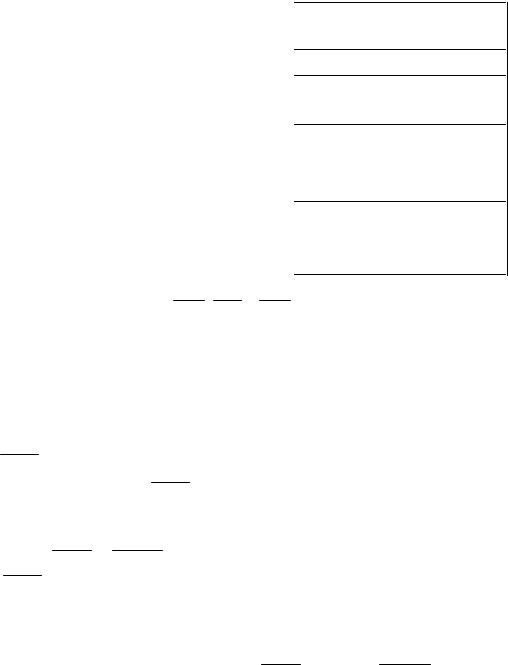

Для декодирования сигналов ST 0, ST1, ST 2 и в систему включается контроллер системной шины К1810ВГ88 (18288), позволяющий сделать полную развязку ША, ШД и управляющей шины. С его помощью реализуется раздельная адресация ВУ и памяти.

Схема системного контроллера приведена на рис. 14. В схему входят дешифратор состояний, формирователи управляющих и командных сигналов и схема управления. Работа схемы тактируется импульсами с тактового гене-

ратора. Входы AEN,CEN и IOB необходимы для организации работы в мно-

гопроцессорной системе. Сигнал AEN служит для разрешения выдачи семи управляющих сигналов, поступающих с формирователей командных сигналов. Сигнал CEN разрешает как выдачу командных сигналов, так и выдачу

сигналов управления DEN и PDEN .

Сигналы AEN и CEN подаются с арбитра шин К1810ВБ89. Вход IOB используется для задания режима работы системного контроллера на него подается постоянный потенциал логической «1» или «0». При IOB =1 системный контроллер функционирует в режиме шины ввода – вывода, а при

IOB =0 – в режиме системной шины. Сигналы DEN (DE) и PDEN используются, как и в минимальном режиме, для разрешения или запрещения работы приемопередатчиков шин данных в зависимости от потенциалов на входе

IOB .

CLK

QS1,QS0

BHE/ST7 A19...A16

ST6...ST3

ST2...ST0

Чтение

AD15...AD0 (AD7...AD0

для К1810ВМ88)

RD

MRDC

IORC

62

T1 |

|

T2 |

|

T3 |

|

T4 |

|

|

|

|

|

|

|

10 -110мс

10...130мс

Адрес Данные (ввод)

10...165мс

10...35мс

Запись

AD15...AD0 Адрес Данные (ввод) (AD7...AD0)

LOCK (1 цикл)

Рис. 14. Временные диаграммы работы МП К1810ВМ86 в максимальном режиме

63

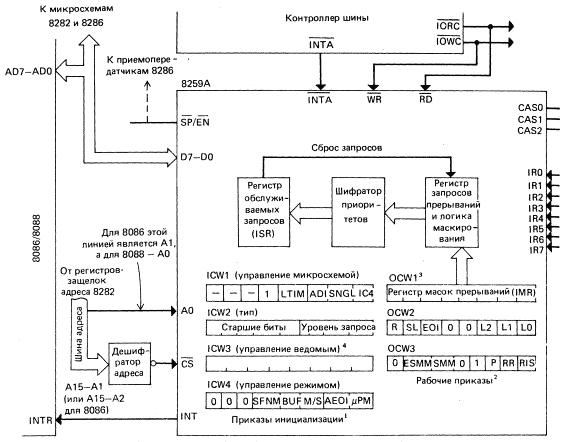

Рис. 15. Структура системного контроллера К1810ВГ88

Командные сигналы вырабатываются системным контроллером (рис. 15) в режиме системной шины (при IOB = 0) в соответствии с кодом состоя-

ния ST 0, ST 0, ST 2 при наличии разрешающего сигнала AEN . Сигнал MCE используется только при каскадировании контроллеров прерываний и служит для считывания адреса ведомого контроллера приоритетных преры-

ваний. Сигналы IOWC и IORC служат для ВУ командами записи и чтения информации с шины данных, сигналы MRDC и MWTC – командами чтения

и записи соответственно. Сигналы AIOWC и AMWC – сигналы опережающей записи для ВУ и памяти и служат для их подготовки к записи информации.

Выходной сигналы INTA определяет начало обработки запроса прерывания от ВУ.

Назначение сигнала ALE(STB) такое же, как и в минимальном режиме: защелкивание адреса в буферном регистре.

Лекция № 11

5.2.Генерация и обработка прерываний

5.2.1.Внешние, внутренние и программные прерывания

Ранее говорилось, что прерывания – это вызываемый определённым образом процесс, переключающий МП на выполнение другой программы с по-

64

следующим возвратом к прерванной программе. Прерываний в МПС на базе I8086/88 256 типов (0…255). Они делятся на внешние аппаратные, внутренние аппаратные и программные. Любые прерывания требуют новых адресов подпрограмм прерываний, которые выбираются из таблицы векторов. Каждый вектор представляет собой два 16-разрядных слова, расположенных в соседних ячейках памяти, причём в ячейке с меньшим адресом (чётным) содержится смещение в кодовом сегменте (новое значение IP), а в ячейке с большим адресом новое значение базового адреса кодового сегмента (значение CS). Под векторы (указатели) прерываний в общем пространстве адресов памяти зарезервирована область 0-3FFh.

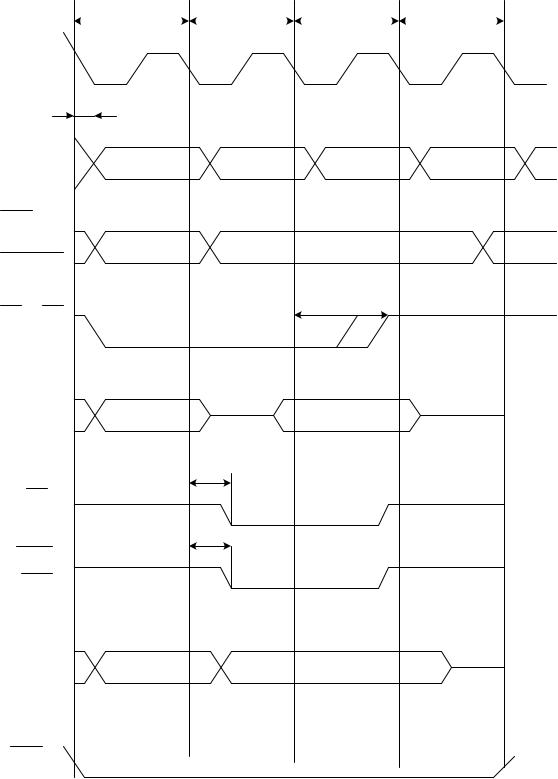

Внешние аппаратные прерывания вызываются внешними по отношению к МП событиями, возникающими асинхронно по отношению к исполняемой программе. Процессор может воспринимать прерывания после выполнения каждой команды, длинные строковые команды имеют для этого специальные окна. Аппаратные прерывания подразделяются на маскируемые и немаскируемые. Для этого у процессора есть два входа: INTR (Interrupt Requist) и NMI (Non Mascable Interrupt). Маскируемые прерывания вызываются переходом в единицу сигнала на входе INTR и выполняются при установленном флаге разрешения прерываний (IF=1). Управление флагом IF производят команды CLI – сброс флага IF =0 и STI – установка флага IF=1(однобайтные команды, выполняемые за два такта). В случае перехода к подпрограмме процессор сохраняет в стеке адрес возврата в основную программу (содержимое CS и IP), регистр флагов, сбрасывает флаг IF и вырабатывает два следующих друг за другом цикла подтверждения прерываний, в которых генерируются два соответствующих сигнала INTA (Interrupt Acknolidge). Высокой уровень сигнала на входе INTR должен сохраняться по крайней мере до появления сигнала INTA. Первый цикл подтверждения прерываний и сигнал INTA холостой, предупреждающий ВУ о принятии запроса и необходимости подготовки номера вектора. По второму сигналу INTA, служащему сигналом чтения в этом цикле, происходит считывание по шине данных байта, содержащего номер вектора, соответствующего данному типу аппаратного прерывания. Полученный номер вектора умножается в процессоре на 4, это значение помещается в регистр IP. Тем самым определяется точка входа в таблицу векторов, откуда считывается адресжет ый я ммы, соответствующий полученному запросу. Обработка текущего прерывания может быть, в свою очередь, прервана немаскируемым прерыванием, а если в подпрограмме разработчик программы установит флаг IF, то и другим маскируемым аппаратным прерыванием (вложенные прерывания). После аппаратного сброса по сигналу CLR (RESET) флаг IF сброшен, и маскируемые прерывания не возможны.

По окончании выполнения подпрограммы по команде IRET МП извлекает из стека адрес возврата и сохранённое значение регистра флагов. При использовании команды RET (FAR) регистр флагов из стека не восстанавливается.

65

Рис. Диаграмма машинного цикла «Прерывание»

Немаскируемые прерывания выполняются независимо от состояния флага IF по сигналу NMI . Высокий уровень на этом входе вызовет прерывание с фиксированным номером 2 (см. табл. 4), которое выполняется так же, как и маскируемое. Этот вход используется для обработки в связи с экстренной ситуацией, например, сбоем по питанию, обнаружением ошибки памяти. Немаскируемое прерывание не требует номера вектора, поэтому в ответ на сигнал на входе NMI нет цикла «подтверждение прерывания», и сигнал на выходе INTAне формируется. Это помогает достигнуть высокой реакции, так как МП сразу же входит в таблицу векторов и считывает адрес соответствующей подпрограммы прерывания.

Внешние прерывания могут появляться в произвольный момент. Время реакции МП, определяющее запаздывание обслуживания прерывания, зависит от времени выполнения текущей команды. Наибольшее время выполнения у команд умножения, деления и команд сдвига на много бит.

Внутренние прерывания могут возникнуть по особым условиям в двух случаях:

прерывание (тип 0) при выполнении команд DIV и IDIV , вызывающее переполнение разрядной сетки;

пошаговые (отладочные) прерывания (тип 1).

Прерывание из-за ошибки деления возникает. Когда при выполнении команд DIV или IDIV формат частного превышает формат получателя или в случае деления на нуль.

Прерывание типа 1 обеспечивает пошаговую работу, им управляет флажок TF (флаг трассировки). Если TF =1, то по окончанию следующей команды возникает прерывание, вызывающее обращение к таблице векторов с адресами 00004…00007. При этом, как и в предыдущем случае. В стек автоматически записываются значения из регистров CS,IP и регистр флагов. При выполнении подпрограммы флаги IF и TF сбрасываются, чтобы при выполнении подпрограммы процессор работал обычным способом, а не в пошаговом режиме, но при выходе из подпрограммы исходное значение регистра флагов, включая и разрешенный флажок TF , восстанавливается. Таким обра-

66

зом, сразу после команды, выполненной за возвратом из подпрограммы, снова появится прерывание. Значит, до тех пор, пока флажок TF установлен, прерывание возникает после каждой команды. Флажок TF можно установить или сбросить посредством включения в стек регистра и извлечения этой информации в процессор с последующим необходимым маскированием. Для включения регистра флаговF в стек и извлечения его из стека предусмотрены команды PUSHE и POPF соответственно.

Таблица 16

Программные прерывания не зависят от состояния флагов F , они бывают трех видов:

пользовательские INT тип (номер вектора); специальное прерывание INTЗ; прерывание по переполнению INTO .

В прерываниях, определяемых пользователем при составлении программы, вторым байтом задается номер вектора прерывания. Считанный

67

жерой байт множится в процессоре на 4, тем самым определяется точка входа в таблицу векторов, где хранится адрес подпрограммы прерывания. При переходе к подпрограмме в стеке запоминается адрес возврата в программу (CS и IP) и регистр флагов. При этом может быть выполнении межсегментный переход.

Однобайтная команда INTЗопределена как прерывание контрольной точки (точки разрыва). Контрольные точки обычно используются как средства отладки. Эту команду также можно использовать, чтобы вставить дополнительный фрагмент программы без ее повторной трансляции.

Прерывания по переполнению (тип 4) выполняются по однобайтной команде INTO , которую обычно ставят в программе после арифметических команд над числами со знаком.

5.2.2 . Программируемый контроллер прерываний I8259 (К1810ВН59)

Для обработки внешних прерываний микропроцессоров I8086/88 предлагается программируемый контроллер прерываний 8259А фирмы Intel.

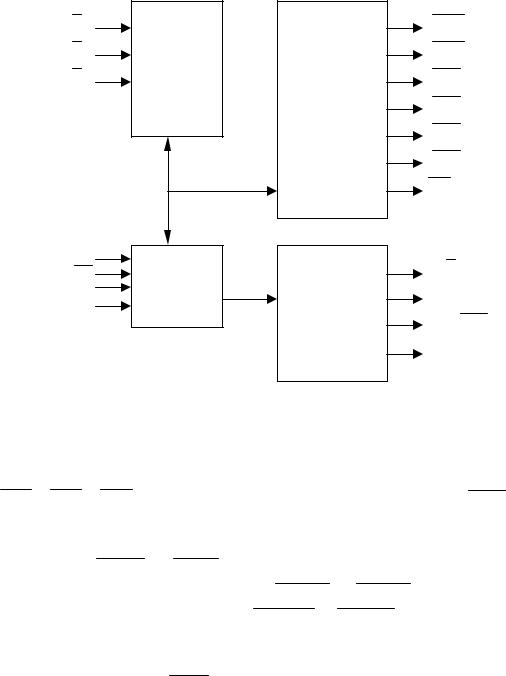

Система прерываний с одним контроллером. Микросхема 8259A вы-

пускается в 28-контактном корпусе типа DIP и требует один источник питания напряжением +5 В. Ее организация и подключения в системе с максимальным режимом показаны на рис. 17. Ниже даются определения контактов микросхемы:

D7-D0. Для взаимодействия с ЦП по шине данных. В больших системах могут потребоваться шинные драйверы, а в малых системах достаточно прямых соединений.

INT. Для выдачи в ЦП сигнала запроса прерывания.

INTA#. Для приема сигналов подтверждения прерывания от ЦП. Предполагается, что подтверждение состоит из двух импульсов, что делает контроллер совместимым с микропроцессорами 8086/8088.

RD#. Сигнализирует контроллеру поместить на шину данных содержимое регистров IMR, ISR или IMR или приоритетный уровень. Что выдается на шину, зависит от состояния контроллера (см. далее).

WR# Сигнализирует контроллеру, что он должен принять данные с шины данных и использовать их для установки бит в словах приказов. Распределение принятых данных рассматривается далее.

CS#. Идентифицирует обращение к контроллеру. Подключается к шине адреса через дешифратор, который сравнивает старшие биты адреса 8259А с адресом, находящимся на шине адреса.

АО. Указывает порт 8259А, к которому производится обращение. Для каждого контроллера в адресном пространстве ввода-вывода системы необходимо зарезервировать два адреса.

IR7-IRO. Для восприятия запросов от интерфейсов ввода-вывода или других (ведомых) контроллеров.

68

Рис.17. Организация программируемого контроллера прерываний

CAS2-CASO. Для идентификации конкретного ведомого контроллера. SP#/EN#. Выполняет две функции. Как вход определяет, каким может быть контроллер: ведущим (SP#/EN# == 1) или ведомым (SP#/EN# == 0). Как выход осуществляет запрещение приемопередатчиков шины данных, когда данные передаются из контроллера в ЦП. Использование в качестве входа или выхода рассматривается далее.

В системе на базе микропроцессора 8088 два адреса 8259А обычно соседние и линия адреса АО подключается на вход АО. Так как контроллер имеет всего восемь линий данных, а микропроцессор 8086 всегда вводит указатель прерывания по младшим 8 битам своей 16-битной шины данных, все передачи данных в (из) 8259А должны производиться по младшей половине шины. Наиболее просто гарантировать удовлетворение этого требования: подключить линию А1 на вход АО и использовать два соседних четных адреса, первый из которых кратен 4. Однако ради упрощения последующего обсуждения в обоих случаях будем считать второй адрес нечетным.

Секция управления 8259А имеет несколько программируемых бит, которые можно считать находящимися в семи 8-битных регистрах. Эти регистры резделены на две группы, первая из которых содержит слова приказов инициализации (ICW), а вторая — слова рабочих приказов (OCW) . Слова приказов инициализации обычно устанавливаются процедурой инициализации при включении вычислительной системы и при работе не изменяются.

69

Слова рабочих приказов применяются для динамического управления обработкой прерываний.

Регистр IRR (и логика маскирования), шифратор приоритетов и регистр ISR предназначены для восприятия и управления прерываниями на входах IR7-IRO. Регистр IRR фиксирует входные запросы и вместе с шифратором приоритетов разрешает незамаскированным запросам с достаточным приоритетом сформировать сигнал 1 на выходе INT. Шифратор приоритетов определяет приоритеты запросов в IRR, а регистр ISR предназначен для хранения текущих обрабатываемых запросов.

После того как бит в IRR установлен в состояние 1, он сравнивается с соответствующим битом маски из IMR. Если бит маски содержит 1, запрос передается в шифратор приоритетов, в противном же случае запрос блокируется. Когда запрос прерывания подается в шифратор приоритетов,жет ый ется его приоритет, и если в соответствии с текущим состоянием шифратора приоритетов необходимо выдать прерывание в процессор, формируется сигнал INT.

Если флажок IF = 1, процессор реализует последовательность прерывания по завершению текущей команды и возвращает два отрицательных импуль ж по линии INTA#. При действии первого импульса триггеры-защелки в IRR запрещаются, поэтому IRR игнорирует последующие сигналы на входах IR7-IRO. Такое состояние сохраняется до окончания второго импульса INTA#. Кроме того, первый импульс INTA# устанавливает соответствующий бит ISR и сбрасывает соответствующий бит в IRR. Второй импульс INTA# передает на линии D7-DO текущее содержимое ICW2 и этот байт процессор использует как тип прерывания. Если бит автоматического окончания прерывания (AEOI) в ICW4 содержит 1, по окончанию второго импульса INTA# сбрасывается бит ISR, который был установлен первым импульсом INTA#; в противном случае бит ISR не сбрасывается до выдачи в OCW2 соответствующего приказа окончания прерывания (EOI).

Как уже говорилось, слова приказов инициализации обычно загружает процедура инициализации при включении системы, и они содержат биты управления, не изменяющиеся при работе системы. Контроллер 8259А имеет четный адрес (АО = 0) и нечетный адрес (АО = 1) и слова приказов инициализации должны загружаться последовательно с использованием четного адреса для ICW1 и нечетного для остальных ICW.

Биты ICW1 определяются следующим образом:

Биты 7-5. Предназначены только для системы на базе микропроцессо-

ров 8080/8085.

Бит 4. Всегда установлен в 1. Он направляет принятый байт в ICW1 в отличие от OCW2 или OCW3, которые также используют четный адрес (АС) = 0).

Бит 3 (LTIM). Определяет режим запуска фронтом (LTIM = 0) или уровнем (LTIM = 1). Режим запуска фронтом вызывает сброс бита IRR, когда устанавливается соответствующий бит ISR.