Цифровые устройства и микропроцессоры

.pdf20

ёмкость памяти может доходить до 1 Мбайт, хотя команды оперируют 16-битными адресами;

сегменты кода, данных и стека могут иметь длину более 64 Кбайт благодаря использованию нескольких сегментов кода, данных или стека.

Источники смещения для различных типов обращения к памяти приведены в таблице 1. Из таблицы видно, что команды всегда выбираются из сегмента кода в соответствии с логическим адресом CS : IP. Стековые команды всегда обращаются к сегменту стека по адресу SS:SP. Если при вычислении адреса ЕА используется регистр ВР, то обращение производится также к стековому сегменту, однако в этом случае стековый принцип работы «вошедший последним выходит первым» игнорируется и ячейки стекового сегмента рассматриваются просто как ячейки памяти. Обычно операнды располагаются в текущем сегменте данных DS и обращение к ним организуется по адресу DS:EA. Однако, можно обратиться к переменным, находящимся в других сегментах. Цепочку (строку) – источник, как правило, располагают в текущем сегменте данных, а её смещение задаётся регистром SI. Цепочка-получатель находится в дополнительном сегменте ES, а смещение – в регистре DI.

|

|

|

Таблица 1 |

|

Тип ссылки к памяти |

Сегмент по |

Альтернативный |

Смещение |

|

|

умолчанию |

сегмент |

|

|

Выборка команды |

CS |

Нет |

IP |

|

Стековая операция |

SS |

Нет |

SP |

|

Переменная |

DS |

CS, SS, ES |

EA |

|

Цепочка-источник |

DS |

CS, SS, ES |

SI |

|

Цепочка-приёмник |

ES |

Нет |

DI |

|

ВР как базовый регистр |

SS |

CS, SS, DS |

EA |

|

Смена сегментного регистра осуществляется с помощью однобайтового префикса замены сегмента 001SR110, который ставится перед первым байтом команды. Поле SR содержит код сегментного регистра: 00 – ES, 01 – CS, 10 – SS, 11 – DS.

3.3. Организация ввода – вывода во внешние устройства

Ввод и вывод информации в порты можно осуществить двумя способами: с использованием общего с памятью адресного пространства, т.е. с отображением на память (совмещённая адресация) и с использованием адресного пространства ввода – вывода (раздельная адресация). При раздельной адресации применяются специальные команды IN (ввод) и OUT (вывод), обеспечивающие передачу между аккумулятором и портами. При выполнении этих команд в минимальном режиме вырабатывается сигнал M/IO = 0, позволяющий вместе с сигналами WR и RD сформировать системные сигналы IOW и IOR для организации записи данных в порт и чтения из порта. В максимальном режиме системные сигналы IOW и IOR вырабатываются системным контроллером I8288 на базе сигналов состояния S0, S1, S2.

21

3.4. Назначение выводов микропроцессоров

Расположение выводов микропроцессоров I8086 и 8088 совпадает, отличие заключается лишь в использовании старшего байта адресной шины, в процессоре I8088 шина данных однобайтная, поэтому мультиплексирован только младший байт ША/ШД. Кроме этого, сигнал M/IO имеет инверсное значение относительно процессора I8086. Назначение выводов микропроцессора I8086 приведено в таблице 2. В зависимости от уровня сигнала на входе MN/MX процессоры могут работать в минимальном и максимальном режимах. В минимальном режиме микропроцессор сам вырабатывает сигналы управления для системы. Этот режим предназначен для построения небольших устройств, не использующих сопроцессоры или другие процессоры. В максимальном режиме сигналы управления системной шиной IOR (чтение внешнего устройства), IOW (запись во внешнее устройство), MEMR (чтение памяти), MEMW (запись в память), INTA (подтверждение прерывания) и ALE (или STB – строб записи адреса в регистр-защёлку) вырабатываются контроллером шины I8288 (К1810ВГ88) по сигналам состояния S0-S2.

|

|

|

|

|

|

|

Таблица 2. |

|

|

|

|

|

|||

Сигнал |

Вх/Вых |

|

Назначение в мин. Режиме |

Назнач.в макс. реж. |

|||

|

|

|

|

||||

AD[0:7] |

Вх/Вых (z) |

Address / Data – мультиплексированные |

Аналогично |

||||

|

|

сигналы шины адреса и данных. Адрес |

|

||||

|

|

присутствует в начале каждого машинного |

|

||||

|

|

цикла. В I8088 эти сигналы через регистр- |

|

||||

|

|

защелку выводятся на линии Addr[0:7] ши- |

|

||||

|

|

ны адреса и двунаправленным буферным |

|

||||

|

|

регистром |

соединяются |

с |

линиями |

|

|

|

|

Data[0:7] шины данных. У процессора 8086 |

|

||||

|

|

мультиплексирована 16-разрядная шина |

|

||||

|

|

AD[0:15] |

|

|

|

|

|

AD[8:15] |

Вх/Вых (z) |

Address / |

Data |

– сигналы |

шины адре- |

Аналогично |

|

|

|

са/данных в микропроцессоре I8086 (не |

|

||||

|

|

мультипликсированные у |

процессора |

|

|||

|

|

I8088). |

|

|

|

|

|

A[16:19] / |

Вых (z) |

Address / Status – старшие биты шины |

Аналогично |

||||

S[3:6] |

|

адреса, мультиплексированные с сигна- |

|

||||

|

|

лами состояния. Адрес присутствует в |

|

||||

|

|

первом такте каждого машинного цикла |

|

||||

|

|

(а при адресации ВУ – нули), после чего |

|

||||

|

|

сменяется признаками состояния. В би- |

|

||||

|

|

тах состояния S6=0, S5 отражает со- |

|

||||

|

|

стояние флага прерываний IF, S4 и S3 |

|

||||

|

|

указывают, какой сегментный регистр |

|

||||

|

|

используется в данном цикле (при об- |

|

||||

|

|

ращении к ВУ на S3 =0, на S4=1). В |

|

||||

|

|

I8086 информация состояния не ис- |

|

||||

|

|

пользуется, а эти сигналы через ре- |

|

||||

|

|

гистр-защелку |

поступают |

на |

линии |

|

|

22

|

|

Addr[16:19] шины адреса |

|

|

|

|

|

|

|

CLK |

Вх |

Clock – сигнал синхронизации процес- |

|

|

Аналогично |

|

|||

|

|

сора частотой 4,77 МГц (8МГц в Turbo- |

|

|

|

|

|

|

|

|

|

XT) |

|

|

|

|

|

|

|

RDY |

Вх |

Аппаратная проверка готовности, ис- |

|

|

Аналогично |

|

|||

|

|

пользуется для синхронизации работы |

|

|

|

|

|

|

|

|

|

МП и медленно действующей перифе- |

|

|

|

|

|

|

|

|

|

рии, 1 – есть готовность, 0 – нет готов- |

|

|

|

|

|

|

|

|

|

ности,вводятся такты ожидания; прове- |

|

|

|

|

|

|

|

|

|

ряется в каждом машинном цикле. |

|

|

|

|

|

|

|

TEST |

Вх |

Программная проверка готовности. |

|

|

Аналогично |

|

|||

|

|

Вход проверяется, если есть команда |

|

|

|

|

|

|

|

|

|

WAIT, 0 – есть готовность, 1 – нет го- |

|

|

|

|

|

|

|

|

|

товности, вводятся такы ожидания |

|

|

|

|

|

|

|

CLR |

Вх |

Сброс: регистры DS, ES, SS, флагов, |

|

|

Аналогично |

|

|||

|

|

указатель команд IP обнулены, конвей- |

|

|

|

|

|

|

|

|

|

ер команд пуст, в регистре CS |

все раз- |

|

|

|

|

|

|

|

|

ряды устанавливаются в 1. |

|

|

|

|

|

|

|

HLD |

Вх |

HLD – запрос захвата шины |

от внеш- |

RQ/GT0 – |

Request |

/ |

|||

RQ / GT0 |

Вх/Вых |

ней подсистемы (ВУ или контроллера |

Grant – сигнал запроса |

||||||

|

|

прямого доступа памяти) |

|

(Request) и предостав- |

|||||

|

|

|

|

ления (Grant) управле- |

|||||

|

|

|

|

ния локальной шиной, |

|||||

|

|

|

|

используется для свя- |

|||||

|

|

|

|

зи |

с |

сопроцессором |

|||

|

|

|

|

I8087 |

|

|

|

|

|

HLDA |

Вых |

HLDA – подтверждение захвата шины, |

RQ/GT1 – аналогич- |

||||||

RQ / GT1 |

Вх/Вых |

выдаётся в ответ на сигнал HLD после |

но |

RQ/GT0, |

но |

с |

|||

|

|

приостанова вычислительного процесса |

меньшим |

приорите- |

|||||

|

|

в МП и перевода шин и некоторых |

том. В I8086 не ис- |

||||||

|

|

управляющих сигналов в z- состояние. |

пользуется |

(на него |

|||||

|

|

|

|

подается лог. «1») |

|

||||

WR |

Вых (z) |

WR – запись, указывает на выполнение |

LOCK – Сигнал мо- |

||||||

LOCK |

Вых |

цикла записи в память или ВУ. |

|

нополизации |

управ- |

||||

|

|

|

|

ления шиной, выра- |

|||||

|

|

|

|

батывается на время |

|||||

|

|

|

|

выполнения |

коман- |

||||

|

|

|

|

ды по префиксу ин- |

|||||

|

|

|

|

струкции LOCK |

|

||||

NMI |

Вх |

Non Mascable Interrupt – сигнал, высо- |

|

|

Аналогично |

|

|||

|

|

кий уровень которого вызывает немас- |

|

|

|

|

|

|

|

|

|

кируемое прерывание NMI. |

|

|

|

|

|

|

|

INTR |

Вх |

Interrupt Request – сигнал запроса (вы- |

|

|

Аналогично |

|

|||

|

|

соким уровнем) маскируемого преры- |

|

|

|

|

|

|

|

|

|

вания. |

|

|

|

|

|

|

|

RESET |

Вх |

Сигнал аппаратного сброса (высоким |

|

|

Аналогично |

|

|||

|

|

уровнем). Синхронизированный сигнал |

|

|

|

|

|

|

|

|

|

сброса поступает через микросхему (ге- |

|

|

|

|

|

|

|

|

|

нератор тактовых импульсов) I8284. |

|

|

|

|

|

|

|

INTA |

Вых |

INTA – подтверждение запроса преры- |

QS0, |

QS1 |

– |

Queue |

|||

ALE |

|

вания, формируется в ответ на приня- |

Status |

– |

состояние |

||||

23

QS0, QS1 |

|

тый запрос прерывания INT, выполняет |

внутренней |

очереди |

||||

|

|

функцию сигнала RD в цикле подтвер- |

команд. Эти сигналы |

|||||

|

|

ждения прерывания и стробирует чте- |

поступают |

на одно- |

||||

|

|

ние вектора прерывания. |

|

именные входы |

со- |

|||

|

|

ALE (STB) – строб адреса, выдаётся в |

процессора I8087 |

|||||

|

|

начале каждого машинного цикла для |

|

|

|

|

|

|

|

|

записи адреса в регистр-защёлку |

|

|

|

|

|

|

|

|

|

|

|||||

DE |

Вых (z) |

DE – Сигнал разрешения передачи дан- |

ST0–Status – исполь- |

|||||

ST0 |

Вых (z) |

ных шинному формирователю по ШД |

зуется |

совместно с |

||||

|

|

|

|

сигналами |

ST1, |

ST2 |

||

|

|

|

|

(табл. 3). |

|

|

|

|

OP/IP |

Вых (z) |

OP/IP (DT/R) – передача/приём данных, |

Это |

сигналы состоя- |

||||

ST1 |

Вых (z) |

определяет направление |

передачи по |

ния, |

идентифицирую- |

|||

|

|

шине данных. 1 – запись данных , 0 – |

щие |

|

выполняемый |

|||

|

|

чтение. Предназначен для управления |

шинный цикл. Начало |

|||||

|

|

шинными формирователями по ШД и |

и конец цикла инди- |

|||||

|

|

действуют на протяжении всего цикла |

цируется |

переходом |

||||

|

|

шины. |

|

бит состояния из пас- |

||||

|

|

|

сивного (111) в актив- |

|||||

|

|

|

|

|||||

|

|

|

|

ное состояние и об- |

||||

|

|

|

|

ратно . |

|

|

|

|

M/IO |

Вых(z) |

M/IO – определяет обращение процес- |

Сигналы поступают на |

|||||

ST2 |

Вых(z) |

сора к памяти или к ВУ и используется |

входы |

контроллера |

||||

|

|

для разделения адресного пространства |

шины I8288, который |

|||||

|

|

памяти и внешних устройств. |

их декодирует в сиг- |

|||||

|

|

|

|

налы управления сис- |

||||

|

|

|

|

темной |

шиной |

IOR, |

||

|

|

|

|

IOW, |

|

|

MEMR, |

|

|

|

|

|

MEMWR, INTA и ALE |

||||

|

|

|

|

. |

|

|

|

|

RD |

Вых (z) |

Чтение, идентифицирует |

выполнение |

|

Аналогично |

|||

|

|

цикла чтения из памяти или ВУ. |

|

|

|

|

|

|

BHE / SТ7 |

Вых (z) |

Byte High Enable / Status 7 (только для про- |

|

Аналогично |

||||

|

|

цессора 8086) – разрешение старшего бай- |

|

|

|

|

|

|

|

|

та. Сигнал BHE указывает на присутствие |

|

|

|

|

|

|

|

|

данных на линиях AD[8:15]. Совместное |

|

|

|

|

|

|

|

|

использование BHE и младшей линии ад- |

|

|

|

|

|

|

|

|

реса А0 для дешифрации адресов позволяет |

|

|

|

|

|

|

|

|

осуществлять передачу слов или отдельных |

|

|

|

|

|

|

|

|

байтов по шине AD (табл. 4). ST7 – |

|

|

|

|

|

|

|

|

резервный выход. |

|

|

|

|

|

|

MN/MAX |

Вход |

Минимальный/максимальный – обеспе- |

|

Аналогично |

||||

|

|

чивает соответствующий режим работы |

|

|

|

|

|

|

|

|

микропроцессора. |

|

|

|

|

|

|

В таблице 3 приведены состояния сигналов на выходах процессора SТ0, SТ1, SТ2, используемых в максимальном режиме, и их декодирование. Они показывают тип машинного цикла, исполняемого в данный момент. Сигналы с этих выводов подаются на системный контроллер I8288 для формирования системных управляющих сигналов.

|

|

|

24 |

|

|

|

Таблица 3. |

|

|

|

|

SТ0 |

SТ1 |

SТ2 |

Тип цикла |

|

|

|

|

0 |

0 |

0 |

Подтверждение прерывания (INTA) |

0 |

0 |

1 |

Чтение порта (IORD) |

0 |

1 |

0 |

Запись в порт (IOWR) |

0 |

1 |

1 |

Останов (Halt) |

1 |

0 |

0 |

Выборка кода |

1 |

0 |

1 |

Чтение памяти (MEMRD) |

1 |

1 |

0 |

Запись в память (MEMWR) |

1 |

1 |

1 |

Пассивное состояние |

Лекция № 6

3.5. Организация адресного пространства памяти и ввода-вывода

Память логически организована как одномерный массив байтов, каждый из которых имеет 20-битовый физический адрес в диапазоне 00000 — FFFFF. (Для записи адресов здесь и далее используется 16-ричная система счисления.) Любые два смежных байта в памяти могут рассматриваться как 16-битовое слово. Младший байт слова имеет меньший адрес, а старший — больший. Такое размещение байтов слова используется также в I8080 и в большинстве современных микроЭВМ. Адресом слова считается адрес его младшего байта. Таким образом, 20-битовый адрес памяти может рассматриваться и как адрес байта, и как адрес слова.

Полная информация, необходимая для определения физического адреса, содержится в адресном объекте «сегмент : смещение», который называется указателем адреса и содержит адрес сегмента и внутрисегментное смещение. Для запоминания указателя адреса требуется два слова памяти, причем слово с меньшим адресом всегда содержит смещение, а слово с большим адресом — базовый адрес сегмента. Каждое слово хранится обычным образом, т. е. по принципу «младший байт — по меньшему адресу».

Команды, байты и слова данных можно свободно размещать по любому адресу, что позволяет экономить память благодаря ее плотной упаковке. Однако для экономии времени выполнения программы целесообразно размещать слова данных в памяти по четным адресам, так как МП передает такие слова за один цикл шины. Слово с четным адресом называется выравненным на границе слов. Слова с нечетными адресами (невыравненные) также допустимы, но для их передачи требуются два цикла шины, что снижает производительность МП. (Каждый цикл имеет четыре обязательных такта Т.) Отметим, что шинный интерфейс инициирует необходимое для выборки слова число обращений к памяти автоматически, так что двукратное обращение к памяти не требует специального указания в программе. Особенно важно иметь выравненные слова для операций со стеком, так как в них участвуют

25

только слова. Следовательно, указатель стека SP необходимо всегда инициализировать на четный адрес.

Команды всегда выбираются словами по четным адресам, за исключениием первой выборки после передачи управления по нечетному адресу, когда выбирается один байт. Поток команд разделяется на байты при заполнении очереди команд внутри МП, так что выравнивание команд не влияет на производительность и поэтому не используется.

Подключение блоков памяти.

При подключении ЗУ к шинам МПС необходимо обеспечивать передачу как двухбайтовых слов, так и отдельных байтов. С этой целью память выполняется в виде двух банков (рис. 5): младшего, подключаемого к линиям данных D7 – DO и содержащего байты с четными адресами (А0 = 0), и старшего, соединенного с D15 – D8 и содержащего байты с нечетными адресами (А0 = 1). Чтобы каждое слово передавалось за один цикл шины, слова располагают только с четных адресов. Напомним, что адресная линия АО совместно с линией разрешения старшего банка ВНЕ обеспечивает следующие варианты пересылок по шине данных:

А0 = 0, ВНЕ = 0 – пересылается слово; А0 = 0, ВНЕ = 1 – пересылается только младший байт;

A0 = l, BHE = 0 – пересылается только старший байт, А0 = 1, ВНЕ = 1 – устройство не выбрано.

Выработка сигнала ВНЕ и указанный порядок пересылок реализуются микропроцессором автоматически.

При чтении из ЗУ в любом случае на шину данных будет подаваться слово, из которого МП при необходимости выберет требуемый байт и поместит его в регистр, указанный в выполняемой команде. Поэтому сигналы ВНЕ и АО на ПЗУ не подаются. При записи в ЗУ необходимо различать старший и младший байты (иначе может происходить разрушение информации, хранящейся в соседнем байте). Для этого сигналы ВНЕ и АО подаются на входы CSH и CSL выбора старшего и младшего банков ОЗУ.

Процесс обращения к ПЗУ стробируется сигналом MEMR, а к ОЗУ – сигналами MEMR и MEMW, объединенными с помощью логического элемента И-НЕ. В примере, показанном на рис. 5, емкость каждого блока (ПЗУ и ОЗУ) составляет 8 Кбайт. Блок ПЗУ может быть, например, выполнен на основе двух включенных параллельно БИС К573РФ4 емкостью 8 Кбайт каждая, а блок ОЗУ – на основе восьми БИС К537РУ10 емкостью 2 Кбайт каждая. Адресные входы А12 – АО каждой пары БИС соединены параллельно и подключены к адресным линиям А13 – А1. Оставшаяся свободной линия А14 используется для различения блоков ПЗУ (А14 = 0) и ОЗУ (А14 = 1). В более общем случае для различения блоков ПЗУ и ОЗУ, а также для раздельной адресации страниц этих блоков осуществляется дешифрация старших адресных линий, например, с помощью ИС К155ИД4.

26

Рис. 5. Схема подключения банков памяти

*3.5.2. Средства и способы доступа к элементам структурной схемы

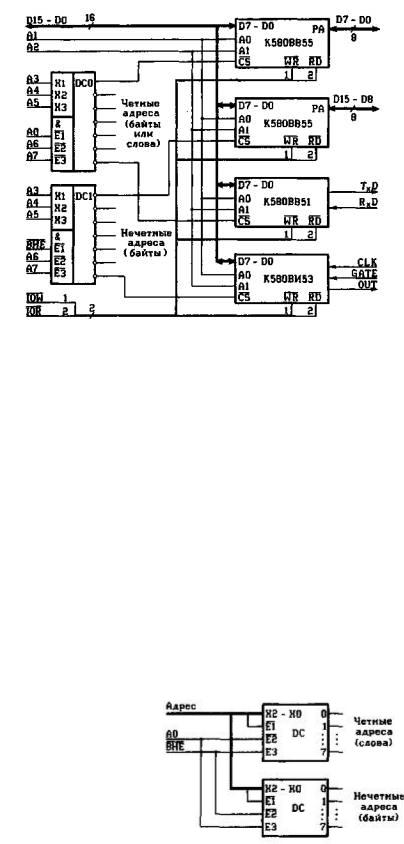

При подключении внешних устройств также возникает проблема передачи слов или отдельных байтов по шине данных (ШД) К устройствам, которые осуществляют обмен байтами и поэтому подключаются к младшей или старшей половине ШД, относятся, в частности, все программируемые БИС. В этом случае отдельно дешифруются четные и нечетные адреса ВУ (рис 6.), и полученные таким образом сигналы выбора CS подаются на соответствующие входы БИС. Устройства с четными адресами подключаются к младшей половине ШД (или ко всей ШД), а устройства с нечетными адресами — к старшей половине ШД. Если, например, необходимо передавать слова с помощью БИС интерфейса К580ВВ55, то параллельно включается две такие БИС, входы CS которых соединены с разными дешифраторами адреса. При этом имеется возможность передавать не только слова, но и отдельные байты, т е. обращаться индивидуально к каждой БИС. Если в этом нет необходимости, то входы CS обеих БИС можно подключить к одному выходу верхнего дешифратора DC

27

Рис. 6. Подключение программируемых БИС к микропроцессорной системе

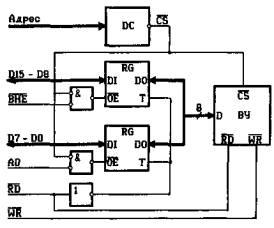

Несколько иной способ выработки сигналов CS показан на (рис. 7), где возможна передача слов по нечетному адресу, при которой МП последовательно передает два байта

Если в системе реализуется ввод – вывод, отображенный на память, т.е. используется совмещённая адресация, то могут потребоваться дополнительные дешифраторы.

При использовании ВУ, ориентированных на передачу байтов, может оказаться целесообразным преобразование двухбайтовой ШД в однобайтовую (рис. 8). Это, в частности, требуется для организации прямого доступа к памяти с помощью БИС контроллера ПДП К1810ВТ37 и для пересылки блоков данных между ЗУ и ВУ с помощью цепочечных команд. В последнем случае ввод – вывод должен быть организован с отображением на адресное пространство памяти. Устройства, подключаемые к однобайтовой шине данных, могут получать четные или нечетные адреса произвольно.

Рис.7 . Вариант дешифрации адресов ВЧ

28

Рис. 8. Схема преобразования двухбайтовой шины данных в однобайтовую для подключения ВУ

3.6.Основные особенности архитектуры микропроцессора I8088. Шинные циклы процессоров

Интегральная схема I8088 (К1810ВМ88) представляет собой 16битовый микропроцессор с 8-битовой внешней шиной данных. Он предназначен прежде всего для перевода аппаратных средств, построенных на базе МП К580ВМ80 и К580ВМ85, на программную среду МП К1810ВМ86 с целью повышения производительности этих средств. Его нередко используют и в оригинальных разработках, поскольку при этом упрощаются построение блоков памяти и разводка проводника на печатной плате по сравнению с МП К1810ВМ86. Микропроцессоры ВМ86 и ВМ88 имеют аналогичную архитектуру и одинаковую систему команд. В ВМ88 сохранены 16-битовые общие и сегментные регистры, АЛУ для обработки 16битовых операндов, сумматор для вычисления 20-битового физического адреса и средства поддержки многопроцессорных систем. Различия между этими двумя МП состоят в изменении разрядности шины данных и соответствующих изменениях структуры и работы шинного интерфейса.

Назначение и нумерация выводов БИС ВМ88 такие же, как БИС ВМ86, но линии адреса А15 – А8 используются только для выдачи адресов, а линия ВНЕ заменена линией состояния SSO, так как ВМ88 может обращаться только к байтам и надобность в сигнале разрешения старшего байта шины ВНЕ отпадает. При работе ВМ88 в минимальном режиме сигнал SSO логически эквивалентен сигналу состояния SO, который вырабатывается МП ВМ86 в максимальном режиме. Сочетание сигналов Ю/М, DT/R и SSO позволяет однозначно определить тип выполняемого цикла шины (табл. 4).

|

|

|

29 |

|

|

|

Таблица 4 |

Ю/М |

DT/R |

STO |

Тип цикла шины |

0 |

0 |

0 |

Подтверждениепрерывания |

0 |

0 |

1 |

Чтение из порта ввода – вывода |

0 |

1 |

0 |

Записьвпортввода– вывода |

0 |

1 |

1 |

Останов |

1 |

0 |

0 |

Выборкакоманды |

1 |

0 |

1 |

Чтениеданныхизпамяти |

1 |

1 |

0 |

Записьданныхвпамять |

1 |

1 |

1 |

Пассивное состояние (нет цикла шины) |

При работе ВМ88 в максимальном режиме на выводе 34 постоянно присутствует высокий потенциал.

Необходимо отметить, что инвертировано значение сигнала выбора памяти и внешних устройств, чтобы он совпадал с сигналом IO/М микропроцессора ВМ85. Однако остальные управляющие сигналы ВМ88 и ВМ85 различны, что требует существенного изменения логики управления шиной при введении ВМ88 в системы, выполненные на базе ВМ85. Изменения в подсистемах памяти и ввода – вывода могут быть небольшими (если не требуется увеличения емкости памяти), поскольку адреса и данные в ВМ88 мультиплексируются, как и в МП ВМ85. Значения адресных сигналов А15 – А8 запоминаются во внутреннем регистре МП, и их не нужно защелкивать во внешнем регистре с помощью строба ALE.

Длина очереди команд МП ВМ88 выбрана равной 4 байт, поскольку в отличие от ВМ86 ВМ88 может считывать только байты (а не слова) за один цикл шины и соответствующее увеличение времени выборки команд не позволяет полностью использовать 6-байтовую очередь для повышения производительности. Порядок опережающей выборки команд отличается тем, что ВМ88 инициирует цикл шины для выборки команды, когда в очереди оказывается один свободный байт, а не два, как в ВМ86. Передача в ВМ88 одного байта за цикл шины приводит к увеличению времени выполнения команд на четыре такта при передаче каждого слова. Поэтому при оценке времени выполнения команд необходимо учитывать число обращений к памяти и к портам ввода – вывода для передачи слов. Временные диаграммы сигналов МП ВМ88 (кроме А15 – А8) совпадают с диаграммами сигналов ВМ86 (рис. 9).