Цифровые устройства и микропроцессоры

.pdf180

добавляет 68 мнемоник, включающих арифметические, тригонометрические, экспоненциальные и логарифмические инструкции.

Процессор 80286 выпущен в 1982 году и представляет второе поколение 16-разрядных процессоров. Его существенным отличием является механизм управления адресацией памяти, обеспечивающий поддержку виртуальной памяти, а также средства для переключения задач (Task switching). К командам процессора 8086 добавляется несколько новых команд. Процессор может работать в двух режимах:

9086 Real Address Mode – реальный режим, полностью совместимый с

8086;

Protected Virtual Address Mode – защищенный режим виртуальной ад-

ресации. В этом режиме процессор позволяет адресовать до 16 Мб физической памяти, через которые при страничной адресации могут отображаться до 1 Гб виртуальной памяти каждой задачи.

За счет архитектуры МП 80286 с тактовой частотой 12,5 МГц работает более чем в 6 раз быстрее, чем 8086 с тактовой частотой 5 МГц. Параллельно разработан числовой процессор 80287, программно совместимый с 8087. Шина адреса разрядностью 24 бита позволяет адресовать 16 Мб физической памяти, но в реальном режиме доступен только 1 Мб, начинающийся с младших адресов.

Регистры 80286 в реальном режиме практически совпадают с регистрами 8086, есть некоторые изменения в регистре флагов. Защищенный режим еще не достаточно совершенен. Как и 8086/8088, процессор 80286 может обслуживать до 256 типов прерываний, они делятся на аппаратные, программные и исключения. Два первых типа прерываний аналогичны уже известным, исключения случаются при появлении особых условий при выполнении операций (в 8086/8088 аналогом исключений были внутренние прерывания процессора).

8.2. Реальный и защищенный режим

Изучив принципы работы микропроцессоров I8086 и I8088, нет необходимости пояснять особенности этого режима. До недавнего времени это был единственный режим, в котором функционировала операционная система MS-DOS. Для неё был разработан большой объём программного обеспечения, поэтому фирма Intel во всех модернизациях своего микропроцессора поддерживает этот режим. Его основные характеристики следующие :

пространство оперативной памяти делится на сегменты по 64 Кбайта. Сегменты в памяти могут перекрываться;

страничное преобразование адреса запрещено, то есть физический адрес равен линейному и формируется как сумма двух составляющих: 16разрядного эффективного адреса и 20-разрядного результата сдвига содержимого конкретного сегментного регистра на 4 разряда влево;

181

максимальное значение физического адреса равно 0FF FFFh, то есть 1 Мбайт, но, фактически, в реальном режиме адресуется на 64 Кбайт больше, что следует из следующего вычисления:

FFFF0 – максимальное значение сегментной части адреса, сдвинутое на 4 разряда влево;

+

0FFFF – максимальное значение смещения;

10FFEF = 1 114 096 байт – максимальный физический адрес в реальном режиме.

Защищенный режим (Protected Mode) предназначен для обеспечения независимости выполнения нескольких задач, т.е. ресурсы одной задачи защищены от воздействия другой задачи. Основным защищаемым ресурсом является память, в которой хранятся коды, данные и различные таблицы. Защита памяти основана на использование сегментации.

Сегмент, как известно – это блок адресного пространства памяти определенного назначения. Максимальный размер сегмента для процессоров 8086 и 80286 составляет 64 Кб, в 32-разрядных процессорах он отодвинулся до 4 Гб. Сегменты памяти выдаются задачами операционной системы, но в реальном режиме любая может переопределить значение сегментных регистров, задающих положение сегмента в памяти, и «залезть» в чужую область данных или кода. В защищенном режиме сегменты тоже распределяются операционной системой, но прикладная программа сможет использовать только разрешенные для нее сегменты памяти, выбирая их с помощью селекторов из таблиц дескрипторов сегментов. Появляются отличия в определении сегментных регистров. Сегментные регистры CS,DS,SS и ES хранят не сами

базовые адреса сегментов, а селекторы, по которым из таблицы, хранящейся в ОЗУ, извлекаются дескрипторы сегментов. Появились два новых термина, которые в дальнейшем используются во всех типах процессоров и требуют пояснения.

Селектор – это 16-разрядный указатель, загружаемый в сегментной регистр. С его помощью выбирается определенный дескриптор из таблицы дескрипторов, хранящихся в ОЗУ. Селектору имеют три поля:

TI (3р) – индикатор использования одной из таблиц дескрипторов, локальной или глобальной;

RPL (0-2р) – запрашиваемый уровень привилегий. Используется механизмом защиты системы;

NDEX (4-15р) – номер дескриптора в таблице.

Процессор умножает индекс восемь (это длина дескриптора) и добавляет результат к базовому адресу таблицы.

Дескрипторы хранятся в таблицах дескрипторов. Под каждой дескриптор отводится четыре смежных слова (8 байт). В дескрипторе указываются базовый адрес сегмента, размер сегмента, уровень защиты, размер операндов, тип сегмента и т.д. Дескрипторы 16 и 32-разрядных процессоров отличаются разрядностью поля базового адреса (24 бита для 80286 и 32 бита для

182

80386 процессоров) и трактовкой поля лимита ( т.е. длины сегмента), которое должно обеспечивать размер сегмента до 64 Кб или 4 Гб соответственно. Два старших байта у дескрипторов 80286 всегда нулевые (заранее зарезервированы для старших процессоров).

Защищенные режим предоставляет средства переключения задач. Состояние каждой задачи (значение всех связанных с ней регистров процессора) может быть сохранено в специальном сегменте состояния задач (TSS) , на который указывает селектор в регистре задачи. При переключении задач достаточно загрузить новый селектор в регистр задачи, и состояние предыдущей задачи автоматически сохранится в сегменте состояния задачи (TSS) .

8.3. Основные особенности архитектуры и программирования 32разрядных процессоров

Первым 32-разрядным процессором был Intel 386, выпущенный в 1985 году. Он имел 32-разрядные раздельные шины адреса и данных. Позже, в 1988 году, был разработан вариант процессора Intel 386 с 16-разрядной шиной данных и 24-разрядной шиной адреса, а полноразрядный вариант получил название Intel 386 DX. Как и в случае с 8088, это было сделано с целью удешевления компьютера, собранного на этом процессоре, хотя производительность компьютера снижалась приблизительно в два раза по сравнению с DX на той же тактовой частоте. Программные модели этих процессоров одинаковы.

В1990 году появился процессор Intel 386 со средствами управления энергопотреблением, разработанными специально для портативных компьютеров. В комплекте с ним выпускался набор периферии. По меркам сегодняшнего дня такие процессоры трудно считать высокопроизводительными, хотя на этом процессоре «вышел в люди» сначала оболочка. А потом OC MS WINDOWS , существенно изменив облик персональных компьютеров.

В32-разрядных процессорах обеспечена программная совместимость со своими 16-разрядными предшественниками, но в них преодолено очень жесткое ограничение на длину сегмента памяти – 64 Кб. В защищенном режиме оно отодвинулось до предела физически реализуемой памяти – 4 Гб. Эти процессоры имеют поддержку виртуальной памяти объемом 64 Тб, встроенный блок управления памятью поддерживает механизм сегментации

истраничной трансляции адресов. Процессоры обеспечивают четырехуровневую систему защиты памяти и устройств ввода-вывода (система привилегий), переключение задач.

Процессоры могут работать в двух режимах: реальном и защищенном. В реальном режиме возможна адресация до 1 Мб физической памяти, т.е. он работает как быстрый 8086, в защищенном режиме, как уже говорилось, до 4 Гб физической памяти и до 16 Тб виртуальной памяти каждой из 4-ех задач.

183

Весовым дополнением является режим виртуального процессора 8086 (Virtual 8086 Mode). Этот режим служит особым состоянием защищенного режима, в котором процессор функционирует как 8086. На одном процессоре в таком режиме могут одновременно исполняться несколько задач с изолированными друг от друга реальными ресурсами. Вычисление физического адресного пространства памяти производится механизмами сегментации и трансляции страниц.

В архитектуру процессоров введены средства отладки и тестирования. Существенным недостатком восьми и 16-разрядных микропроцессоров было их невысокое быстродействие, объясняемое не только низкой тактовой частотой, но и несовершенством архитектуры. Существенную роль в повышении быстродействия сыграла конвейеризация вычислений. Наиболее общий прием конвейеризации заключается в том, что во время выполнения предыдущей команды выбирается и декодируется следующая. Для 32разрядных процессоров характерна суперскалярная архитектура. Скалярным называют процессор с единственным конвейером. Конвейер – это специальное устройство, реализующее такой метод обработки команд в микропроцессоре, при котором выполнение команды разбивается на несколько этапов, при этом одновременно может выполняться ряд команд. Все процессоры Intel до 486 включительно относятся к скалярным, 1486 имеет пятиступенчатый

конвейер, включающий пять этапов: выборку команды; декодирование; вычисление адреса операндов; выполнение операции; запись результатов.

При использовании конвейера в МП на разной стадии выполнения могут находиться пять команд. Суперскалярный (superscalar) процессор имеет более одного конвейера, способных обрабатывать команды параллельно. Pentium является двухпотоковым процессоров (имеет два конвейера), Pentium Pro трехпотоковым, т.е. он может выполнять параллельно три выбранные команды.

8.4. Кэш-память

Следует остановиться на таком понятии, как кэширование памяти. Большое внимание на производительность вычислителей фон-неймановской архитектуры оказывают время доступа к памяти и ее пропускная способность. Кэширование – это способ увеличения быстродействия системы за счет хранения часто используемых данных и кодов в кэш-памяти. Кэшпамять представляет собой быстродействующее запоминающее устройство, размещенное в одном кристалле с процессором или же внешнее по отношению к процессору. Она служит высокоскоростным буфером между процессором и относительно медленной памятью. В процессоре I80386 использовалось только внешнее кэширование, организованное на дорогих микросхемах

184

SRAM. Идея кэш-памяти основана на предвосхищении наиболее вероятного использования процессором информации из основной памяти путем копирования ее в кэш-память. Следовательно, возникают понятия «кэш-попадание» и «кэш-промах». Эффективность кэш-попаданий выражается отношением успешных обращений к общему количеству обращений к кэш-памяти.

Предсказание адреса следующего обращения в память было бы невозможно, если бы программы обращались к памяти абсолютно произвольным образом. На самом же деле программы имеют тенденцию обращаться к памяти по адресу, близкому к адресу предыдущего обращения. Этот принцип на-

зывается локальностью программы или локальностью ссылок. Даже не-

большая кэш-память объемом 64 Кб обеспечивает коэффициент попадания до 90%, что оправдывает расходы. В таблицах приведенынекоторые данные по размерам и эффективностью обращения кэш-памяти, а также сделано сравнение обращений.

В таблице 33 приведено соотношение размера кэш-памяти с её эффективностью.

|

|

Таблица 33 |

|

РАЗМЕР КЭШ-ПАМЯТИ |

ПОПАДАНИЯ |

ВЫИГРЫШ |

|

|

|

|

|

Нет КЭШ, DRAM с двумя |

0% |

0% |

|

Tw |

|

||

|

|

|

|

16к |

81% |

35% |

|

|

|

|

|

32к |

86% |

38% |

|

|

|

|

|

64к |

88% |

39% |

|

|

|

|

|

128к |

89% |

39% |

|

|

|

|

|

Нет КЭШ, SRAM без Tw |

100% |

47% |

|

|

|

|

|

|

|

|

|

В таблице 34 приведены результаты сравнения обращений.

Таблица 34

ДЕЙСТВИЕ |

ТАКТЫ |

Некэшированное считывание: |

|

Выдача адреса в память |

1 |

Ожидание RAM |

2 |

Данные возвращаются |

1 |

Всего: |

4т.(2 Tw) |

Кэшированное считывание (попадание):

185

Выдача адреса в КЭШ-память |

|

Проверка КЭШ, выдача данных |

1 |

Всего: |

1 |

|

2т.(нет Tw) |

Кэшированное считывание (промах): |

|

Выдача адреса в КЭШ-память |

|

Проверка КЭШ, нет соответствия |

1 |

Выдача адреса в память |

1 |

Ожидание RAM |

1 |

Данные возвращаются |

2 |

Всего: |

1 |

|

6т.(4 Tw) |

|

|

Внутреннее кэширование обращений к памяти применяется в процессорах, начиная с I80486. В нем содержится один блок встроенной кэш-памяти размером 8 Кб, который используется для кэширования и кодов, и данных. Pentium имеет два блока кэш-памяти по 8 Кб, один для кода, другой для данных. Процессор становится более интеллектуальным. Pentium Pro также имеет две ступени встроенной кэш-памяти. Первый уровень кэширования состоит из четырехканального наборно-ассоциативного кэша инструкций и двухканального наборно-ассоциативного КЭШа данных. Длина строки КЭШа – 32 байта. Вторичный кэш, также смонтированный на процессоре, скрывает многие промахи первичного. В случае промаха на обоих уровнях минимальная задержка доставки данных из DRAM составляет 11-14 тактов одновременный доступ по записи и чтению, если эти запросы относятся к разным банкам кэш-памяти.

8.5. Архитектура микропроцессоров семейства Pentium

Процессоры Pentium представляют пятое поколение процессоров формы Intel. По архитектуре и системе команд они совместимы с 32-разрядными процессорами, но имеют 64-битную шину данных, из-за чего их иногда ошибочно называют 64-разрядными. По сравнению с предыдущими поколениями, процессоры Pentium имеют следующие отличия:

суперскалярная архитектура: процессор имеет два параллельно работающих конвейера обработки команд (U-конвейер с полным набором инструкций и V-конвейер с несколько ограниченным набором). Благодаря этому процессор способен одновременно выполнять две команды (при специальном режиме компиляции программного обеспечения);

применение технологии динамического предсказания ветвлений вместе с внутренним КЭШем команд объемом 8 Кб обеспечивает максимальную загрузку конвейеров;

внешняя шина данных ради повышения производительности имеет разрядность 64 бит, что требует соответствующей организации памяти;

186

встроенный сопроцессор за счет улучшения архитектуры в 2-10 раз превосходит сопроцессор 486 по производительности;

введено несколько инструкций. В том числе распознавание семейства и модели CPU;

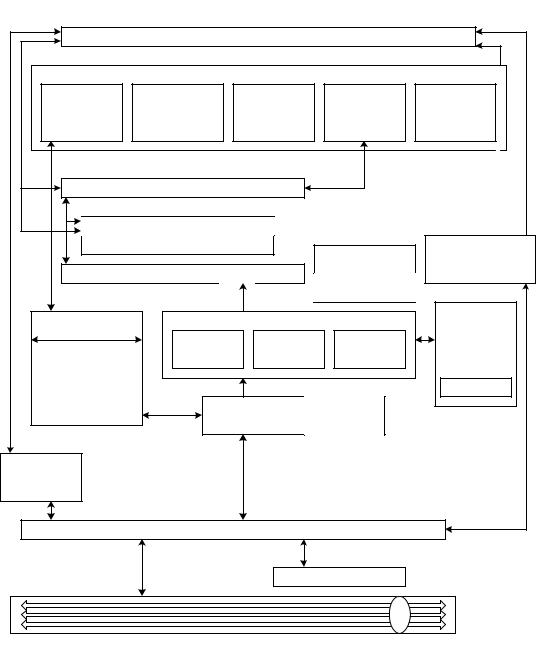

введены средства управления энергопотреблением Обратимся к структурной схеме микропроцессора, представленной на

рис.82 .

Рис. 82. Структурная схема микропроцессора семейства P6 (Pentium Pro/II/III) В структурную схему входят:

подсистема памяти;

187

блок выборки/декодирования; буфер переупорядоченных команд;

устройство диспетчеризации/исполнения.

Подсистема памяти состоит из КЭШа первого уровня L1 (команд и

данных), кэша второго уровня, устройства шинного интерфейса и системной шины, устройства связи с памятью и буфера переупорядочивания запросов к памяти. Устройство шинного интерфейса обращается к оперативной памяти системы через 64-разрядную внешнюю шину. Во время обслуживания одного запроса формируется ряд других, обрабатываемых в порядке поступления. Любой внутренний запрос процессора на обращение к памяти направляется во внутренний кэш. Если адресуемая область представлена в кэш-памяти (случай попадания – cache hit), запрос на чтение обслуживается только кэшпамятью, не выходя на внешнюю шину. Запрос на запись изменяет строку кэш, и в зависимости от политики записи либо сразу выходит на внешнюю шину (при сквозной записи), либо несколько позже (при использовании алгоритма обратной записи). При записи в кэш-память данных процессор использует один из следующих способов модификации данных:

сквозная запись, при которой запись в строку кэш обновляет кэшпамять и основную;

обратная запись, при которой модифицируется только строка в кэшпамяти. Этот способ записи приводит к сокращению за счет исключения ненужной записи в основную память. Перезапись модифицированной строки из кэш-памяти в основную производится посредством обратной записи, производимой при удалении строки из кэш-памяти.

В случае промаха (Cache Miss) запрос на запись направляется только на внешнюю шину, а запрос на чтение обслуживается сложнее. Если этот запрос относится к кэшируемой области памятью, то выполняется цикл заполнения целой строки КЭШа (т.е. для Pentium – 32 байта) из оперативной памяти самым быстрым способом (64-битными передачами).

Запросы на данные из памяти в исполнительном устройстве обеспечивается с помощью устройства связи с памятью и буфера переупорядочивания запросов к памяти. Буфер отслеживает все запросы данных; если таковые отсутствуют в кэш-памяти данных первого уровня (L1) , инициируется обраще-

ние к кэшу второго уровня (L2 ). Если в кэше L2 операндов не оказалось, бу-

фер переупорядочивания запросов к памяти заставляет устройство шинного интерфейса сформировать запрос к оперативной памяти.

Блок выборки/декодирования состоит из устройства выборки команд, буфера предсказаний переходов, декодера инструкций, блока микропрограммного управления и таблицы регистровых алиасов. Поток команд из КЭШа команд (L1) декодируется в последовательность микроопераций при

помощи трех параллельно работающих декодеров. Микрооперации выполняются пятью исполнительными устройствами, работающими параллельно. Порядком исполнения микроопераций занимается блок микропрограммного

188

управления. Декодер команд может формировать до шести микроопераций за такт. После декодирования команд порядок выполнения микроопераций трудно предсказать. Поэтому могут возникнуть трудности с использованием регистров. Эта проблема называется проблемой ложных взаимозависимостей и реализуется механизмом переименования регистров. Для этого в вычислительных процессах используется дополнительный набор из 40 внутренних регистров. Информация о действительных именах регистров процессора иих внутренних именах (номерах универсальных регистров) помещается в таблицу регистровых алиасов. С помощью этой таблицы микрооперации готовятся к неупорядоченному выполнению.

Буфер переупорядоченных команд содержит команды, переупорядо-

ченные для оптимальной загрузки конвейера. Он представляет собой массив памяти, выполненный в виде 40 регистров. В них находятся микрокоманды, ожидающие своей очереди на исполнение и уже частично выполненные, но из-за переупорядочивания исполнения команд не до конца.

Устройство диспетчеризации/исполнения содержит буфер микроопе-

раций, готовых к исполнению два исполнительных устройства для целочисленных операций, два – для чисел с плавающий точкой и устройство связи с памятью (это деление достаточно условно). Такая организация позволяет за один такт выполнить пять микроопераций. Устройство диспетчеризации/исполнения может выбирать микрооперации из буфера переупорядоченных команд в любом порядке. Порядок исполнения микроопераций определяет специальный буфер, называемый буфером команд, готовых к исполнению. Микрооперации, готовые к работе, отправляются в соответствующие исполнительные устройства. Результаты исполнения возвращаются в буфер переупорядоченных команд, где будут храниться до тех пор, пока не будут удалены устройством удаления и восстановления.

Два целочисленных исполнительных устройства могут параллельно обрабатывать две целочисленные микрооперации. Исполнительные устройства с плавающей точкой обрабатывают вещественные числа.

Устройство связи с памятью управляет загрузкой и сохранением данных для микроопераций. Последним в работу схемы выполнения команд исходной программы вступает блок удаления и восстановления, восстанавливающий исходную последовательность команд. Он постоянно проверяет буфер переупорядоченных команд для обнаружения полностью выполненных микроопераций. Такие микрооперации удаляются из буфера и восстанавливаются в исходном порядке. При этом результаты операций записываются в реальные регистры микропроцессора и в оперативную память.

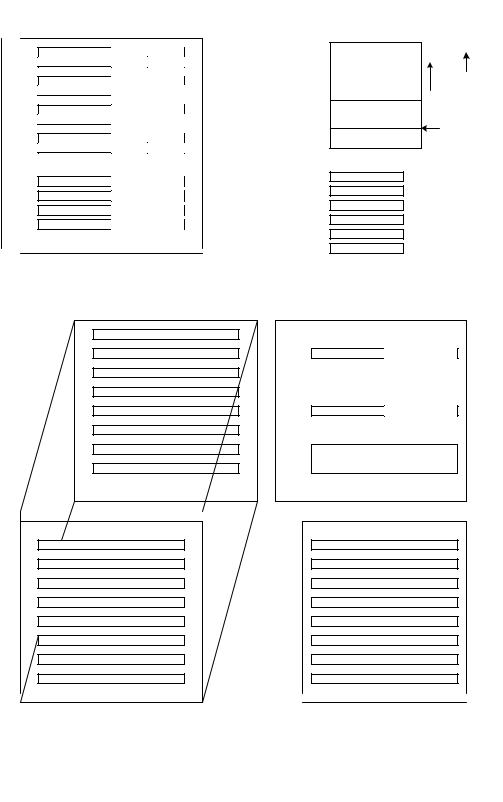

На этом пока завершим обсуждение общих вопросов, связанных с архитектурой. При разработке программ каждый программист получает в свое распоряжение определенный ресурс микропроцессора, необходимый для выполнения и хранения в памяти команд, данных и служебной информации. Набор этих ресурсов представляет программную модель микропроцессора. На рис. 83 представлена программная модель микропроцессора Pentium Ш.

189

Рис. 83. Программная модель микропроцессора Pentium Ш

Следует отметить, что возросшая производительность процессора Pentium требует и соответствующей организации системы на его основе. Компания Intel разработала и поставляет все необходимые для этого наборы микросхем. Прежде всего, для согласования скорости с динамической основной памятью необходима кэш-память второго уровня. Контроллер кэш-