Цифровые устройства и микропроцессоры

.pdf

11

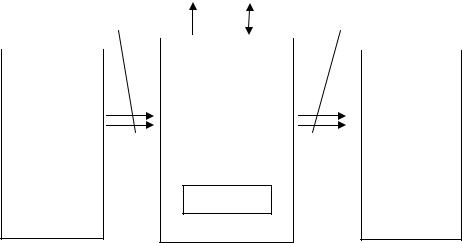

па и т. д.). Эти же устройства представляют информацию в необходимую для процессора форму.

|

|

|

|

П А М Я Т Ь |

|

|

|

|

Шины ввода |

|

|

|

|

Шины вывода |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

ПРОЦЕССОР |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Устройство |

|

|

|

|

УСТРОЙ- |

|

|

управления |

|

|

УСТРОЙ- |

||

|

|

|

|

|

||||

СТВА |

|

|

|

|

|

СТВА |

||

|

|

Арифметико- |

|

|

||||

ВВОДА |

|

|

|

|

ВЫВОДА |

|||

|

|

|

|

логическое |

|

|

|

|

|

|

|

|

устройство |

|

|

|

|

|

|

|

|

|

|

|

|

|

Регистры

Рис.1. Структурная схема вычислительного устройства

Память представляет собой устройство, хранящее:

−совокупность команд, образующих программу;

−обрабатываемые данные.

Память состоит из ячеек, хранящих набор бит, составляющих информа-

ционные слова. Ячейки нумеруются числами, называемыми адресом ячейки. Если необходимо записать или считать информационное слово. Следует подать на шину адреса требуемый адрес. Таким образом, процессор связан с памятью однонаправленной шиной адреса (ША) и двунаправленной шиной данных (ШД). Кроме основной памяти в компъютерах имеется внешняя память для долговременного хранения программ и данных. Для этого используются накопители на магнитных дисках и т. д.

Устройства вывода представляют результаты обработки информации в форме, удобной для восприятия.

Лекция № 3

2.2. Классификация микропроцессоров

Микропроцессор характеризуется очень большим числом параметров и качеств, поскольку обеспечивает эффективное автоматическое выполнение операций обработки цифровой информации в соответствии с заданным алгоритмом.

По числу БИС в микропроцессорном комплекте различают микропро-

цессоры однокристальные и многокристальные секционированные (микропрограммируемые). Однокристальные получаются при реализации всех аппаратурных средств в виде одной БИС, они имеют фиксированную систему

12

команд. Секционированные микропроцессоры получаются в том случае, когда в виде БИС реализуются части (секции) структуры процессора при функциональном разбиении её вертикальными плоскостями. Для построения многоразрядных микропроцессоров при параллельном включении секций МП в них добавляются средства «стыковки», чем достигается возможность работы с требуемой разрядностью слов. (Принцип микропрограммирования приведён в конце раздела).

По назначению различают универсальные и специализированные микропроцессоры.

Универсальные микропроцессоры предназначаются для решения широкого круга задач и применения в различных вычислительных системах

Специализированные процессоры включают в себя цифровые сигнальные процессоры и микроконтроллеры. Цифровые сигнальные процессоры – рассчитаны на обработку в реальном времени цифровых потоков, образованных путем оцифровывания аналоговых сигналов. Это обусловливает их сравнительно малую разрядность и преимущественно целочисленную обработку. Однако современные сигнальные процессоры способны проводить вычисления с плавающей точкой над 32 – 40-разрядными операндами. Кроме того, появился класс медийных процессоров, представляющих собой законченные системы для обработки аудио- и видеоинформации.

Микроконтроллеры – обладают наибольшей специализацией и разнообразием функций. Используются во встроенных системах управления, в том числе в бытовых приборах.

CISC (Complete Instruction Set Computer) – Микропроцессоры с пол-

ным набором команд. Такие микропроцессоры используют программирование на языке команд и выполняются на одном кристалле. Они имеют фиксированную разрядность слова данных и фиксированный набор команд. Каждая команда представляет собой определенную последовательность микрокоманд. На ее выполнение может затрачиваться несколько машинных циклов (обращений к внешней памяти), каждый из которых включает в себя 1…5 (а иногда и более) рабочих тактов.

RISC (Reduce Instruction Set Computer) – Микропроцессоры с сокра-

щенным набором команд. Основная особенность RISC-процессоров состоит в использовании небольшого набора часто используемых команд одинакового формата, которые могут быть выполнены за один командный цикл (такт). Более сложные, редко используемые команды реализуются на программном уровне. Однако за счет значительного повышения скорости выполнения сокращенного набора команд средняя производительность RISC-процессоров оказывается выше, чем у CISCпроцессоров.

2.3. Принцип микропрограммного управления

Секционированные микропроцессоры работают не на программном, а на микропрограммном уровне, поэтому не имеют своей системы команд. Они

13

могут использовать систему команд какого-либо однокристального процессора, разбивая его команды на микрокоманды или просто разрабатываются программы на микропрограммном уровне. Микропрограммное устройство управления состоит из микропрограммной памяти и схемы формирования адресов микрокоманд. Микрокоманда содержит в общем случае три поля: поле управления генерацией адреса следующей микрокоманды, поле управления длительностью такта, поле управления операционной частью микропроцессора.

Для эффективного применения комплекта К1804 необходимо знать принципы микропрограммного управления в ЭВМ. В микропрограммной ЭВМ для выполнения различных операций используется однородная последовательность микрокоманд. Выполнение машинной команды интерпретируется набором микрокоманд, образующих микропрограмму. Элементарные функции, реализуемые при выполнении микрокоманды, инициируются микрокомандами. Обычно микрокоманда выполняет две главные функции: определение и управление всеми микрооперациями, определение и управление адресом –следующей микрокоманды. Первая функция связана с выбором операндов для АЛУ, заданием операции АЛУ, выбором получателя результата АЛУ, управлением переносом, сдвигом, прерываниями, вводом и выводом данных и т.д. Вторая функция – выбор источника адреса следующей микрокоманды, иногда этот адрес определяется явно.

В блоке микропрограммного управления (БМУ) имеется микропрограммная память М х N. Диапазон адресов составляет от 0 до N-1 . Каждое слово (микрокоманда) состоит из М бит, разделенных на поля различной длины. Определение полей называется форматом микрокоманды. В типичной ЭВМ микрокоманда содержит следующие поля: 1 — общего назначения, 2 — адрес перехода (адрес микропрограммной памяти), 3 — функция управления адресом следующей микрокоманды, 4 — управление прерыванием, 5 — управление выбором синхронизации, 6 — управление переносом, 7 — управление источниками операндов АЛУ, 8 — управление функцией АЛУ, 9 — управление получателем результата АЛУ.

Более подробно вопросоы микропрограммирования будут рассмотрены далее в разделе 9 при изучении секционированных микропроцессоров.

3.АРХИТЕКТУРА 16-РАЗРЯДНЫХ ПРОЦЕССОРОВ I8086/88

3.1.Архитектура микропроцессора I8086/88 (К1810ВМ86/88)

3.1.1.Введение

Микропроцессор 8086 фирмы Intel содержит на кристалле около 29000 транзисторов и производится по МОП-технологии. Процессоры I8086 и выпущенный годом позже его модифицированный вариант I8088 выполняют 8/16битные логические и арифметические операции, включая умножение и деление, операции со строками и операции ввода-вывода. Процессоры имеют 20-

14

разрядную шину адреса (ША), позволяющую адресовать 1 Мб памяти. Шина данных у микропроцессоров I8086, у I8088 – 8-разрядная. Это сокращение, сделанное с целью удешевления системы, поскольку предоставляет возможность использования ранее разработанного программного обеспечения, оборачивается некоторым снижением производительности: I8086 за счёт большей разрядности ШД работает примерно на 20-60 % быстрее, чем I8086 c такой же тактовой частотой. С программной точки зрения эти процессоры идентичны, их система команд и набор регистров включены во все процессоры РСсовместимых процессоров. От процессора I8086 пошло общее обозначение семейства: х 86.

Процессоры поддерживают аппаратные и программные прерывания, предусмотрено использование математического сопроцессора, повышающего производительность вычислений.

В процессорах применена конвейерная архитектура, позволяющая выполнить выборку кодов команд из памяти и их дешифрацию во время выполнения внутренних операций. Это сокращает время простоя его операционных узлов.

Лекция № 4 3.1.2. Структурная схема

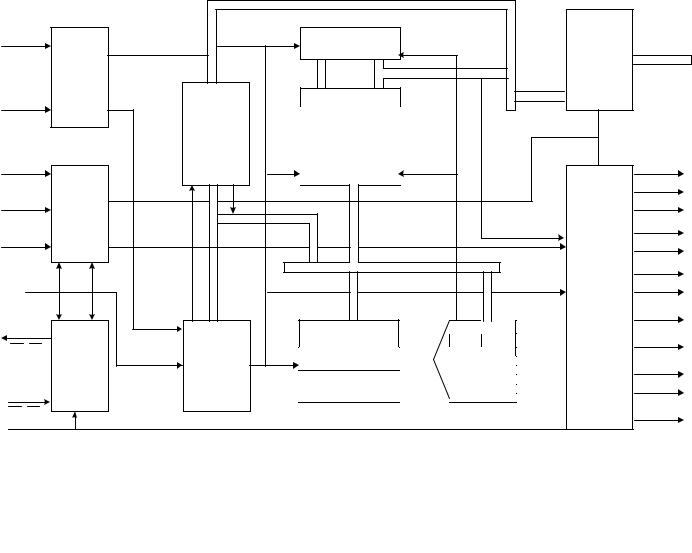

Структурная схема микропроцессора представлена на рисунке 2. Структуру микропроцессора можно условно разбить на три части: опера-

ционное устройство, устройство сопряжения с шиной и управляющее устройство.

Операционное устройство. В операционном устройстве декодируются команды и обрабатываются данные, т. е. осуществляется сам процесс выполнения команды. В состав операционного устройства входят: 16-разрядное арифмети-

ко-логическое устройство (АЛУ) с тремя регистрами временного хранения и регистром признаков и восемь 16-разрядных регистров. АЛУ выполняет различные арифметические и логические операции, а также операции сдвига.

Поскольку АЛУ является комбинационной схемой, регистры временного хранения необходимы для хранения операндов во время выполнения операций, программисту они не доступны.

Блок регистров состоит из четырёх 16-разрядных регистров А, В, С, D, двух указательных (SP,BP) и двух индексных регистров (SI, DI). Для первых четырёх регистров общего назначения (РОНов) существует возможность их использования как раздельных восьмиразрядных. Если РОН используется как 16разрядный – добавляется буква Х, если как 8-разрядный – символ Н для левой группы (от английского слова high) и буква L для правой группы (от слова low), т. е. старшие и младшие байты. Аккумулятор (А) называют собственным регистром АЛУ, его функции довольно разнообразны. Операционное устройство. В операционном устройстве декодируются команды и обрабатываются данные, т. е. осуществляется сам процесс выполнения

15

команды. В состав операционного устройства входят: 16-разрядное арифмети- ко-логическое устройство (АЛУ) с тремя регистрами временного хранения и регистром признаков и восемь 16-разрядных регистров. АЛУ выполняет различные арифметические и логические операции, а также операции сдвига.

Поскольку АЛУ является комбинационной схемой, регистры временного хранения необходимы для хранения операндов во время выполнения операций, программисту они не доступны.

Блок регистров состоит из четырёх 16-разрядных регистров А, В, С, D, двух указательных (SP,BP) и двух индексных регистров (SI, DI). Для первых четырёх регистров общего назначения (РОНов) существует возможность их использования как раздельных восьмиразрядных. Если РОН используется как 16разрядный – добавляется буква Х, если как 8-разрядный – символ Н для левой группы (от английского слова high) и буква L для правой группы (от слова low), т. е. старшие и младшие байты. Аккумулятор (А) называют собственным регистром АЛУ, его функции довольно разнообразны. Операционное устройство. В операционном устройстве декодируются команды и обрабатываются данные, т. е. осуществляется сам процесс выполнения команды. В состав операционного устройства входят: 16-разрядное арифмети-

ко-логическое устройство (АЛУ) с тремя регистрами временного хранения и регистром признаков и восемь 16-разрядных регистров. АЛУ выполняет различные арифметические и логические операции, а также операции сдвига.

Поскольку АЛУ является комбинационной схемой, регистры временного хранения необходимы для хранения операндов во время выполнения операций, программисту они не доступны.

Блок регистров состоит из четырёх 16-разрядных регистров А, В, С, D, двух указательных (SP,BP) и двух индексных регистров (SI, DI). Для первых четырёх регистров общего назначения (РОНов) существует возможность их использования как раздельных восьмиразрядных. Если РОН используется как 16разрядный – добавляется буква Х, если как 8-разрядный – символ Н для левой группы (от английского слова high) и буква L для правой группы (от слова low), т. е. старшие и младшие байты. Аккумулятор (А) называют собственным регистром АЛУ, его функции довольно разнообразны. Операционное устройство. В операционном устройстве декодируются команды и обрабатываются данные, т. е. осуществляется сам процесс выполнения команды. В состав операционного устройства входят: 16-разрядное арифмети-

ко-логическое устройство (АЛУ) с тремя регистрами временного хранения и регистром признаков и восемь 16-разрядных регистров. АЛУ выполняет различные арифметические и логические операции, а также операции сдвига.

Поскольку АЛУ является комбинационной схемой, регистры временного хранения необходимы для хранения операндов во время выполнения операций, программисту они не доступны.

Блок регистров состоит из четырёх 16-разрядных регистров А, В, С, D, двух указательных (SP,BP) и двух индексных регистров (SI, DI). Для первых четырёх регистров общего назначения (РОНов) существует возможность их ис-

16

пользования как раздельных восьмиразрядных. Если РОН используется как 16разрядный – добавляется буква Х, если как 8-разрядный – символ Н для левой группы (от английского слова high) и буква L для правой группы (от слова low), т. е. старшие и младшие байты. Аккумулятор (А) называют собственным регистром АЛУ, его функции довольно разнообразны. Операционное устройство. В операционном устройстве декодируются команды и обрабатываются данные, т. е. осуществляется сам процесс выполнения команды. В состав операционного устройства входят: 16-разрядное арифмети-

ко-логическое устройство (АЛУ) с тремя регистрами временного хранения и регистром признаков и восемь 16-разрядных регистров. АЛУ выполняет различные арифметические и логические операции, а также операции сдвига.

Поскольку АЛУ является комбинационной схемой, регистры временного хранения необходимы для хранения операндов во время выполнения операций, программисту они не доступны.

Блок регистров состоит из четырёх 16-разрядных регистров А, В, С, D, двух указательных (SP,BP) и двух индексных регистров (SI, DI). Для первых четырёх регистров общего назначения (РОНов) существует возможность их использования как раздельных восьмиразрядных. Если РОН используется как 16разрядный – добавляется буква Х, если как 8-разрядный – символ Н для левой группы (от английского слова high) и буква L для правой группы (от слова low), т. е. старшие и младшие байты. Аккумулятор (А) называют собственным регистром АЛУ, его функции довольно разнообразны.

Кроме того, что в РОНах могут храниться данные, участвующие в операциях, каждый регистр имеет ещё своё специфическое назначение, неявно подразумеваемое в некоторых командах:

АХ – умножение, деление, ввод и вывод слова;

AL – умножение, деление, ввод и вывод байта, десятичная арифметика, трансляция (XLAT);

АН – умножение и деление слова; ВХ – трансляция, адресация по базе;

СХ – счётчик циклов и указатель длины строковых операций; ДХ – умножение и деление слова, ввод и вывод с косвенной адресацией.

Регистры – указатели SP, BP и индексные регистры SI и DI главным образом хранят адресную информацию.

SP (Stack Pointer – указатель стека) – операции со стеком; BP (Base Pointer – указатель базы) – обращение к стеку;

SI (Sours Index – индекс источника) – смещение адреса в текущем сегменте данных DS;

DI (Destination Index – индекс приёмника) – смещение адреса в дополнительном сегменте ES.

17 |

17

Регистр признаков (F) состоит из нескольких триггеров, называемых флажками (рис. 3). Он хранит признаки результатов выполнения арифметических и логических операций и управляющие триггеры. Команды пересылок на флаги не воздействуют. Назначение флагов:

CF (Carri Flag) – флаг переноса (заёма) старшего бита в арифметических операциях;

PF (Pariti Flag) – флаг паритета, устанавливается при чётном числе единиц в результате;

15р 14р 13р 12р 11р |

10р 9р |

8р 7р 6р 5р 4р 3р 2р 1р 0р |

|||||||||||||

|

|

|

|

OF |

DF |

IF |

TF |

SF |

ZF |

|

AF |

|

PF |

|

CF |

Рис. 3. Регистр флагов

AF (Auxiliary Flag) – флаг дополнительного переноса (заёма) в тетраде для десятичной арифметики;

ZF (Zero Flag) – флаг нулевого результата.

SF (Sign Flag) – флаг знака. Если в триггере устанавливается единица, флаг отрицательный.

TF (Trap Flag) – флаг трассировки (пошагового режима). При установке этого флага после выполнения каждой команды вызывается внутреннее прерывание 1-го типа (INT 1).

IF (Interrapt Flag) – флаг управления прерываниями. При единичном значении разрешается выполнение маскируемых аппаратных прерываний.

DF (Direction Flag) – флаг управления направлением в строковых операциях. При единичном значении индексные регистры, участвующие в строковых операциях, автоматически декрементируются на количество байт операнда, при нулевом – инкрементируются.

OF (Overflow Flag) – флаг переполнения. Устанавливается, если результат арифметической команды не умещается в операнде назначения.

Устройство сопряжения с шиной осуществляет связь с ВУ, обеспечивает выборку команд и данных из памяти, формирует очередь команд.

В состав устройства сопряжения с шиной входят: сегментные регистры CS, DS, SS и ES, указатель команд IP, сумматор адреса, регистры очереди команд и буферы, обеспечивающие связь с шинами адреса и данных.

Блок очереди команд у I8086 имеет 6-байтную организацию. Блок предварительной выборки при наличии двух свободных регистров в очереди старается её заполнить в то время, когда внешняя шина процессора не занята операциями обмена. Очередь у процессора I8088 сокращена до 4 байт, а предварительная выборка выполняется уже при наличии одного свободного байта. Очередь обнуляется при выполнении любой команды передачи управления. Конвейерный принцип, при котором пока одна команда исполняется в операцион

18

ном устройстве, другая команда выбирается из памяти, повышает скорость выполнения программы.

Буферы представляют собой 16 двунаправленных усилителя с тремя выходными состояниями для линий AD0 – AD15. Для линий А16 – А19 буферы содержат четыре однонаправленных усилителя с тремя выходными состояниями.

Особое место занимают 16-битные регистры – указатели сегментов CS (Code Segment – сегмент кодов команд), DS (Date Segment – сегмент данных), ES (Extra Segment – дополнительный сегмент данных), SS (Stack Segment – сег-

мент стека). Содержимое этих регистров не может быть изменено никакими командами, кроме команд их загрузки.

Регистры CS, DS, SS, ES предназначены для указания начала области (сегмента) памяти и используются при обращении к памяти для вычисления адресов ячеек.

CS – регистр сегмента программы, определяет начальный адрес сегмента памяти, в котором располагается программа. Выборка очередной команды осуществляется относительно содержимого CS с использованием значения указателя команд IP.

DS – регистр сегмента данных, определяет начальный адрес текущего сегмента данных. Вычисление физического адреса в этом сегменте зависит от способа адресации.

ES – регистр дополнительного сегмента данных

SS – регистр сегмента стека, определяет начало стекового сегмента и используется в командах обращения к стеку, при обработке прерываний и подпрограмм. (Стек – это сегмент памяти, работающий по принципу LIFO (Last in first out – вошедший последним выходит первым)).

IP – указатель команд, является смещением в сегменте кода относительно начала сегмента.

Более подробно описание функций этих регистров приведено в следующем разделе.

Сумматор адресов формирует 20-разрядный физический адрес, суммируя два логических адреса: базовый логический адрес, находящийся в одном из сегментных регистров и смещение в сегменте. Более подробно описание описание этого процесса приведено в следующем разделе.

Буферы обеспечивают связь с шинами адреса и данных для передачи логического нуля и единицы о обладая возможностью переходить в так называемое «третье», высокоимпедансное состояние.

Управляющее устройство дешифрирует команды, формирует управляющие сигналы, обеспечивающие функционирование вычислительной системы, а также микроприказы для внутренних действий МП.

19

Лекция № 5

3.2. Сегментация памяти, вычисление адресов

Сегмент представляет собой независимый, поддерживаемый на аппаратном уровне блок памяти. Каждая программа в общем случае может состоять из любого количества сегментов, но непосредственный доступ она имеет только к четырём сегментам: кода CS, данных DS, стека SS и дополнительного сегмента данных ES (для 32-х разрядных процессоров серии Intel вводятся ещё два дополнителных сегмента FS и GS). В компъютере программа никогда не знает, по каким физическим адресам будут размещены её сегменты, этим занимается её операционная система. Она размещает сегменты программы в оперативной памяти по определённым физическим адресам, после чего помещает значения этих адресов в соответствующие сегментные регистры. В самостоятельно разрабатываемом вычислителе проблема инициализации сегментных регистров и распределение ресурсов памяти лежит на разработчике аппаратуры и программного обеспечения. Внутри сегмента программа обращается к адресам относительно начала сегмента, то есть, начиная с нуля и заканчивая адресом, равным размеру сегмента (его максимальный объём может быть 64 кб). Этот относительный адрес или смещение, используемое микропроцессором для доступа к данным внутри сегмента, называется эффективным (ЕА) или исполнительным. (В руководствах фирмы Intel термин «эффективный адрес» применяется в контексте машинного языка, а термин «смещение» (offset) – в контексте языка ассемблера. Слово «смещение» (displasement) означает величину, которая прибавляется к содержимому регистра(ов) для образования ЕА.)

Сегменты могут быть смежными, следовать с интервалом или перекрываться. Каждый сегмент начинается на 16-байтной границе( так называемая граница параграфа).

Для вычисления 20-разрядного физического адреса содержимое каждого сегментного регистра (CS, DS, SS, ES) рассматривается как 16 старших разрядов А4–А19 начального адреса соответствующего сегмента. Младшие разряды А0–А3 полагаются равными нулю и приписываются справа при вычислении физического адреса. Вычисление производится в сумматоре и состоит в сложении 20-разрядного начального адреса сегмента с 16-разрядным смещением, которое дополняется четырьмя старшими разрядами, равными нулю (рис. 4).

Эффективный адрес (смещение) |

0000 |

+ |

16 |

бит |

|

Базовый сегментный адрес |

|

|

|

0000 |

|

16 |

бит |

|

|||

Физический адрес |

= |

|

|

|

|

20 |

бит |

|

|

||

Рис. 4. Формирование физического адреса

Наличие сегментных регистров обеспечивает следующие преимущества: