Цифровые устройства и микропроцессоры

.pdf50

же в стек записываются значения регистра флагов F и сбрасываются флаги IF и TF. Обычно пользовательский резерв начинается с вектора № 32.

Однобайтная команда INT, отличающаяся от двухбайтной одним битом, не требует специального указания уровня прерывания. Она автоматически воспринимается процессором как прерывание третьего уровня (type 3), и используется в программах для организации контрольной точки.

Однобайтная команда INTO вызывает переход на обслуживание прерывания четвёртого уровня, связанного с переполнением, когда значение флага переполнения OF = 1. Команда INTO обычно используется после арифметических команд над числами со знаком.

4.3.7. Команды управления процессором

Существует три типа команд управления процессором: команды работы с флагами, установки МП в особые состояния и синхронизации с сопроцессором.

Команды операций с флагами. Эти команды включают семь мнемоко-

дов:

−STC – установка флага переноса CF;

−CMC – инвертирование флага переноса;

−CLC – сброс флага переноса;

−STD – установка флага направления передачи DF;

−CLD – сброс флага направления DF;

−STI – установка флага разрешения передачи;

−CLI – сброс флага разрешения прерывания.

Назначение этих команд очевидно и комментарий не требует.

Команды установки микропроцессора в особые состояния. Это коман-

ды HLT (останов) и WAIT (ожидание). По той и другой команде процессор начинает отсчитывать такты ожидания TW, которые прекращаются при определённых внешних воздействиях. Из команды останова HLT процессор может быть выведен двумя способами: подачей начального сброса RESET или внешним прерыванием, что широко используется при организации прерываний. В первом случае процессор перейдёт к выполнению основной программы сначала, во втором – к выполнению подпрограммы обслуживания прерывания. После выполнения подпрограммы процессор обязан перейти к следующей за командой HLT команде, следовательно, при необходимости возвращения к команде останова в подпрограмме необходимо поставить команду JMP с указанием адреса команды HLT.

При выполнении команды WAIT процессор аппаратно проверяет вход TEST, когда процессор обнаружит на этом входе сигнал нулевого уровня, состояние ожидания прекращается. Управление ожиданием с помощью тандема WAIT–TEST позволяет осуществить синхронизацию, т.е. сопряжение во

51

времени работы процессора с внешними устройствами (например, с арифметическим сопроцессором).

Другой способ вывода процессора из состояния ожидания заключается в подаче запроса прерывания по входу INT. Необходимо отметить, что по команде WAIT не происходит автоматического увеличения содержимого указателя команд IP, поэтому после выполнения программы обслуживания прерывания процессор вновь перейдёт к выполнению команды WAIT, т.е. перейдёт в состояние ожидания. Таким образом можно выполнять прерывающие программы во время ожидания сигнала готовности TEST от ВУ.

Команды синхронизации с арифметическим сопроцессором. Для орга-

низации совместной работы основного процессора с сопроцессором служит команда ESC. Более подробно эта команда будет рассмотрена при изучении арифметического сопроцессора.

Лекция № 9

4.4.Основные составляющие ассемблерных программ

4.4.1.Определение сегментов и групп

Основные составляющие ассемблерных программ подробно рассмотрены в пособии к циклу лабораторных работ.

Любая программа должна обязательно состоять из сегментов, без сегментов программ не бывает. Обычно в программе задаются три сегмента: команд, данных и стека, при необходимости организуют дополнительный сегмент. Сегменты могут быть самостоятельными блоками памяти или объединяться в зависимости от используемой модели памяти (модели памяти рассматриваются в учебном пособии по циклу лабораторных работ).

Большинство программ на языке ассемблера можно разделить на пять основных частей со следующими условными названиями: заголовок, макро-

определения, данные, тело программы и заключение. Заголовок

Любая программа начинается с заголовка. В нём содержатся команды и директивы, которые не приводят к созданию машинного кода при трансляции, но помогают при генерации исполняемого файла.

Макроопределения, директивы

После заголовка следуют различные описания переменных и констант. Для описания пользуются некоторыми директивами (псевдооператорами). Директивы управляют работой программы – ассемблера, а не микропроцессора. С помощью директив можно определять сегменты и подпрограммы (процедуры), давать имена командам и данным, резервировать области памяти и выполнять другие важные задачи. В отличие от команд языка ассемблера большинство директив не генерирует объектный код. В ассемблере константы часто называют макроопределениями, использующими директиву EQU, которая связывает значение с определённым именем (идентификато-

52

ром), вместо которого Turbo Assembler подставит указанное значение. Для числовых значений, кроме директивы EQU, можно использовать знак равенства (=).

Использование имён позволяет обращаться по именам к выражениям, что упрощает программу для чтения и отладки. Ниже приводится несколько примеров макроопределений, которые могут следовать за заголовком.

Count |

EQU |

6 |

Tent |

= |

Met + Count |

Существует несколько правил, которые надо помнить при создании макроопределений в языке ассемблера.

•После описания имени константы с помощью директивы EQU нельзя изменять его значение.

•Это ограничение не распространяется на имена – идентификаторы, описанные с помощью знака равенства (=), – можно свободно изменять их значения. Это позволяется сделать в любом месте программы.

•EQU может описывать все типы равенств, включая числа, выражения и символьные строки. Знак равенства может описывать только числа либо арифметические выражения типа приведённого Met + Count.

•Имена-идентификаторы не являются переменными – ни они, ни их значения не содержатся в сегменте данных. Команды ассемблера не могут изменять их значения независимо от того, были они описаны с помощью директивы EQU или (=).

•Предпочтительнее располагать макроопределения в начале программы. Выражения, описанные с помощью EQU, вычисляются, когда соответствующее имя используется программой. Выражения, описанные через знак равенства (=), вычисляются непосредственно в месте определения.

Процедуры

Процедурой в ассемблере является всё то, что в других языках называют подпрограммами, функциями и т.д. Ассемблер не накладывает на процедуры никаких ограничений – на любой адрес программы можно передать управление командой CALL, и оно вернётся к вызвавшей процедуре, как только встретится команда RET. Такая свобода выражения легко может приводить к трудно читаемым программам, и в язык ассемблера были включены директивы логического оформления процедур.

Данные

Описание сегмента данных в программе можно расположить между макроопределениями и кодовым сегментом, в котором находятся команды программы, но допускается его размещение и в другом месте программы.

Сегмент данных программы должен начинаться с директивы SEGMENT, перед которой ставится имя, а после директивы можно поставить параметры. Директива даёт указание ассемблеру разместить в памяти переменные, указанные в этом сегменте. Сегмент данных может содержать два типа

53

переменных: инициализированных (т.е. определённых) и неинициализированных, т.е. не имеющих определённых значений перед запуском программы. Для неинициализированных переменных на месте определяющей память константы используют знак вопроса (?), при необходимости получения большего неинициализированного пространства знак вопроса ставится в скобках на месте DUP-выражений, что является полезным для создания больших буферов, например:

Big |

db |

8000 DUP (?) |

; 8000-байтовый буфер |

Когда DOS загрузит вашу программу, в памяти создастся 8000байтовый буфер, в котором будут находиться какие-то прежние значения. Рекомендуется все неинициализированные значения ставить в сегменте данных последними.

Для инициализации переменных чаще всего используются три директивы: DB (определить байт), DW (определить слово), DD (определить двойное слово). Для инициализации данных операнд должен быть константой, выражением, вычисление которого даёт константу, или цепочкой. Указанные директивы применяются для размещения конкретных данных в ячейках или просто для резервирования пространства без инициализации.

Операторы инициализации и резервирования данных имеют следующий формат:

Переменная Мнемоника Операнд...,Операнд ; Комментарий

Здесь переменная не обязательна, но при её наличии ей назначается смещение первого байта, резервируемого директивой. Переменная должна заканчиваться пробелом (в отличие от метки, которая должна заканчиваться двоеточием.)

Например, директивы

D-BYTE |

DB |

104,10H |

D-WORD |

DW |

100, 100Н, –5 |

D-ABC |

DB |

0,?,?,10 |

Вероятно, вы обратили внимание, что числа в программе могут быть записаны в любой системе счисления, но в памяти число будет только в двоичном коде.

Тело программы

Кодовый сегмент содержит вашу исполняемую программу, которая имеет четыре колонки: метки, мнемоника, операнды и комментарии. Начи-

нается сегмент также с директивы SEGMENT, перед которой ставится имя. Оно может быть любым, но удобнее использовать именно слово CODE. Метки помечают места в программе, на которые могут ссылаться другие команды и директивы. В кодовом сегменте метка всегда заканчивается двоеточием (:), в сегменте данных двоеточие не используется. Во второй колонке содержатся мнемоники, т.е. машинные команды. Третья колонка содержит

54

операнды, которые обрабатываются мнемоническими командами. Некоторые команды не требуют операндов. Четвёртая колонка используется для комментариев. Из перечисленных колонок обязательной является только вторая (мнемоника команды). Перед комментариями обязательно ставится точка с запятой. Многие программисты начинают свои программы многострочными пояснительными комментариями.

После строчки с директивой SEGMENT идёт строчка с первой командой, начинающейся с метки, которая определяет точку входа в программу. Завершается программа директивой END с именем метки, определяющей точку входа.

5. РЕАЛИЗАЦИЯ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ НА БАЗЕ 16РАЗРЯДНЫХ МИКРОПРОЦЕССОРОВ

5.1.Функционирование микропроцессора

5.1.1.Способы обмена информацией в микропроцессорной системе. Формирование системных управляющих сигналов в минимальном и максимальном режимах, совмещённая и раздельная адресации

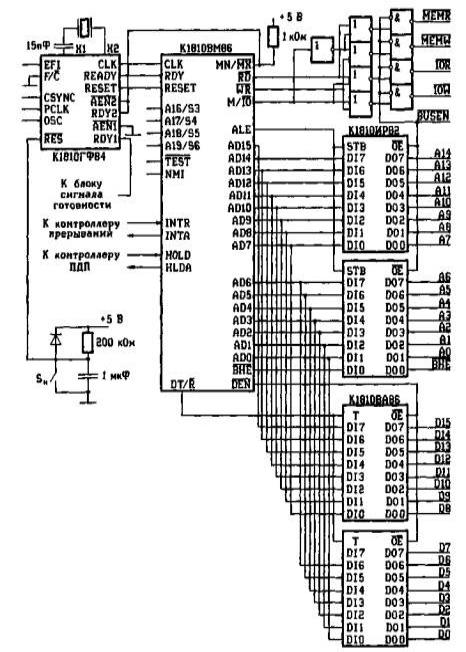

При обмене информацией микропроцессора, работающего в минимальном режиме, с памятью и внешними устройствами используют один из двух вариантов: совмещённую или раздельную адресацию. Это выражается в разных способах формирования системных управляющих сигналов для блоков памяти и внешних усройств. Задача может быть решена с помощью комбинационных логических схем, которые формируют требуемые управляющие сигналы на основе сигналов RD, WR и М/IO, вырабатываемых МП. Если в системе используется адресное пространство ввода – вывода, изолированное от пространства памяти (раздельная адресация), то целесообразно сформировать сигналы MEMR, MEMW, IOR, IOW. Эти сигналы управляют запоминающими и внешними устройствами отдельно, независимо от информации на ША, тем самым увеличивается адресное пространство памяти и внешних устройств. Обращаться к внешним устройствам в этом случае нужно только с помощью команд IN или OUT. Роль формирователей сигналов могут выполнять элементы ИЛИ-НЕ (рис. 11) или дешифратор на три входа (например, К155ИД7).

Если же в МПС ввод – вывод организован с отображением на память (совмещённая адресация), то сигнал М/IO не используется, и на ЗУ, и ВУ подаются сигналы RD и WR после усиления. Преимущество такого способа подключения ВУ в том, что появляется возможность использования большого числа команд, предназначенных для обработки данных из памяти, вместо двух – команд IN и OUT .

В максимальном режиме управляющие сигналы MEMR, MEMW, IOR, IOW вырабатывает системный контроллер К1810ВГ88.

55

5.1.2. Структура и формирование системных магистралей (шин) микропроцессорной системы

При разработке структуры блока ЦП (рис. 11) возникают задачи разделения (демультиплексирования) шины адреса/данных (ШАД) и буферирования шин адреса (ША) и шин данных (ШД).

Первая задача решается с помощью ИС К1810ИР82/83, выполняющих функции адресной защелки. Так как сигнал ВНЕ формируется в том же интервале времени, что и адресные сигналы, то его также необходимо зафиксировать в защелке. Поэтому изображенные на рис. 11 два 8- битовых регистра К1810ИР82 обеспечивают запоминание 15 разрядов адреса. Для доступа к памяти максимальной емкостью 1 Мбайт необходимо подключить еще один регистр, на который подаются оставшиеся старшие разряды AD15, A19/S 6 – A16/S3.

Вторая задача решается с помощью двунаправленных 8-битовых шинных формирователей К1810ВА86/87, которые усиливают сигналы системной шины данных.

Используемые усилители и формирователи должны обеспечивать три выходных состояния, чтобы можно было организовать прямой доступ к памяти. В этом случае после перевода МП в состояние захвата эти усилители переходят в третье состояние по сигналу РМ (BUSEN), поступающему от контроллера ПДП. Если захват шин и обмен данными по ПДП не предусмотрен, то необходимость в таком переключении отпадает.

56

Рис. 11. Структурная схема ЦП на основе ВМ86

Лекция № 10

5.1.3. Минимальный режим

Минимальный и максимальный режимы отличаются по своим функциональным возможностям. Для введения минимального режима контакт MN / MX подключается к «1». Ещё раз обратимся к рис.11, на котором представлена типичная конфигурация минимального режима. Поскольку 16 младших разрядов ША мультиплексированы с ШД, адрес необходимо фиксировать в регистрах-защёлках.

57

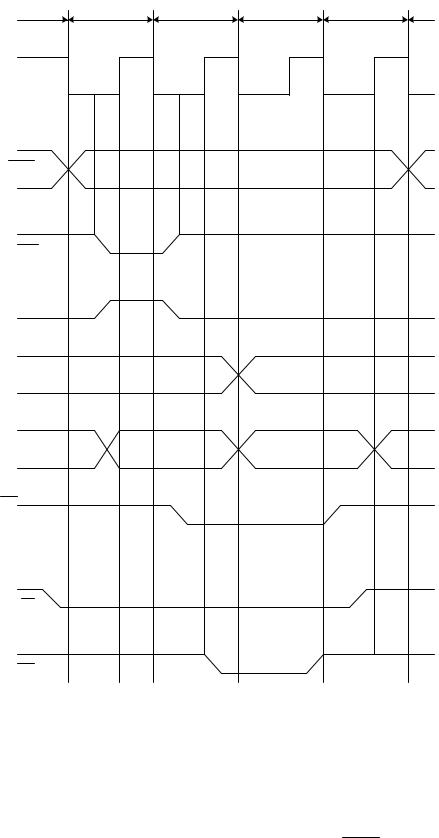

Рис. 12. Временные диаграммы последовательности чтения для min режима КР1810ВМ86

Для 8-разрядных регистра К1810ИР82 (18282), каждый из которых рассчитан на 8 бит, запоминают адреса, один из разрядов используется для фик-

сирования сигнала разрешения старшего байта шины BHE . Для доступа ко всему объему памяти (1 Мбайт) необходимо включение в систему еще одного регистра, на который следует подать пять старших адресных разрядов: АД15 и А16÷А19. Для фиксирования адреса используется сигнал STB . Вход ДЕ регистров-защелок позволяет перевести регистры в высокоимпедансное

58

состояние в режиме ПДП. В однопроцессорных системах без контроллера ПДП этот контакт заземляется.

Для управления взаимодействием с памятью и внешними устройствами

МП генерирует сигналы чтения RD , записи WR и обращения к памяти или к

ВУ M / IO . Как уже говорилось, с помощью внешней логики, показанной на

рис. 11, можно сформировать сигналы MRD,MW , IOR, IOW , позволяющие разделить адресное пространство памяти и ВУ.

В системе с несколькими интерфейсами требуются приемопередатчики на ШД. Для этого предназначаются микросхемы К1810ВА86 (18286). Каждая микросхема содержит 16 тристабильных элементов – 8 приемников и 8 передатчиков (драйверов). Следовательно, для обслуживания 8 линий ШД 18086

– две таких микросхемы.

Сигнал ДE разрешения пересылки данных подается на вход разрешения вывода ДЕ шинных формирователей К1810ВА86. Направление пересыл-

ки определяется сигналом OP / IP , поступающим от процессора на вход T (ДT/ R) приемопередатчика. Процессор переводит линии ДE и OP / IP в высокоимпедансное состояние в ответ на запрос шины по линии HLD .

Иногда системная шина проектируется так, что сигналы адреса или данных инвертируется. Поэтому микросхемы К1810ИР82 (18282) и К1810ВА86 (18286) имеют свои полные аналоги 18283 и 18287, осуществляющие инверсию сигналов при передаче со входов на выходы.

Все типы циклов по обмену информации могут быть объединены в 2 базовых цикла: чтения и записи. На рис. 12 представлены диаграммы работы микропроцессора, работающего в минимальном режиме, для машинного цикла «чтение». Машинный цикл (м. ц.) чтения начинается в такте T1с установки адресной информации и с подачи разрешения фиксации адреса STB . Адрес запишется в буферах К1810ИР82 (или ИР83).

Сигнал BHE показывает, будет ли пересылаться только младший байт

(«1») или все слово («0»). В тактах Т1 – Т4 сигнал M / IO указывает, что является источником данных – память или ВУ.

В такте T2 завершается выдача адреса, и выходы буферов A0 − A14 пере-

водятся в 3-е состояние, на линиях A16 − A19появляются сигналы ST 3...ST 6, которые сохраняются до конца Т4, начинается управляющий сигнал чтения R. Данные передаются в тактах Т3, Т4, при этом в такте Т3 адресуемое устройство выдает сигнал готовности RDУ, позволяющий синхронизировать скорость работы памяти и МП введением между Т3 и Т4 дополнительных тактов ожидания, если на входе RДУ окажется «0». Затем в такте Т4 сигнал чтения Rустанавливается в «1», тем самым выводы адресуемого устройства устанавливаются в 3-е состояние и освобождают системную ШД.

Сигнал OP / IP в Т1 – Т4 определяет сигналы формирователям ВА86 режим приема (т.е. направление), а сигнал ДЕ разрешает передачу данных в точке Т3. Чтение кода команды и данных осуществляется аналогично, отли-

59

чие в том, что данные направляются в блок регистров, а код операции в регистр очереди команд.

5.1.4. Максимальный режим

Максимальный режим используется в структурах микропроцессорных систем повышенной сложности. Он устанавливается при заземлении вывода

MN / MX . Режим характеризуется тем, что устанавливаются дополнительные управляющие сигналы, обеспечивающие совместную работу микропроцессора с другими микропроцессорами, арифметическими сопроцессорами или процессорами ввода-вывода. При установке максимального режима изменяется назначение восьми выводов микропроцессора. Еще раз акцентируем внимание на этих выводах, рассмотрев их в таблице 11.

На рис. 13 приведена типичная конфигурация максимального режима, на рис. 14 временные диаграммы работы.

На выводы ST 0, ST1, ST 2 в тактах Т1, Т2 и Т4 выводится код состояния микропроцессора, характеризующий текущий цикл и определяющий способ использования ША/ШД. Коды состояний приведены в табл. 11. За счет кодирования кодов состояния освобождается ряд выводов. Во время тактов Т3 и

TW , когда шины не используются МП, на выводах ST 0, ST1, ST 2 присутствует код 111. Код состояния позволяет выработать все необходимые управляющие сигналы при помощи внешнего средства – системного контроллера К1810ВГ88.

Выводы RQ /GTO и RQ /GT1являются двунаправленными линия-

ми, причем вывод RQ /GTO имеет более высокий приоритет. Вывод служат для захвата системной шины другими устройствами. Захват начинается с по-

ступления на один из входов RQ /GTO и RQ /GT1 запроса захвата, во время очередного такта Т1 или Т4 микропроцессор подает на этот же вывод ответственный сигнал разрешения захвата. В следующем такте микропроцессор входит в режим захвата и устанавливает шины и ряд других выводов в высокоимпедансное состояние. После окончания использования системных шин ВУ сообщает об этом микропроцессору по тем же линиям. Получив этот сигнал, микропроцессор возобновляет работу.