Цифровые устройства и микропроцессоры

.pdf

150

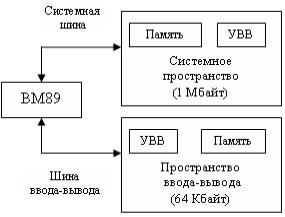

Для реализации необходимого квитирования доступа к шине одного из нескольких микропроцессоров используется арбитр шины I8289 (К1810ВБ89). Арбитр шины предотвращает доступ к системной шине контроллера шины, формирователей шины данных и регистров адреса, переводя их выходные каскады в высокоимпедансное состояние, и заставляет МП перейти в состояние ожидания установкой сигнала RDY = 0. Микропроцессор остаётся в этом состоянии до тех пор, пока арбитр не разрешит доступ к системной шине, подключив к ней контроллер шины, формирователи шины данных и регистры адреса.

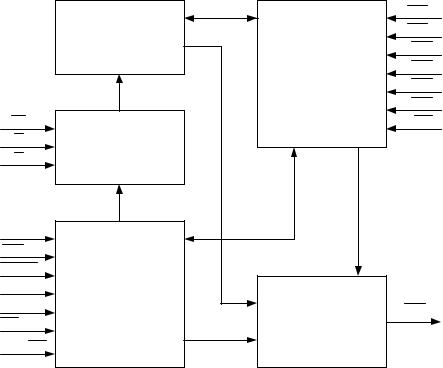

Структурная схема арбитра шины представлена на рис. 71.

Схема приоритетного арбитража

Интерфейс

Multlbus

Дешифратор

состояний

Устройство

управления

Интерфейс AEN местной шины

Рис. 71. Структурная схема арбитра шин

Рассмотрим кратко назначение узлов и основных выводов микросхемы. Дешифратор состояний, проанализировав код состояний МП, включает в работу схему приоритетного арбитража. Интерфейс местной шины формирует сигнал разрешения доступа к шине AEN для шинного интерфейса микропроцессорного модуля (контроллеру шины К1810ВГ88, регистрам-защёлкам адреса К1810ИР82/83 и шинным формирователямК1810ВА86/88). Интерфейс Multibus взаимодействует с другими арбитрами многопроцессорной системы и синхронизирует действия по захвату системной шины.

По линиям ST0, ST1, ST2 поступают сигналы состояния МП, по которым арбитр определяет для своего модуля, когда запрашивать или освобождать системную шину.

Для понимания способов учёта приоритетов ведущих шины достаточно рассмотреть следующие сигналы:

151

BREQ – запрос шины. Выходной сигнал, генерируемый арбитром для использования системной шины при параллельном способе организации приоритетов. Сигналы BREQ подаются в шифратор приоритетов, который формирует двоичный адрес активной линии BREQ с наибольшим приоритетом. Полученный адрес подаётся на дешифратор для выбора соответствующей линии BPRN, активный сигнал на которой возвращается в запрашивающий арбитр шины с наибольшим приоритетом.

BPRN – вход приоритета шины. Нулевой сигнал показывает арбитру, что он имеет приоритет над всеми другими арбитрами, запрашивающими системную шину. Этот арбитр разрешает своему МП доступ к системной шине, как только она будет доступна.

BUSY – вход / выход занятости шины. Выходной сигнал, равный нулю, выдаётся арбитром, получившем управление системной шиной. Он сообщает другим арбитрам, что системная шина занята. Для этого выводы BUSY (они имеют выходы с открытым коллектором) всех арбитров объединены в одну линию. Когда арбитр использовал шину, он снимает сигнал занятости BUSY (если на этом выходе устанавливается единица, шина доступна).

Способ последовательного учёта приоритетов реализуется путём организации приоритетной цепочки арбитров шины.

BPRO – выход приоритета шины. Данный сигнал используется при последовательном способе учёта приоритетов, когда выход BPRO некоторого арбитра подаётся на вход BPRN следующего арбитра с меньшим приоритетом. Если арбитр шины не запрашивает шину, он пропускает сигнал BPRN на выход BPRO.

Способ циклического учёта приоритетов аналогичен способу параллельного анализа приоритетов, но приоритеты арбитров периодически переназначаются.

CBRQ – вход/выход общего запроса шины.

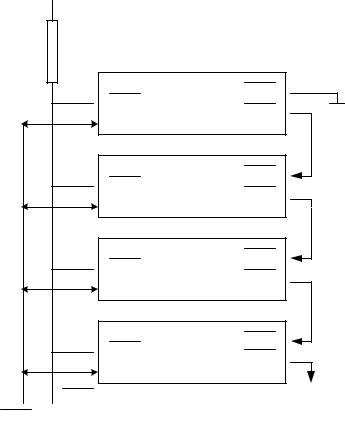

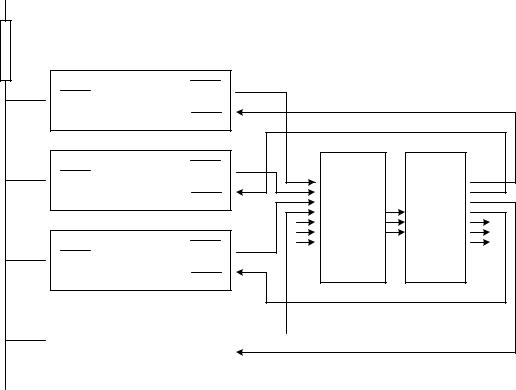

Из рассмотренных способов учёта приоритетов предпочтение обычно отдаётся первому, так как он допускает использование большего числа арбитров шины и не требует сложных дополнительных схем. На рис. 72 и рис. 73 представлены структурные схема арбитража с последовательным и параллельным учётом приоритетов.

Следует акцентировать внимание ещё на два выбора арбитра: IOB и RESB. Эти два входа подключаются к постоянным уровням, показывая, какими ресурсами обладают отдельные модули. Сигнал на входе IOB, равный нулю, говорит о том, что в модуле есть своя периферийная шина вводавывода, часто называемая в литературе резидентной шиной ввода-вывода. Если на входе RESB установить единицу, данный модуль работает с рези

152

Рис. 72. Последовательный учёт приоритетов

дентной шиной памяти. В этом случае системная шина запрашивается или освобождается как функция входного сигнала SYSB/RESB. Четыре комбинации сигналов на этих входах позволяют получить соответствующее число конфигураций, в которых процессор может обращаться к локальным устройствам ввода-вывода и памяти:

режим работы с системной шиной (RESB=0, IOB=1);

режим работы с системной шиной памяти и резидентной шиной ввода-

вывода (RESB = 0, IOB = 0);

режим с системной шиной и резидентной шиной (RESB=1, IOB=1); режим с системной шиной памяти, резидентной шиной и резидентной

шиной ввода-вывода (RESB = 1, IOB = 0).

Для полноты картины обозначим смысл сигнала AEN. Его назначением является разрешение доступа к системной шине. Сигнал AEN = 0 переводит формирователи ША и ШД, а также тактовый генератор МП в активное состояние и позволяет ему управлять системной шиной. На рис. 19 приведён пример схемы подключения арбитра шины к резидентской шине ввода-

|

|

|

|

153 |

|

|

|

|

Арбитр шины 1 |

|

|

|

|

|

|

|

BUSY |

BREQo |

|

|

|

|

|

|

BPRN o |

|

|

|

|

||

|

|

|

|

|

|

||

|

Арбитр шины 2 |

|

|

|

|

|

|

o |

BUSY |

BREQ o |

o |

|

|

o |

|

|

o |

|

|

||||

|

|

BPRN |

o |

|

|

o |

|

|

|

|

o |

Шифратор |

|

o |

|

|

Арбитр шины 3 |

|

|

o |

приори |

Дешифра o |

|

|

|

|

o |

тор |

o |

||

|

|

|

|

o |

тетов |

|

o |

|

BUSY |

BREQ o |

o |

|

|

o |

|

o |

|

|

|

|

|||

BPRN o |

|

|

|

|

|||

|

|

|

|

|

|

||

|

Арбитр шины 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BREQ |

o |

|

|||

o |

|

BUSY |

|||||||||

|

|

||||||||||

|

|

|

|

|

o |

||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

BPRN |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 73. Параллельный учёт приоритетов

вывода, резидентская шина памяти отсутствует, так как вход RESB подсоединён к нулю.

154

УВВ, Память отображенные

на память

СШИ 1 |

|

|

|

AEN |

СШ памяти |

|

|

ST0 ST1 ST2 |

BPRN |

Внешняя |

|

ЛШ |

|

|

|

МП |

АШ |

BPRO |

схема |

приоритетного |

|||

SYSB/RESB |

|

арбитража |

|

|

|

||

IOB |

RESB |

|

|

CШИ2 |

РШ ввода-вывода |

|

|

|

|

|

|

УВВ |

Рис. 74. Схема подключения АШ к резидентной шине

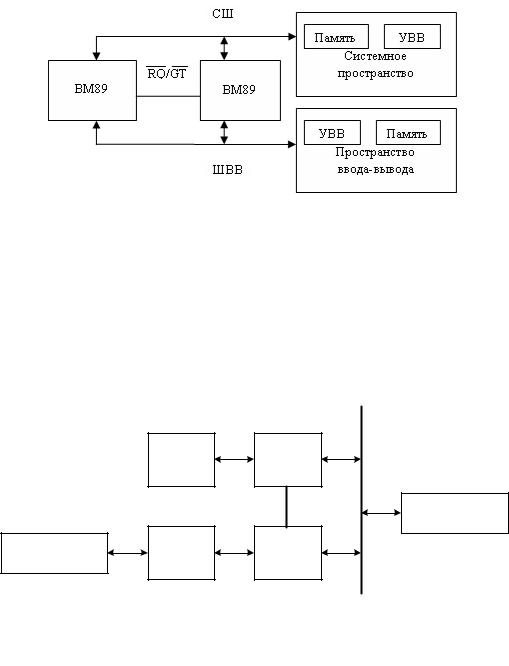

*6.2. Процессор ввода – вывода I 8089 (К1810 ВМ89)

Процессор ВМ89 имеет 40 выводов; напряжение питания – 5 В; мощность Р≥2,5 Вт; синхронизируется частотой 1-5 МГц. Кроме передач с помощью контроллеров ПДП, подготовку и саму передачу данных осуществляет ЦП, но даже в режиме ПДП центральный процессор должен подготовить контроллер и следить за завершением каждой операции ПДП.

Процессор ввода – вывода (ПВВ) 8089 специально предназначен для эффективного управления вводом – выводом, он должен выбирать и выполнять свои команды, но кроме ввода – вывода, смогут выполняться арифметические и логические операции, переходы, поиск и преобразование.

ПВВ используется совместно с ВМ86/88, он может работать параллельно с центральным процессором одновременно по двум каналам ввода – вывода, каждый из которых обеспечивает скорость передачи информации до 1,25 Мбайт/с при f=5 МГц. Центральный процессор взаимодействует с ВМ89 посредством управляющих блоков в памяти. Он готовит управляющие блоки, которые описывают подлежащую выполнению задачу, а затем направляет задачу ВМ89. ПВВ считывает управляющие блоки канальной программы, которая написана в командах ПВВ.

155

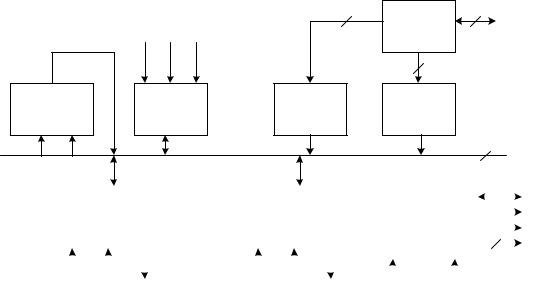

На рисунке 75 представлена структурная схема процессора ввода – выво-

да.

CA SEL RESET

Рг Рг

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RQ /GT |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOCK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BHE |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SO − |

S2 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

DRQ1 EXT1 SINTR1 |

DRQ2 EXT 2 SINTR2 |

|

|

|

|

|

|

|

READY |

|||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||

Рис. 75. Схема процессора ввода – вывода

Каждый из двух одинаковых каналов ввода – вывода содержит пять 20-ти битовых, четыре 16-ти битовых и один 4-х битовый регистр. Взаимодействие каналов осуществляется под управлением встроенной логики приоритетов. Контроллер имеет 16-битовую мультиплексируемую ШД и 20разрядную ША. Оба канала разделяют логику управления и АЛУ. Каждый из каналов может осуществлять высокоскоростные пересылки в режиме ПДП с одновременным преобразованием пересылаемых данных. Что значит «одновременные преобразования»? Из схемы видно, что в состав входит АЛУ, оно может:

а) осуществлять арифметические операции над 8 и 16 двоичными чис-

лами.

б) логические операции И, ИЛИ, НЕ.

в) может анализировать условия окончания передачи.

г) может с помощью регистра сборки – разборки принимать из 1- байтного источника, а передавать их в 2-байтный получатель и наоборот. Общее устройство управления УУ обеспечивает начальную установку сопроцессора. После сброса ВМ86 подготавливает в памяти блоки, позволяющие инициализировать сопроцессор и выдать ему задачи через память.

|

|

|

156 |

|

|

|

|

Таблица 26 |

|

|

|

|

|

|

S2 |

S1 |

S0 |

Сигналы состояния микропроцессора |

|

0 |

0 |

0 |

Выборка команды из адресного пространства ввода- |

|

|

|

|

вывода |

|

0 |

0 |

1 |

Чтение данных из адресного пространства ввода-вывода |

|

0 |

1 |

0 |

Запись данных в адресное пространство ввода-вывода |

|

0 |

1 |

1 |

Не используется |

|

|

|

|

|

|

1 |

0 |

0 |

Выборка команды из системного пространства адресов |

|

1 |

0 |

1 |

Чтение данных из системного пространства адресов |

|

1 |

1 |

0 |

Запись данных в системное пространство адресов |

|

1 |

1 |

1 |

Пассивное пространство |

|

|

|

|

|

|

Назначение выводов.

AD0 – AD15 – ША/ШД. Функции шины задаются сигналами состояния S0 ÷S2. А16/S3, А17/S4, А18/S5, А19/S6 – четыре старших разряда адреса и сигналов состояния.

Сигналы адресов формируются в течение первой части цикла шины (Т1), а затем работают сигналы состояний.

S6=S5=1 – ПДП-пересылка

S4=0 – ПДП-пересылка

S4=1 – цикл шины без ПДП

S3=0 – работает канал 1

S3=1 – работает канал 2.

После сброса эти шины находятся в третьем состоянии.

S0 ÷S2 – выходы для кодирования состояния ВМ89, назначение этих выводов приведены в таблице 26. С их помощью контроллер шины и арбитр формируют команды управления памятью и устройствами ввода – вывода. Сигналы формируются в такте Т4 передающего цикла, определяя начало нового цикла. В такте Т3 текущего цикла переходят в пассивное состояние.

ВНЕ – выходной сигнал разрешения старшего байта ШД. При сбросе и отсутствии обращений в 3-ем состоянии (может не фиксироваться в регистре адреса, т.к. не мультиплексирован с другим сигналом).

LOCK – выходной сигнал, говорящий о занятости системной шины в многопроцессорных системах. Подается на аналогичный вход арбитра шины, запрещая доступ к шине другим процессорам. Сигнал формируется или командой TSL, или установкой соответствующего разряда регистра управления.

RQ/GT –вход-выход сигнала, запрос-предоставление шин. Сигнал необходим для арбитража шины между сопроцессором и процессором или между двумя сопроцессорами.

CLK – вход тактовых импульсов (с ГФ84)

157

READY –входной сигнал готовности о возможности пересылки данных (синхронизируется через ГФ84)

CA – входной сигнал запроса готовности канала. Используется при инициализации СПВВ и при определении задания каналами. Также по срезу этого сигнала опрашивается состояние входа SEL. Этот сигнал можно назвать сигналом внимания для СП.

SEL – входной сигнал выбора канала. По первому после сброса сигналу СА определяется, ведущий или ведомый данный сопроцессор и далее запускается последовательность инициализации. Следующим сигналом СА сигнал SEL определяет номер канала (1 или 2),которому поступит сообщение от ЦП. На вход SEL обычно подключается линия адреса А0.

RESET – начальная установка, переводящая СП в пассивное состояние до получения сигнала запроса готовности канала.

DRQ1, DRQ2 – входы запросов ПДП от внешних устройств (для 1 или 2 канала).

EXT1, EXT2 – входящие сигналы окончания прямого доступа, если канал запрограммирован на окончание по внешнему сигналу.

SINTR1, SINTR2 – выходные сигналы запросов прерывания для МП.

Размещение СПВВ в адресном пространстве.

СПВВ может работать в сильно связанной (локальной) конфигурации или в слабо связанной (дистанционной, удалённой) конфигурации.

СПВВ может обращаться к памяти и ВУ, размещёнными в системном пространстве ёмкостью 1 Мбайт или в пространстве ввода/вывода ёмкостью

64 Кбайт (рис. 76).

Рис.76. Два пространства адресов процессоров ввода-вывода

Различие между этими двумя шинами состоит в том, что СШ управляется сигналами: чтения и записи в память, то есть УВВ входит в адресное пространство памяти, а ШВВ – сигналами чтения и записи внешних устройств.

158

Рис. 77. Использование СШ и ШВВ в местной конфигурации

Таким образом, устройства ввода-вывода, размещённые в системном пространстве, оказываются отображёнными на память (реагируют на 20-битовые адреса, закреплённые за ними по командам чтения и записи в память), а память, размещённая в пространстве ввода-вывода, – отображённой на внешние устройства( адресуемой 16-битовыми адресами и реагирующей на команды чтения и записи во внешние устройства).

Рис.78. Использование СШ и ШВВ в удалённой конфигурации

Рассмотренные СШ и ШВВ работают по-разному в зависимости от конфигурации, в которой используется СПВВ.

Структура СПВВ и его функционирование.

Оба канала сопроцессора (рис. 75) программируются и работают независимо друг от друга, но имеют общую логику управления и АЛУ.

Процессор может выполнять передачи ПДП со множеством вариантов. Направления могут быть: память-память, память-ввод/вывод, ввод/вывод-память, ввод/вывод-ввод/вывод.

Если данные передаются из 8-битного источника в 16-битный получатель, процессор «собирает» их в одно 16-битовое слово и передаёт на шину за один цикл, увеличивая скорость передачи. Или обратная ситуация, этим занимаются регистры сборки-разборки.

159

Кроме того, между циклами считывания и запоминания в процессоре можно сравнить или преобразовать данные с помощью АЛУ и регистров.

Операцию ПДП можно окончить по внешнему запросу, по соответствию или несоответствию при маскированном сравнении или же при достижении счётчиком нуля. Такие варианты работы определяются содержимым регистра управления канала СС.

Как уже говорилось выше, для того, чтобы СПВВ мог начать работать, он должен быть инициализирован. Для этого ЦП готовит необходимое сообщение в память, чтобы произвести начальную инициализацию, а затем выдаёт команды каналам.

Сообщение для СПВВ формируется ЦП в виде четырёх блоков.

В этих блоках сообщается физическая ширина системной шины, ширина использования шины ввода/вывода, начальный адрес программы канала и видимая служебная информация.

Названия этих блоков:

-блоки параметров (2);

-управляющие блоки (2);

-блок системной конфигурации;

-блок указателя системной конфигурации.

Итак, инициализация ПВВ готовится ЦП и записывается в память. Запускается инициализация путём выдачи сигнала СА. Сигнал по линии СА заставляет ПВВ выполнять следующее:

1.из фиксированной ячейки FFFF6h ввести слово BUSY, определяющее ширину системной шины;

2.загрузить адрес блока системной конфигурации SCB из ячеек FFFF8h и

FFFFAh;

3.ввести слово, определяющее режим и ширину шины ввода/вывода

(SOC);

4.загрузить адрес управляющего блока (из SCB+2 и SCB+4) в регистр ССР;

5.установить BUSY в CВ+1 на 00 (ширина шины – 8 б.) ;

6.!ожидать от ЦП следующего сигнала СА, инициирующего выполнение задачи.

Если в системе несколько ПВВ, то ЦП инициализирует их по очереди. Затем идёт инициализация отдельных каналов, следующим будет сигнал СА.

Сигнал СА появляется в принципе при выполнении любой команды, связанной с выставлением адреса, обычно это команда OUT. Следующий сигнал СА заставляет СПВВ анализировать сигнал SEL, если SEL=0 , значит 16-разрядная системная шина, если SEL=1, то 8-разрядная. Затем декодируется управляющее слово и начинает выполняться действие в соответствии с кодами полей этого слова.

Использование СПВВ в местной (сильно связанной) и удалённой (слабо связанной) конфигурации.

В сильно связанной конфигурации ЦП и ПВВ совместно используют общую шину, при этом ПВВ – ведомый. ПВВ запрашивает шину по линииRQ /GT . Когда