Агаханян Електронные устройства в медицинских приборах 2010

.pdfТриггер на микросхемах ТТЛ не может работать в счетном режиме, так как он не содержит элементов, способных запоминать его предыдущее состояние.

5.4.Триггеры на переключателях тока

собъединенными эмиттерами

Триггеры на переключателях тока обладают наибольшим быстродействием, что связано с заметным увеличением потребляемой мощности. Чтобы уменьшить потребляемую мощность, такие триггеры строят на возможно меньшем числе элементов, стремясь упростить их схему различными средствами.

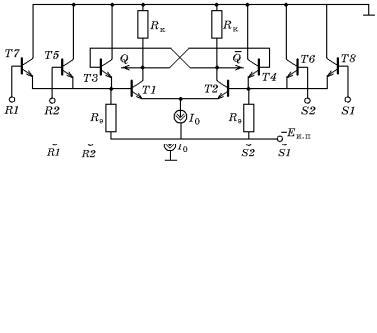

На рис. 5.12 показаны схемы триггеров, первый из которых построен на элементах ЭСЛ, а второй – на элементах ЭЭСЛ. Основу триггера составляет переключатель тока на транзисторах Т1 и Т2, охваченных перекрестными обратными связями. В обеих схемах эти связи реализуются через повторители напряжения на Т3 и Т4. Однако в триггере на рис. 5.12, а повторители являются выходными элементами, а в триггере на рис. 5.12, б – входными.

Логические элементы, на основе которых построены данные триггеры, отличаются от стандартных микросхем тем, что они не содержат транзистора с опорным напряжением. Роль этого элемента в триггере выполняет транзистор Т2 для T1 и, наоборот, Т1 для Т2, образуя переключатель тока. Поэтому расчетные соотношения, полученные в п. 2.6 для стандартных микросхем на переключателях тока, применимы и для рассматриваемых схем.

В схемах, приведенных на рис. 5.12, запись информации в триггер производится через входные транзисторы Т5, T7 и Т6, T8. При запирании этих транзисторов собственно триггер отключается от своих входных цепей, оставаясь в одном из устойчивых состояний благодаря взаимодействию между двумя частями переключателя тока, обеспечиваемому перекрестными связями. Переброс триггера происходит при отпирании входного транзистора, связанного с закрытой частью переключателя тока.

Допустим, в исходном состоянии транзистор Т1 открыт, а T2 закрыт. В момент времени t0 на вход S1 подается перепад напряже-

281

ния, соответствующий логической 1 (входные транзисторы T5–T7 остаются в закрытом состоянии).

а

б

Рис. 5.12. Схемы триггеров на переключателях тока, построенных на элементах ЭСЛ (а) и на элементах ЭЭСЛ с эмитерными повторителями на входе (б)

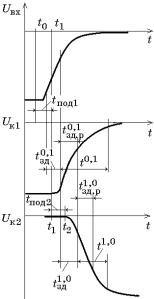

Проследим за переходными процессами, происходящими в триггерах на элементах ЭСЛ и ЭЭСЛ при работе в спусковом режиме. Эти процессы иллюстрируются эпюрами, которые приведены на рис. 5.13. Хотя эти эпюры построены для триггера на элементах ЭЭСЛ (рис. 5.12,б), ими можно пользоваться и для пояснения переходного процесса в триггере на элементах ЭСЛ (рис. 5.12,а).

На первом этапе стадии подготовки длительностью

tпод1 ≈ tзд0 + τln [ Uлог /(Uвых1 – Uвх.и)]

282

в триггере почти не происходит каких- |

|

||

либо изменений. И только когда в мо- |

|

||

мент времени t1 потенциал на входе S1 |

|

||

достигает уровня Uвх.и, часть тока I0 от- |

|

||

ветвляется в эмиттер транзистора T8 и |

|

||

начинается переброс триггера. Из-за |

|

||

уменьшения тока эмиттера Т1 повыша- |

|

||

ется потенциал на выходе Q, постепенно |

|

||

подготавливается отпирание транзистора |

|

||

Т2, который является частью переключа- |

|

||

теля тока. Во время второго этапа дли- |

|

||

тельностью tпод2 ≈ tпод1 потенциал на вы- |

|

||

ходе Q достигает уровня Uвх.и, отпирает- |

|

||

ся Т2 и заканчивается стадия подготов- |

|

||

ки. Если к этому моменту времени t2 (на |

|

||

рис. 5.13) |

транзистор Т1 остается в от- |

|

|

крытом состоянии, то в триггере возоб- |

Рис. 5.13. Эпюры напряжений |

||

новляется |

действие положительной об- |

||

ратной связи и начинается стадия реге- |

во время переходного |

||

процесса при перебросе |

|||

нерации. Однако какая стадия последует |

|||

триггера на переключателях |

|||

– регенерации или восстановления – за- |

тока |

||

висит от того, успеет ли запереться Т1 до отпирания Т2. Транзистор Т1 запирается за время

tзап ≈ tз0 + τln [ Uлог /(Uвых1 – Uвх.н)],

в течение которого импульс на входе S1 нарастает до уровня Uвх.н. Тогда I0 почти полностью ответвляется в эмиттер Т8, отключая тем самым Т1. Если tзап < tпод1 + tпод2, то стадия регенерации вообще не наступает. На основании представленных соотношений можно по-

казать, что если ширина активной области Uвх.ак = Uвх.н – Uвх.и |

не |

превышает третью часть размаха логического сигнала Uлог |

= |

=Uвых1 –Uвых0 , то транзистор Т1 закрывается до того, как отпирается

Т2. Так как в практических ИМС это условие, как правило, выполняется, то регенеративный процесс либо вообще не наступает, либо его действие почти не сказывается.

283

Переброс триггера завершается на стадии восстановления, которая начинается при запирании Т1.

При записи информации в триггер задержки рассчитывают по формулам

tзд0,1.р.тр = tзд0,1.р ≈ t1,0зд.пер ; t1,0зд.р.тр = tзд0,1.р + t1,0зд.р ≈ 2 t1,0зд.пер .

Быстродействие триггера характеризуется его временем переброса, определяемым соотношением

Тпер ≈ tзд0,1 + t1,0зд + t1,0 = 2 t1,0зд.пер + t1,0 ≈

≈2[tзд0 + τln ( Uлог /Uпом1 ) + 1,1τ].

Втактируемых системах триггер на переключателях тока, как правило, строят на двухступенчатых логических элементах [1]. При этом наличие дополнительной ступени переключателя тока позволяет сравнительно просто решать проблему включения и отключения собственно триггера от схемы управления.

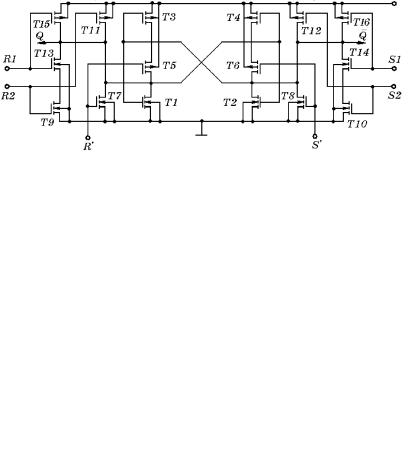

5.5.Триггеры на МДП-транзисторах

На рис. 5.14 приведены схемы триггеров, состоящих из двух логических элементов на МДП-транзисторах с одноименной проводимостью (см. § 2.7). Собственно триггер образуется путем охвата перекрестными связями инверторов на транзисторах Т1 и Т2 с квазилинейными резисторами Т3 и Т4 в стоковых цепях. На практике используется также триггер с нелинейными резисторами, отличающийся от рассматриваемого триггера тем, что в нем затворы нагрузочных транзисторов Т3 и Т4 подключаются к общему источнику питания Еи.п. Это позволяет исключить источник смещения

Ез, однако ценой уменьшения Uвых1 .

К выходам Q' и Q ′ собственно триггера подключаются усили-

тели мощности. В схеме на рис. 5.14,a эти усилители построены на сильноточных транзисторах Т5, Т7 и Т6, Т8, предназначенных для ускорения разряда и заряда паразитных емкостей нагрузки. Так как

собственно триггер имеет прямой Q′ и инверсный Q ′ выходы, то для раскачки усилителей мощности не требуется дополнительных

284

инверторов. Поэтому в триггере на рис. 5.14,а каждый из усилителей мощности построен на двух транзисторах (Т5, T7 и Т6, Т8) вместо четырех.

а

б

Рис. 5.14. Триггеры на МДП-транзисторах с инвертирующим (а) и бутстрепным (б) выходными усилителями мощности

Благодаря наличию двух выходов отпадает также необходимость подключения к каждому логическому элементу двух усилителей мощности: инвертирующего и неинвертирующего. Это еще больше упрощает схему элементов, образующих триггер, по сравнению со стандартными микросхемами.

Для записи информации используются входы логических элементов. В асинхронных триггерах можно ограничиться элементами ИЛИ-НЕ, подавая информацию на входы S' и R'. В тактируемых системах входы элементов ИЛИ-НЕ обычно используются для

285

предварительной установки 1 или 0 (входы S' и R' на рис. 5.14). Для переброса триггера в процессе его работы спусковые импульсы целесообразно подавать на входы И, так как это дает возможность записать информацию на входах, не опасаясь нарушения работы триггера. Так, установив на входах R1 и S1 низкий потенциал, запирающий транзисторы T13 и Т14, можно подать на входы R2 и S2 напряжение, соответствующее последующему такту. Только при поступлении тактового импульса на входы S1 и R1 код, установленный на входах, будет записан в триггере.

Условия (5.2) и (5.3) для схем, приведенных на рис. 5.14, выполняются с запасом, определяемым помехоустойчивостью инверторов на Т1 и T2:

|

Uпом1 = Uвых1 |

.ин– Uвх.гр; Uпом0 = Uвх.от – Uвых0 |

.ин, |

||

где Uвых1 |

.ин ≈ Еи.п и Uвых0 |

.ин — выходные потенциалы инверторов |

|||

T1 и T2, образующих триггер. В схеме с нелинейным резистором |

|||||

|

Uвых1 |

.ин = (Еи.п – Uзи.пор) /(1 + η). |

|

||

Выходные потенциалы триггера отличаются от указанных величин из-за влияния усилителя мощности. Для триггера на рис. 5.14,а они определяются соотношениями

Uвых1 ≈ (Еи.п – Uзи.пор) /(1 + η); Uвых0 ≈ 0.

Понижение выходного потенциала Uвых1 и в особенности его за-

висимость от порогового напряжения транзистора Т5 или Т6 являются серьезными недостатками обычного усилителя мощности. Выходной потенциал Uвых1 можно зафиксировать на уровне, близ-

ком Еи.п, применяя на выходах триггера бутстрепный усилитель мощности (см. рис. 5.14,б).

Нагрузочная способность триггера на МДП-транзисторах лимитируется требуемым быстродействием, определяемым продолжительностью переходного процесса при его перебросе [1].

Лучшими характеристиками обладает триггер, состоящий из логических микросхем на комплементарных МДП-транзисторах. Схема такого триггера показана на рис. 5.15. Собственно триггер построен на инверторах, образуемых из комплементарных пар Т1,

286

Т3 и Т2, Т4, охваченных перекрестными связями. В асинхронных системах переброс триггера можно осуществить путем подачи сигналов на входы R' и S', связанные с затворами транзисторов T5, T7 и Т6, Т8, которые вместе с инверторами на Т1, Т3 и Т2, Т4 образуют элемент ИЛИ-НЕ.

Рис. 5.15. Триггер на комплементарных парах МДП-транзисторов

В тактируемых системах обычно входы R' и S' используются для предварительной установки триггера в требуемое состояние. Переброс триггера при его работе удобно осуществлять через входы R1, R2 и S1, S2, которые связаны с элементами И-НЕ, состоящими из транзисторов Т9, Т11, T13, Т15 и T10, T12, Т14, Т16. Подключив к входам R1 и S1 выход генератора тактовых импульсов, во время паузы можно устанавливать соответствующие потенциалы на входах R2 и S2 без нарушения устойчивого состояния триггера. Это состояние триггера будет изменяться только после поступления тактового импульса, деблокирующего элементы И-НЕ по входам R1 и S2.

Помехоустойчивость триггера на комплементарных парах, как и у соот-

Рис. 5.16. Эпюры напряжений, иллюстрирующие переходный процесс в триггере на комплементарных парах МДП-транзисторов

287

ветствующих логических элементов (см. §2.7), определяется пороговыми напряжениями транзисторов:

Uпом1 ≈ Uзи.пор р; Uпом0 ≈ Uзи.пор п.

Помехоустойчивостью определяется запас, с которым выполняются неравенства (5.2) и (5.3).

Триггер на комплементарных парах обладает также более высоким быстродействием. Эпюры напряжений, описывающие переходный процесс в таком триггере при работе в спусковом режиме, показаны на рис. 5.16. В исходном состоянии транзисторы Т1, Т4 закрыты, a Т2, Т3 открыты по цепям затворов. Входы R', R1 и S', S1 заблокированы низким потенциалом на затворах транзисторов T7, Т8, Т13 и Т14 с п-каналами. При этом транзисторы Т5 и Т6 остаются открытыми и тем самым не препятствуют установлению соответствующего состояния в триггере.

При подаче спускового сигнала Uвх на вход R' или одновременно на входы R1 и R2 начинается первый этап стадии подготовки, который заканчивается, когда входной сигнал достигает порогово-

го напряжения Uзи.пор п транзистора Т7 (или Т9 и Т13). На втором этапе происходит спад напряжения Uвых1 на стоке транзистора Т1 и,

соответственно, на затворах транзисторов Т2 и Т4. Когда потенциал затвора Т4 достигает уровня Uзи.пор р, транзистор Т4 отпирается, и заканчивается второй этап стадии подготовки. После этого начинается нарастание потенциала Uвых2 на стоке Т2 и затворах Т1 и T3. Стадия подготовки завершается, когда Uвых2 повышается до уровня Uзи.пор п и транзистор T1 отпирается. В триггере возобновляется регенеративный процесс.

Как отмечалось ранее, влияние этого процесса в практических схемах не очень существенно. На последней стадии восстановления завершается установление триггера в новое устойчивое состояние, при котором транзисторы Т2, Т3 оказываются закрытыми, a T1, T4 открытыми по цепям затворов (однако все они не проводят тока). При блокировке входной цепи отключаются также транзи-

сторы Т7, Т8 и Т13, T14 (или Т9, Т10).

Из анализа переходных процессов следует, что времена задержки передачи информации в триггере на МДП-комплементарных парах определяются соотношениями

288

t1,0зд.р.тр = t1,0зд.р ; tзд0,1.р.тр = t1,0зд.р + tзд0,1.р ,

а его быстродействие лимитируется временем переброса

Тпер = t1,0зд + tзд0,1 + t0,1.

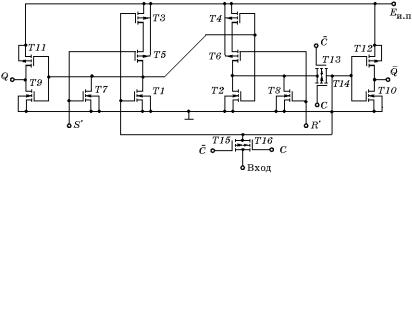

Для повышения быстродействия триггера, работающего на большую емкостную нагрузку, к его выходам обычно подключают буферные инверторы, выполняющие функции усилителей мощности. На рис. 5.17 показана схема триггера на комплементарных па-

рах, к выходам Q и Q которого подключены буферные каскады,

построенные на мощных транзисторах Т9, Т11 и T10, Т12. При использовании буферных каскадов остальные элементы триггера реализуют на маломощных транзисторах, имеющих малые размеры. Это способствует уменьшению топологических размеров триггера, так как для любой его конфигурации требуется всего четыре мощных транзистора больших размеров.

Рис. 5.17. Триггер на комплементарных парах МДП-транзисторов

сбуферными каскадами на выходах и с двунаправленными ключами

вцепи обратной связи на входе

Применение буферных каскадов позволяет формировать перепады напряжения, длительности фронта и среза которых практически не зависят от комбинации входных сигналов триггера. Эта особенность позволяет еще больше повысить быстродействие триггера, так как имеется возможность использовать внутри триггера транзисторы малых размеров, что способствует уменьшению ме-

289

жэлектродных емкостей. Благодаря этому обеспечивается более быстрое переключение собственно триггера.

В триггерах на комплементарных парах счетный режим работы обычно реализуют с помощью управляющего запуска. При этом на входе триггера, а также в цепи перекрестной обратной связи используются двунаправленные ключи, которые представляют собой параллельно соединенные комплементарные пары транзисторов, управляемые разнополярными импульсами. Схема такого триггера показана на рис. 5.17. Во время паузы тактовых импульсов двунаправленный ключ на транзисторах T15, Т16 не проводит и тем самым отключает триггер от его входа. Двунаправленный ключ на транзисторах Т13 и Т14, оставаясь в проводящем состоянии, соединяет сток транзистора T2 с затворами комплементарной пары Т1, T3 и тем самым замыкает цепь перекрестной связи. Во время действия тактового импульса двунаправленный ключ на транзисторах T15 и T16 отпирается и соединяет триггер со входом. Одновременно запирается ключ на транзисторах Т13 и Т14, и цепь перекрестной связи размыкается. При этом триггер устанавливается в состоянии, соответствующем входному потенциалу. Так, если на входе действует высокий потенциал, то это приводит к отпиранию транзистора Т1, что сопровождается понижением потенциала его стока и затворов комплементарной пары Т2 и Т4. Транзистор Т2 запирается, и потенциал на его стоке повышается. Когда прекращается тактовый импульс, ключ на транзисторах Т13 и T14 отпирается и подключает затворы транзисторов Т1 и Т3 к стоку транзистора Т2. Поэтому, когда запирается входной ключ (Т15 и Т16) и отключает триггер от входа, его состояние сохраняется, так как цепь перекрестной связи оказывается замкнутой.

5.6. Триггеры на интегральных инжекционных логических элементах

Интегральные инжекционные логические (И2Л) микросхемы являются одной из современных разработок, которые все больше и больше используются в различных устройствах цифровой автоматики и ЭВМ. Для построения микросхем И2Л используется базовая

290