Агаханян Електронные устройства в медицинских приборах 2010

.pdf

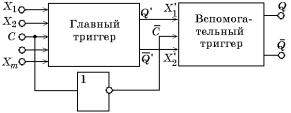

• с блокировкой входов главного триггера сигналами, поступающими от схемы управления вспомогательного триггера.

В качестве примера на рис. 5.8 показана структурная схема ТС с инвертором между главным и вспомогательным триггерами. Принцип действия этой системы заключается в следующем. При воздействии тактового импульса входная информация воспринимается главным триггером. В это время схема управления вспомогательного триггера блокируется сигналом 0, поступающим через инвертор на ее тактовый вход.

Рис. 5.8. Структурная схема MS-триггера, состоящего из главного и вспомогательного триггеров

После окончания тактового импульса, когда на входе С он заменяется сигналом 0, блокируется схема управления главного триггера. В это время под действием инвертированного тактового сигнала 1 на входе С вспомогательный триггер воспринимает информацию, записанную в главном триггере. При двух других способах связи блокировка входов соответствующего триггера осуществляется сигналами со схемы управления второго триггера.

В зависимости от логической функции, выполняемой схемой управления, различают следующие типы ТС: D, Т, Е, R, S, DV, RS, JK, RI, SI, DVI, RSI, JKI, RST, JKT, JK-J*K*, JK-J*K*T и т.д.

Наибольшее применение получили D-, Т-, RS-, JK- и DV-триггеры. RI-; SI-, RSI-, JKI-, DVI-триггеры представляют собой логические инверсии соответственно R-, S-, RS-, JK-, DV-триггеров. Следовательно, если R-, S-, RS-, JK-, DV-триггеры реализуются в позитивной логике, то эти же схемы будут представлять собой RI-, SI-, RST-, JKT-, DH-триггеры в негативной логике при перекодировании входных сигналов и, наоборот, первые из них будут инверсией

271

последних. Поэтому нет необходимости отдельно рассматривать инверсные триггеры, так как они логически равнозначны и только представлены в различных типах логики.

Следует отметить, что число возможных типов триггеров даже для одного и двух внешних входных сигналов не исчерпывается перечисленными выше видами. Далее рассматриваются ТС, получившие наибольшее распространение в интегральной схемотехнике.

Логические функции, выполняемые ТС, удобно описать при помощи таблицы истинности, отражающей изменение системы. При составлении таких таблиц следует иметь в виду, что так как триггер представляет собой запоминающее устройство, то его состояния описываются переключательными функциями от значений переменных, определяемых в предшествующие моменты времени. Именно этим отличаются таблицы истинности ТС от аналогичной таблицы для логического элемента, который характеризуется тем, что описывающие его переключательные функции зависят от значений переменных в тот же момент времени, в который определяются сами функции. Следовательно, в таблицах истинности состояние триггера в такте п + 1 будет зависеть от входного сигнала в такте п. Эти состояния будут отмечены соответственно индексами п + 1 и п. Тем самым в таблице истинности ТС отражается способность этого устройства к запоминанию.

Рассмотрим ТС для положительной логики, для которой уровень напряжения, соответствующий логической 1, более положителен, чем уровень, соответствующий логическому 0. ТС с отрицательной логикой (для которой уровень напряжения, представляющий состояние 1, менее положителен, чем уровень, представляющий состояние 0) могут быть рассмотрены как инверсия триггеров с положительной логикой.

RS-триггеры. Примером простейшей ТС является RS-триггер, который в общем случае имеет три входа, два из которых логические: вход S для установки 1 и вход R для сброса 1 (т. е. для установки 0). Третий вход (С), предназначенный для приема тактовых импульсов, не выполняет логических функций. Этот вход имеют тактируемые триггеры. Состояния RS-триггера, соответствующие различным сочетаниям сигналов на входах R и S, приведены в табл. 5.1 (н/о – состояние триггера не определено).

272

Таблица 5.1

Таблица истинности RS-триггера

Такт п |

|

Такт п+1 |

||||||

R |

|

S |

Qn+1 |

|

|

|

n+1 |

|

Q |

||||||||

0 |

|

0 |

Qn |

|

|

|

|

n |

|

|

Q |

||||||

0 |

|

1 |

1 |

0 |

||||

|

Такт п |

Такт п+1 |

||||

R |

|

S |

Qn+1 |

|

|

n+1 |

Q |

||||||

1 |

|

0 |

0 |

1 |

||

|

|

|

|

|

|

|

1 |

|

1 |

н/о |

|

н/о |

|

Особенность RS-триггера заключается в том, что при подаче одновременно на входы R и S сигнала, соответствующего логической 1, состояние на его выходе становится неопределенным: триггер начинает генерировать или во время воздействия входных сигналов неоднократно переходить из одного состояния в другое.

Очевидно, что для нормальной работы триггера необходимо исключить указанное сочетание входных сигналов, приводящее к неопределенному состоянию. Это можно осуществить, предусмотрев выполнение запрещающего условия1 RS = 0. Если на обоих входах действует сигнал, соответствующий 0, триггер сохраняет свое прежнее состояние. Таким образом, характеристическое уравнение RS-триггера при выполнении условия RS = 0 можно записать в следующем виде:

Qп+1 = [QRS RS]n или Qп+1 = [S QR]n .

JК-триггеры. Они отличаются от RS-триггеров прежде всего тем, что в них устранена неопределенность, которая возникает в RS-триггерах, когда на обоих входах одновременно действуют единичные сигналы. JК-триггер тоже имеет два логических входа: J — для установки 1 и К — для сброса 1. Тактируемые JК-триггеры имеют дополнительный вход С для приема тактовых импульсов.

Состояния JК-триггера, соответствующие различным комбинациям сигналов на входах J и К, представлены в табл. 5.2.

1 Здесь и далее обозначения входов и выходов совпадают с обозначениями соответствующих сигналов.

273

Таблица 5.2

Таблица истинности JК-триггера

|

Такт п |

|

|

|

Такт п+1 |

||||||

J |

|

K |

Qn+1 |

|

|

|

|

n+1 |

|||

Q |

|||||||||||

0 |

|

0 |

|

Qn |

|

|

|

|

|

n |

|

|

|

|

Q |

||||||||

|

|

|

|

|

|

|

0 |

||||

1 |

|

0 |

1 |

|

|||||||

0 |

|

1 |

0 |

|

1 |

||||||

1 |

|

1 |

|

|

n |

|

|

|

Qn |

||

|

Q |

|

|

|

|||||||

Таким образом, состояние JK-триггера однозначно определено при всех сочетаниях входных сигналов, в том числе и при J = 1 и

K = 1.

Характеристическое уравнение JK-триггера можно записать в виде

Qп+1 = [QJK JK QJK]n или Qп+1 = [JQ KQ]n .

JK-триггер можно получить из RS-триггера, соединив выходы триггера с его входами. Такое соединение позволяет использовать информацию, которая записана в триггере, для управления самой ТС. При этом схема управления строится таким образом, чтобы на входах S' и R' собственно триггера единичные сигналы одновременно не появлялись. Когда на обоих входах ТС действуют единичные сигналы (J = K = 1), схема управления обеспечивает работу триггера в счетном режиме: из-за связи с выхода на вход схема управления учитывает предшествующее состояние ТС и направляет сигнал на соответствующий вход собственно триггера, обеспечивая тем самым его переброс.

JK-тригтер является более универсальным по сравнению с RS- триггером, поэтому он широко применяется в микроэлектронике.

JK-триггер имеет симметричную внутреннюю структуру и удобен для построения различных узлов сложных цифровых систем. Путем незначительных изменений соединений внешних выводов JK-триггера можно получать триггеры другого типа, такие, как RS-, D-, Т-триггеры и т.д., благодаря чему сокращается число ИМС, необходимых для функциональной полноты данной серии ИМС.

274

D- и DV-триггеры. В настоящее время наряду с RS- и JK- триггерами широкое распространение получили D- и DV-триггеры. Так как основным элементом DV-триггера является D-триггер, то целесообразно прежде всего ознакомиться с его работой.

D-триггер представляет собой запоминающий элемент с одним входом и предназначен для задержки логического сигнала. Иногда D-триггер называют триггером-задержкой или триггеромзащелкой. В соответствии с назначением триггера его работа опи-

сывается характеристическим уравнением следующего вида:

Dп+1 = Dп,

которому соответствуют состояния, указанные в табл. 5.3.

Из этой таблицы следует, что состояние |

|

Таблица 5.3 |

|

D-триггера и соответствующий ему логиче- |

|

||

|

|

|

|

ский сигнал Qп+1 повторяют значение сиг- |

Таблица истинности |

||

нала, которое было установлено на входе |

D-триггера |

||

триггера в предыдущий момент времени. В |

|

|

|

асинхронных триггерах задержка определя- |

Такт п |

Такт п+1 |

|

Dn |

Qn+1 |

|

|

ется параметрами схемы, а в тактируемых – |

|

|

|

0 |

0 |

|

|

периодом следования тактовых импульсов. |

|

||

1 |

1 |

|

|

|

|

||

Ограниченные логические возможности

D-триггера привели к необходимости разработки на его основе новых типов триггеров, являющихся более универсальными. К их числу прежде всего относится DV-триггер. Этот триггер имеет два логических входа D и V, первый из которых является управляющим, а второй разрешающим. DV-триггер управляется по входу D (выполняя функции обычного D-триггера) только в том случае, когда на входе V имеется разрешающий сигнал, т.е. когда V = 1. Если на входе V действует запрещающий сигнал 0, триггер сохраняет свое состояние независимо от сигнала на входе D, т.е. он выдает ранее записанную информацию и перестает управляться по входу D.

Состояния DV-триггера, соответствующие различным сочетаниям сигналов на его входах D и V, указаны в табл. 5.4. Характеристическое уравнение, описывающее логические возможности DV-

триггера, имеет следующий вид:

Qn+1 =[QV DV ]n .

275

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 5.4 |

|||

|

|

|

Таблица истинности DV-триггера |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Такт п |

Такт п+1 |

|

Такт п |

|

Такт п+1 |

|||||||||||

D |

|

V |

Qn+1 |

|

|

|

n+1 |

D |

|

V |

|

Qn+1 |

|

|

|

n+1 |

|

Q |

|

Q |

|||||||||||||||

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

|

Qn |

|

Qn+1 |

0 |

|

1 |

|

0 |

|

1 |

||||||

1 |

|

0 |

Qn |

|

|

|

|

n |

1 |

|

1 |

|

1 |

|

0 |

||

|

|

Q |

|

|

|

||||||||||||

Как отмечалось, быстродействие триггеров и ТС определяется быстродействием образующих их логических элементов, которое характеризуется следующими динамическими параметрами:

• временами перехода из состояния логической 1 в состояние логического 0 t1,0 и, наоборот, из 0 в 1 t0,1, измеряемыми как интервал времени, в течение которого выходное напряжение изменяется от 0,9Uвыхт до 0,1Uвыхт и от 0,1Uвыхт до 0,9Uвыхт;

• временами задержки включения t1,0зд и выключения tзд0,1 , из-

меряемыми на заданных уровнях как интервал времени между входным и выходным импульсами при переходе от 1 до 0 и, наоборот, от 0 до 1;

• временами задержки распространения сигнала при включении t1,0зд.р и выключении tзд0,1.р ИМС, измеряемыми на уровне 0,5 как

интервал времени между входным и выходным импульсами при переходе от 1 в 0 и, наоборот, от 0 в 1 соответственно;

• средним временем задержки распространения сигнала tзд.р.ср, определяемым по формуле

tзд.р.ср = ( t1,0зд.р + tзд0,1.р )/2.

5.3. Триггеры на элементах ТТЛ

Как отмечалось ранее, элементы транзисторно-транзисторной логики (ТТЛ), появившиеся в результате дальнейшего усовершенствования элементов диодно-транзисторной логики (ДТЛ), обла-

276

дают бóльшим быстродействием, чем их прототипы, поэтому их часто применяют для построения быстродействующих ТС1.

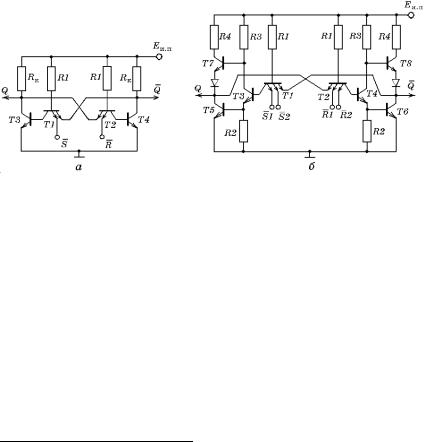

На рис. 5.9 представлены схемы триггеров на элементах ТТЛ с простым и сложным инверторами. В первой схеме (рис. 5.9,а) триггер построен на двух инверторах на Т3 и Т4, которые охвачены обратными связями через эмиттерные входы транзисторов Т1 и Т2. Во второй схеме (рис. 5.9,б) аналогичным способом обратными связями охвачены сложные инверторы на транзисторах Т3, Т5, Т7 и

Т4, Т6, T8.

Рис. 5.9. Триггеры на элементах ТТЛ с простым (а)

исложным (б) инверторами

Вэтих схемах входами триггеров служат эмиттеры транзисторов Т1 и Т2. При установлении на входах повышенного потенциала триггер отключается от входных цепей, оставаясь в одном из своих устойчивых состояний. Это состояние поддерживается перекрестными связями, соединяющими выход каждого инвертора с эмиттерным входом другого. Если, например, на выходе первого инвертора (на Т3 или Т3, Т5, Т7) устанавливается высокий потенциал

Uвых1 , то это приводит к смещению эмиттера Т2 в обратном направлении, благодаря чему на выходе второго инвертора (на Т4 или Т4, T8, Т6) устанавливается низкий потенциал. Это, в свою очередь, обеспечивает сохранение высокого потенциала на выходе первого

1В этом и в последующих разделах будут рассмотрены собственно триггеры. В случае необходимости с ТС можно ознакомиться в [1] и [8].

277

инвертора, так как ток, отбираемый от источника питания транзистором Т1 через его эмиттер, направляется к выходу второго инвертора, а не в базу Т3, поэтому последний остается закрытым.

Переброс триггеров, показанных на рис. 5.9, происходит тогда, когда потенциал на одном из входов, например на входе S, понижается. При этом ток, отбираемый многоэмиттерным транзистором (МЭТ), ответвляется в эмиттер, на который подан низкий потенциал (с входом S связан транзистор T1). Это приводит к запиранию транзистора (в данном случае Т3), присоединенного к коллектору МЭТ. Процесс завершается перебросом триггера в новое устойчивое состояние.

В асинхронных системах переброс триггера начинается, как только изменяются входные потенциалы. Использование в тактируемых устройствах триггера, образуемого элементами И-НЕ (см. рис. 5.9), часто создает трудности, поскольку такой триггер перебрасывается при обработке входной информации. Этот недостаток можно исключить, построив триггер на логических элементах И- ИЛИ-НЕ, каждый из которых имеет два входных транзистора. Один из них включают в схему триггера, а другой служит для переброса триггера после обработки входной информации, при этом во время обработки информации последний блокируется, не вызывая нарушения устойчивого состояния равновесия триггера.

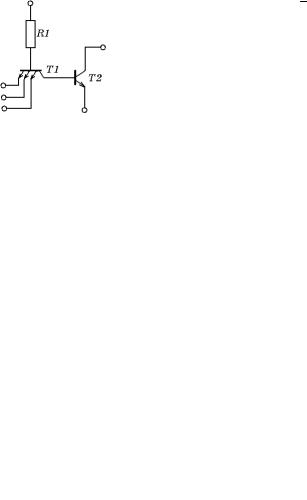

Стандартную микросхему ТТЛ, выполняющую функцию И-НЕ, можно превратить в элемент И-ИЛИ-НЕ, дополнив ее по входу расширителем (рис. 5.10).

Рис. 5.10. Схема логического расширителя, применяемого для построения элемента И-ИЛИ-НЕ на базе микросхемы ТТЛ

В микросхемах ДТЛ логический расширитель представляет собой диодную матрицу с диодами смещения на выходе. Один из этих диодов используется как разделительный элемент в парал-

278

лельной цепи диодных матриц, выполняющих функцию ИЛИ. В микросхемах ТТЛ нет диодов смещения, поэтому в качестве разделительного элемента используется транзисторный усилитель (на рис. 5.10 – Т2), подключаемый к выходу МЭТ, который является входным элементом расширителя. Транзисторный усилитель расширителя соединяется параллельно с простым инвертором микросхемы ТТЛ или с транзистором T1 в микросхеме со сложным инвертором.

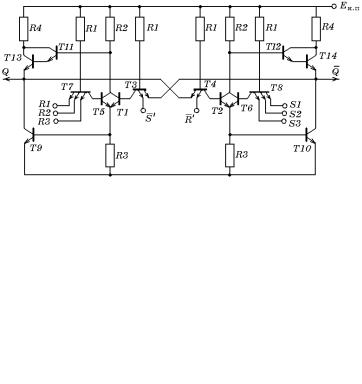

На рис. 5.11 представлены схемы триггеров, собранных на элементах И-ИЛИ-НЕ. Собственно триггер построен на инверторах, охваченных обратными связями через МЭТ Т3 и Т4, которые представляют собой входную часть логических расширителей. Допол-

нительные входы расширителя (на рис. 5.11 — S ′ и R′) часто используют для предварительной записи информации непосредственно в триггер. В последующие моменты времени на эти входы подается высокий потенциал, отключающий их от триггера.

а

б

Рис. 5.11. Триггеры на элементах ТТЛ с логическими расширителями на входах: с простым (а) и сложным (б) инверторами

279

Входная информация обрабатывается и поступает в триггер через МЭТ Т7 и T8, являющиеся элементами основных микросхем ТТЛ. Для блокировки транзисторов Т7 и T8 достаточно подать на один из входов R и S (например, R1 и S1) низкий потенциал, отпирающий соответствующий эмиттер и тем самым отключающий триггер от входной цепи. При этом можно обрабатывать информацию, поступающую на остальные входы (R2, R3 и S2, S3), изменяя потенциалы на этих входах в требуемом направлении. В течение времени блокировки состояние триггера остается неизменным. Только при подаче тактового импульса, запирающего блокированные эмиттеры, триггер переходит в новое устойчивое состояние, соответствующее установленной на входе информации.

Помехоустойчивость триггера, его нагрузочная способность определяются соответствующими выражениями, характеризующими микросхемы TTЛ [1]. Нагрузочная способность ТТЛ-триггера ограничивается паразитными емкостями, замедляющими переброс триггера, продолжительность которого определяет его быстродействие.

Времена задержки распространения сигнала в ТТЛ-триггере на элементах И-НЕ (см. рис. 5.9) определяются выражениями

tзд0,1.р.тр = tзд0,1.р ; t1,0зд.р.тр = tзд0,1.р + t1,0зд.р .

Быстродействие триггера на элементах с простым инвертором можно оценить по формуле (см. рис. 5.9,а)

Тпер = tзд0,1 + t0,1,

а в триггере со сложным инвертором (см. рис. 5.9,б) по формуле

Тпер = tзд0,1 + t1,0зд + t0,1.

Задержки при передаче информации в ТТЛ-триггере на элементах И-ИЛИ-НЕ рассчитываются по формулам

t1,0зд.р.тр = t1,0зд.р ; tзд0,1.р.тр = t1,0зд.р + tзд0,1.р ,

а быстродействие по формуле

Тпер = t1,0зд + tзд0,1 + t0,1.

Для уменьшения задержки при передаче информации, а также времени переброса триггера Тпер, характеризующего его быстродействие, применяют элементы на транзисторах Шоттки.

280