Агаханян Електронные устройства в медицинских приборах 2010

.pdf

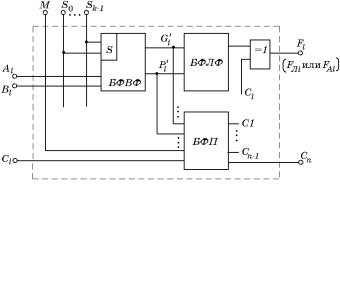

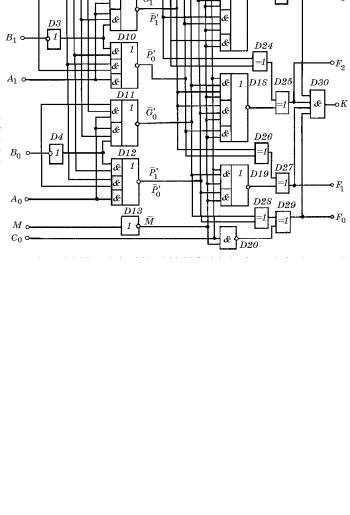

второго слагаемых и цифра переноса из соседнего младшего разряда. В результате сложения в каждом разряде получаются цифры сумм для этого разряда и цифра переноса в следующий старший разряд. Структуру АЛУ синтезируют таким образом, чтобы можно было реализовать операцию сложения с наибольшим быстродействием при минимальном числе логических элементов. Поэтому в АЛУ используются ускоренные методы формирования переноса, для чего в каждом разряде образуются вспомогательные функции Рi′ и Gi′. При этом для каждой из арифметических операций име-

ется свой набор функций Рi′ и Gi′.

При помощи АЛУ можно также организовать арифметическое умножение многоразрядных двоичных чисел. Так, при последовательном методе умножения для вычисления произведения необходимо каждый раз сдвинуть множимое на один разряд влево. При этом полученное в результате сдвига частное произведение прибавляется к результату, если соответствующий данному шагу сдвига разряд множителя равен единице. Если он равен нулю, то сложение не производится. Основным недостатком последовательного метода умножения является необходимость программного управления процессом и сравнительно низкое быстродействие.

Для сокращения затрат времени на умножение наряду с усовершенствованными программными методами используются и аппаратурные методы. Программные методы обеспечивают ускорение операция умножения за счет усложнения алгоритма управления. Аппаратурные методы ускорения связаны с использованием специальных множительных блоков. Также умножители выпускаются в виде отдельных ИМС, допускающих наращивание разрядности. Для обеспечения высокого быстродействия современных микропроцессоров в их АЛУ включают быстродействующие умножители повышенной разрядности.

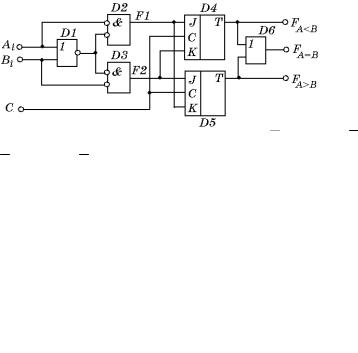

Одной из самых распространенных арифметических операций является операция сравнения двух многоразрядных чисел. Поскольку критерием равенства двух чисел А и В является совпадение их по всем разрядам, то для сравнения двух одиночных разрядов чисел А и В можно воспользоваться функцией «исключающее ИЛИ»

402

Разрядность компараторов можно увеличить последовательным или параллельным каскадированием компараторов меньшей разрядности.

В заключение рассмотрим функциональную схему стандартного АЛУ (рис. 8.15), обычно входящего в серию цифровых ИМС.

Рис. 8.15. Функциональная схема стандартного АЛУ

404

8.5. Полупроводниковые запоминающие устройства

8.5.1. Классификация и основные параметры микросхем памяти

Одним из основных функциональных узлов цифровых устройств является запоминающее устройство (ЗУ), которое предназначено для приема, хранения и выдачи информации, необходимой для работы устройства. В полупроводниковых ЗУ обычно оперируют двоичной информацией, представляемой двоичными цифрами – битами. Другой часто используемой единицей двоичной информации является байт, состоящий из 8 бит.

Требования к объему памяти ЗУ определяются назначением и структурой цифровых систем и меняются от единиц килобит (для микро-ЭВМ) до 1010 ÷ 1111 бит (для больших ЭВМ). В системах с большим объемом памяти обычно применяется иерархическая структура с тем, чтобы предотвратить снижение производительности системы, которое неизбежно при увеличении объема памяти. При иерархической структуре в систему включается несколько видов ЗУ разного объема и быстродействия. Информация, подлежащая скорой текущей переработке, заносится в быстродействующее ЗУ (иногда называемое внутренним) с относительно небольшим объемом. Основной массив информации, ожидающий обработки, хранится в ЗУ большой емкости и, соответственно, с низким быстродействием, откуда в текущий момент обработки он поступает во внутреннее ЗУ.

ЗУ можно разделить на два вида: оперативные (ОЗУ) и постоянные (ПЗУ). ОЗУ выполняют запись, хранение и считывание произвольной текущей информации, изменяющейся в процессе работы системы (например, результатов вычислений или таких программ, которые меняются). ПЗУ осуществляют хранение и выдачу постоянно записанной информации, содержание которой в ходе работы системы не изменяется (например, команды и константы).

По способу выдачи информации ЗУ подразделяются на устройства с произвольной и последовательной выборками. В ЗУ с произвольной выборкой запись или считывание информации в любой из

406

8.5.2. Оперативные запоминающие устройства

Рассмотрим основные полупроводниковые ЗУ.

Статические ОЗУ. Нa рис. 8.16 приведена структурная схема статического ОЗУ с произвольной выборкой. Оно содержит матрицу запоминающих ячеек, состоящих из п строк по т элементов в каждой, с информационной емкостью N = n×m, входные буферные каскады, дешифраторы адреса, усилители записи–считывания и схему управления.

Рис. 8.16. Структурная схема статического ОЗУ с произвольной выборкой

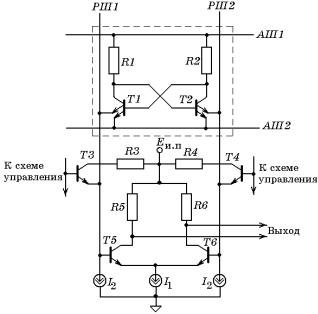

В современных ОЗУ указанные части обычно выполняются на одном кристалле в виде функционально законченных узлов. Такая организация ОЗУ называется матричной или двухкоординатной, она обеспечивает доступ отдельно к каждой из ЗЯ через адресные (AШ) и разрядные (РШ) шины, к которым подсоединены входы и выходы ЗЯ. Код адреса ячейки определяется сигналами на адресных входах X и Y, которые поступают на обслуживающие матрицу

408

сравнительно малым током хранения Iхр, что обеспечивается сравнительно низким напряжением питания, определяемым разностью потенциалов на адресных шинах AШ1 и АШ2, составляющим всего (0,2–0,3) В. В режиме хранения на разрядных шинах РШ1 и РШ2 устанавливается высокий потенциал, смещающий эмиттерные переходы транзисторов Т1 и Т2 в обратном направлении. При этом токи источников I2 протекают через эмиттерные цепи транзисторов Т3 и Т4.

Рис. 8.17. Схема запоминающей ячейки ОЗУ на элементах ТТЛ

В режиме считывания на базах транзисторов Т3 и Т4, связанных со схемой управления, поддерживается прежний потенциал. При этом под действием опрашивающих импульсов увеличивается разность потенциалов на адресных шинах АШ1 и АШ2, т.е. повышается напряжение питания триггера, что приводит к увеличению тока насыщенного транзистора T1 или Т2. Одновременно подается импульс тока I1 в эмиттеры Т5 и Т6, отпирающий усилитель считывания. Ток эмиттера насыщенного транзистора Т1 (Т2) через разряд-

410