- •Вопросы по курсу тсис для группы 2032

- •1 Вариант

- •2 Вариант:

- •23.Команда. Формат команды. Классификация команд. Особенности состава команд Intel.

- •25. Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

- •27.Автоинкрементная и автодекрементная адресация.

- •Уровни кэша

- •31.Сегментная и страничная организация доступа к памяти.

- •32.Режимы работы

- •Реальный режим (Real Mode)

- •Режим системного управления (System Management Mode)

- •Защищенный режим (Protected Mode)

- •34. Конвейеризация и векторизация обработки данных

- •37. Устройства ввода информации. Сенсорные экраны.

- •Проекционно-ёмкостные сенсорные экраны Конструкция и принцип работы

- •Особенности

- •Пятипроводной резистивный сенсорный экран.

- •Сенсорные экраны на поверхностно-акустических волнах Конструкция и принцип работы

- •Инфракрасные сенсорные экраны

- •Сенсорные экраны dst

- •Индукционные сенсорные экраны

25. Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

Под адресацией подразумевается способ, с помощью которого адресуется информация, содержащаяся в памяти. Наименьшая единица информации, к которой можно адресоваться, называется адресной единицей. Каждой адресуемой в памяти единице присваивается единственный признак - адрес. Каждая адресная единица имеет свой адрес. Адрес устанавливается для каждого места хранения информации и не зависит от содержания записей. Другими словами запоминающее устройство - это совокупность регистров определенной длины. Каждому регистру присвоен адрес. Для вызова из памяти содержимого такого регистра или записи в регистр какой-либо информации необходимо указать его адрес. Длина каждого регистра есть в этом случае наименьшая адресуемая единица информации.

Регистрами ввода/вывода являются регистры SREG, MCUSR и указатель стека SPH:SPL а также регистры, управляющие системой прерывания микроконтроллера, режимами подключения EEPROM памяти, сторожевым таймером, портами ввода/вывода и другими периферийными узлами. Все регистры ввода/вывода могут считываться и записываться через РОН (POH — регистры общего назначения) при помощи команд IN, OUT Регистры ввода/вывода, имеющие адреса в диапазоне $00 - $1F (знак $ указывает на шестнадцатеричную систему счисления), обладают возможностью побитовой адресации. Непосредственная установка и сброс отдельных разрядов этих регистров выполняется командами SBI и CBI Для признаков результата операции, которые являются битами регистра ввода/вывода SREG, имеется целый набор команд установки и сброса. Команды условных переходов в качестве своих операндов могут иметь как биты-признаки результата операции, так и отдельные разряды побитно адресуемых регистров ввода/вывода. На рис. 2.3 показано распределение адресов в едином адресном пространстве.

Младшие

32 адреса ($0 - $1F) соответствуют оперативным

регистрам т.е. РОН. Следующие 64 адреса

($20 - $5F) зарезервированы для регистров

ввода/вывода. Внутренняя SRAM у всех AVR

начинается с адреса $60. Таким образом,

регистры ввода/вывода имеют двойную

нумерацию. Если используются команды

IN, OUT, SBI, CBI, SBIC, SBIS, то следует использовать

нумерацию регистров ввода/вывода,

начинающуюся с нуля (назовем ее основной).

Если же к регистрам ввода/вывода доступ

осуществляется как к ячейкам памяти,

то необходимо использовать нумерацию

единого адресного пространства

оперативной памяти данных AVR. Очевидно,

что адрес в едином адресном пространстве

памяти данных получается путем прибавления

числа $20 к основному адресу регистра

ввода/вывода. Для хранения оперативных

данных программист, кроме РОН, может

использовать внутреннюю и внешнюю (если

они имеются) блоки SRAM (см. рис. 2.3).

Рис. 2.3. Программная модель

AVR-микроконтроллеров. Работа с внешней

SRAM может быть программно разрешена/запрещена

установкой/сбросом бита SRE в регистре

ввода/вывода MCUSR. Операции обмена с

внутренней оперативной памятью

AVR-микроконтроллер выполняет за два

машинных цикла. Доступ к внешней SRAM

требует одного дополнительного цикла

на каждый байт по сравнению с внутренней

памятью. Кроме того, установкой бита

SRW в регистре ввода/вывода MCUSR можно

программно увеличить время обмена с

внешней SRAM еще на один дополнительный

машинный цикл ожидания. Выполнять

арифметико-логические операции и

операции сдвига непосредственно над

содержимым ячеек памяти нельзя. Нельзя

также записать константу или очистить

содержимое ячейки памяти. Система команд

AVR позволяет лишь выполнять операции

обмена данными между ячейками SRAM и

оперативными регистрами. Достоинством

системы команд можно считать разнообразные

режимы адресации ячеек памяти. Кроме

прямой адресации имеются следующие

режимы: косвенная, косвенная с

пост-инкрементом, косвенная с

пре-декрементом и косвенная со смещением.

Поскольку внутренняя и внешняя SRAM входят

в единое адресное пространство (вместе

с оперативными регистрами и регистрами

ввода/вывода), то для доступа к ячейкам

внутренней и внешней памяти используются

одни и те же команды. Следует отметить,

что регистры ввода/вывода не полностью

используют отведенные для них 64 адреса.

Неиспользуемые адреса зарезервированы

для будущих применений, дополнительных

ячеек памяти по этим адресам не существует.

Младшие

32 адреса ($0 - $1F) соответствуют оперативным

регистрам т.е. РОН. Следующие 64 адреса

($20 - $5F) зарезервированы для регистров

ввода/вывода. Внутренняя SRAM у всех AVR

начинается с адреса $60. Таким образом,

регистры ввода/вывода имеют двойную

нумерацию. Если используются команды

IN, OUT, SBI, CBI, SBIC, SBIS, то следует использовать

нумерацию регистров ввода/вывода,

начинающуюся с нуля (назовем ее основной).

Если же к регистрам ввода/вывода доступ

осуществляется как к ячейкам памяти,

то необходимо использовать нумерацию

единого адресного пространства

оперативной памяти данных AVR. Очевидно,

что адрес в едином адресном пространстве

памяти данных получается путем прибавления

числа $20 к основному адресу регистра

ввода/вывода. Для хранения оперативных

данных программист, кроме РОН, может

использовать внутреннюю и внешнюю (если

они имеются) блоки SRAM (см. рис. 2.3).

Рис. 2.3. Программная модель

AVR-микроконтроллеров. Работа с внешней

SRAM может быть программно разрешена/запрещена

установкой/сбросом бита SRE в регистре

ввода/вывода MCUSR. Операции обмена с

внутренней оперативной памятью

AVR-микроконтроллер выполняет за два

машинных цикла. Доступ к внешней SRAM

требует одного дополнительного цикла

на каждый байт по сравнению с внутренней

памятью. Кроме того, установкой бита

SRW в регистре ввода/вывода MCUSR можно

программно увеличить время обмена с

внешней SRAM еще на один дополнительный

машинный цикл ожидания. Выполнять

арифметико-логические операции и

операции сдвига непосредственно над

содержимым ячеек памяти нельзя. Нельзя

также записать константу или очистить

содержимое ячейки памяти. Система команд

AVR позволяет лишь выполнять операции

обмена данными между ячейками SRAM и

оперативными регистрами. Достоинством

системы команд можно считать разнообразные

режимы адресации ячеек памяти. Кроме

прямой адресации имеются следующие

режимы: косвенная, косвенная с

пост-инкрементом, косвенная с

пре-декрементом и косвенная со смещением.

Поскольку внутренняя и внешняя SRAM входят

в единое адресное пространство (вместе

с оперативными регистрами и регистрами

ввода/вывода), то для доступа к ячейкам

внутренней и внешней памяти используются

одни и те же команды. Следует отметить,

что регистры ввода/вывода не полностью

используют отведенные для них 64 адреса.

Неиспользуемые адреса зарезервированы

для будущих применений, дополнительных

ячеек памяти по этим адресам не существует.

Циклы обмена между процессором и памятью

Синхронный обмен без ожидания готовности данных. Этот тип обмена реализован между процессором и памятью. При этом быстродействие микросхем памяти должно соответствовать длительности циклов чтения-записи, реализуемых процессором. Инициатор обмена– всегда процессор (действия – чтение команд, передача данных в ходе выполнения команд).

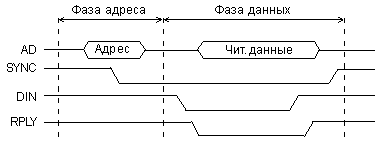

На шине адреса/данных (AD) в начале цикла обмена (в фазе адреса) процессор (задатчик) выставляет код адреса. На этой шине используется отрицательная логика. Средний уровень сигналов на шине AD обозначает, что состояния сигналов на шине в данные временные интервалы не важны. Для стробирования адреса используется отрицательный синхросигнал -SYNC, выставляемый также процессором. Его передний (отрицательный) фронт соответствует действительности кода адреса на шине AD. Фаза адреса одинакова в обоих циклах записи и чтения.

|

|

|

|

Рис. 2.3. Цикл чтения на магистрали Q-bus. |

Рис. 2.4. Цикл записи на магистрали Q-bus. |

Получив (распознав) свой код адреса, устройство ввода/вывода или память (исполнитель) готовится к проведению обмена. Через некоторое время после начала (отрицательного фронта) сигнала -SYNC процессор снимает адрес и начинает фазу данных. В фазе данных цикла чтения (рис. 2.3) процессор выставляет сигнал строба чтения данных -DIN, в ответ на который устройство, к которому обращается процессор (исполнитель), должно выставить свой код данных (читаемые данные). Одновременно это устройство должно подтвердить выполнение операции сигналом подтверждения обмена -RPLY. Для сигнала -RPLY используется тип выходного каскада ОК, чтобы не было конфликтов между устройствами-исполнителями. Процессор, получив сигнал -RPLY, заканчивает цикл обмена. Для этого он снимает сигнал -DIN и сигнал -SYNC. Устройство-исполнитель в ответ на снятие сигнала -DIN должно снять код данных с шины AD и закончить сигнал подтверждения -RPLY. После этого процессор снимает сигнал -SYNC. В фазе данных цикла записи (рис. 2.4) процессор выставляет на шину AD код записываемых данных и сопровождает его отрицательным сигналом строба записи данных -DOUT. Устройство-исполнитель должно по этому сигналу принять данные от процессора и сформировать сигнал подтверждения обмена -RPLY. Процессор, получив сигнал -RPLY, заканчивает цикл обмена. Для этого он снимает код данных с шины AD и сигнал -DOUT. Устройство-исполнитель в ответ на снятие сигнала -DOUT должно закончить сигнал подтверждения -RPLY. После этого процессор снимает сигнал -SYNC. То есть на данной магистрали адрес передается синхронно (без подтверждения его получения исполнителем), а данные передаются асинхронно, с обязательным подтверждением их выдачи или приема исполнителем. Отсутствие сигнала подтверждения -RPLY в течение заданного времени воспринимается процессором как аварийная ситуация. В принципе возможна и асинхронная передача адреса, что увеличивает надежность обмена, хотя может снижать его скорость.

26. Абсолютная, прямая и косвенная адресация.

Пространство памяти предназначено для хранения кодов команд и данных, для доступа к которым имеется богатый выбор методов адресации (около 24). Операнды могут находиться во внутренних регистрах процессора (наиболее удобный и быстрый вариант). Они могут располагаться в системной памяти (самый распространенный вариант). Наконец, они могут находиться в устройствах ввода/вывода (наиболее редкий случай). Определение места положения операндов производится кодом команды. Причем существуют разные методы, с помощью которых код команды может определить, откуда брать входной операнд и куда помещать выходной операнд. Эти методы называются методами адресации. Эффективность выбранных методов адресации во многом определяет эффективность работы всего процессора в целом.

^ Прямая или абсолютная адресация. Физический адрес операнда содержится в адресной части команды. Формальное обозначение:

Операндi = (Аi),

где Аi – код, содержащийся в i-м адресном поле команды.

Рис. 9.1 Прямая адресация

Пример: mov al,[2000] – передать операнд, который содержится по адресу 2000h в регистр AL.

Add R1,[1000] – сложить содержимое регистра R1 с содержимым ячейки памяти по адресу 1000h и результат переслать в R1.

Допускается использование прямой адресации при обращении, как к основной, так и к регистровой памяти.

Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд.

Операндi= Аi.

![]()

Рис. 9.2 Непосредственная адресация

Непосредственная адресация позволяет повысить скорость выполнения операции, так как в этом случае вся команда, включая операнд, считывается из памяти одновременно и на время выполнения команды хранится в процессоре в специальном регистре команд (РК). Однако при использовании непосредственной адресации появляется зависимость кодов команд от данных, что требует изменения программы при каждом изменении непосредственного операнда.

Пример: mov eax,0f0f0f0f0 – загрузить константу 0f0f0f0f0h в регистр eax.

^ Косвенная (базовая) адресация. Адресная часть команды указывает адрес ячейки памяти (рис. 7.3,а) или номер регистра (рис. 7.3,б), в которых содержится адрес операнда:

Операндi = ((Аi)).

Рис. 9.3 Косвенная адресация

Применение косвенной адресации операнда из оперативной памяти при хранении его адреса в регистровой памяти существенно сокращает длину поля адреса, одновременно сохраняя возможность использовать для указания физического адреса полную разрядность регистра. Недостаток этого способа – необходимо дополнительное время для чтения адреса операнда. Вместе с тем он существенно повышает гибкость программирования. Изменяя содержимое ячейки памяти или регистра, через которые осуществляется адресация, можно, не меняя команды в программе, обрабатывать операнды, хранящиеся по разным адресам. Косвенная адресация не применяется по отношению к операндам, находящимся в регистровой памяти.

Пример: mov al,[ecx] – передать в регистр AL операнд (содержимое) ячейки памяти, адрес которой находится в регистре ECX.

Предоставляемые косвенной адресацией возможности могут быть расширены, если в системе команд ЭВМ предусмотреть определенные арифметические и логические операции над ячейкой памяти или регистром, через которые выполняется адресация, например увеличение или уменьшение их значения на единицу (и не только на 1).

В этом случае речь идет о базовой адресации со смещением.

Пример: mov eax,[eci+4] – передать в EAX операнд, который содержится по адресу ECI со смещением плюс 4.

Иногда, адресация, при которой после каждого обращения по заданному адресу с использованием механизма косвенной адресация, значение адресной ячейки автоматически увеличивается на длину считываемого операнда, называется автоинкрементной. Адресация с автоматическим уменьшением значения адресной ячейки называется автодекрементной.

^ Регистровая адресация. Предполагается, что операнд находится во внутреннем регистре процессора.

Например: mov eax,cr0 – передать в EAX содержимое CR0 или

mov ecx,ecx – сбросить регистр ECX.

^ Индексная адресация (со смещением) – содержимое РОН используется в качестве компоненты эффективного адреса (как правило, работа с массивами).

Пример: sub array [esi],2 – вычесть 2 из элемента массива, на который указывает регистр ESI.

^ Относительная адресация. Этот способ используется тогда, когда память логически разбивается на блоки, называемые сегментами. В этом случае адрес ячейки памяти содержит две составляющих: адрес начала сегмента (базовый адрес) и смещение адреса операнда в сегменте. Адрес операнда определяется как сумма базового адреса и смещения относительно этой базы:

Операндi = (базаi + смещениеi).

Для задания базового адреса и смещения могут применяться ранее рассмотренные способы адресации. Как правило, базовый адрес находится в одном из регистров регистровой памяти, а смещение может быть задано в самой команде или регистре.

Рассмотрим два примера.

Адресное поле команды состоит из двух частей, в одной указывается номер регистра, хранящего базовое значение адреса (начальный адрес сегмента), а в другом адресном поле задается смещение, определяющее положение ячейки относительно начала сегмента. Именно такой способ представления адреса обычно и называют относительной адресацией.

Рис. 9.4 Относительная адресация

Первая часть адресного поля команды также определяет номер базового регистра, а вторая содержит номер регистра, в котором находится смещение. Такой способ адресации чаще всего называют базово-индексным.

Рис. 9.5 Базово-индексная адресация

Главный недостаток относительной адресации – большое время вычисления физического адреса операнда. Но существенное преимущество этого способа адресации заключается в возможности создания "перемещаемых" программ – программ, которые можно размещать в различных частях памяти без изменения команд программы. То же относится к программам, обрабатывающим по единому алгоритму информацию, расположенную в различных областях ЗУ. В этих случаях достаточно изменить содержимое базового адреса начала команд программы или массива данных, а не модифицировать сами команды. По этой причине относительная адресация облегчает распределение памяти при составлении сложных программ и широко используется при автоматическом распределении памяти в мультипрограммных вычислительных системах.