- •Вопросы по курсу тсис для группы 2032

- •1 Вариант

- •2 Вариант:

- •23.Команда. Формат команды. Классификация команд. Особенности состава команд Intel.

- •25. Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

- •27.Автоинкрементная и автодекрементная адресация.

- •Уровни кэша

- •31.Сегментная и страничная организация доступа к памяти.

- •32.Режимы работы

- •Реальный режим (Real Mode)

- •Режим системного управления (System Management Mode)

- •Защищенный режим (Protected Mode)

- •34. Конвейеризация и векторизация обработки данных

- •37. Устройства ввода информации. Сенсорные экраны.

- •Проекционно-ёмкостные сенсорные экраны Конструкция и принцип работы

- •Особенности

- •Пятипроводной резистивный сенсорный экран.

- •Сенсорные экраны на поверхностно-акустических волнах Конструкция и принцип работы

- •Инфракрасные сенсорные экраны

- •Сенсорные экраны dst

- •Индукционные сенсорные экраны

23.Команда. Формат команды. Классификация команд. Особенности состава команд Intel.

Команда – это код, определяющий операцию вычислительной машины и данные, участвующие в операции. Команда также содержит в явной или неявной форме информацию об адресе, по которому помещается результат операции, и об адресе следующей команды.

- совокупность сведений, представленных в виде двоичных кодов, необходимых процессору для выполнения очередного шага.

В команде зачастую содержатся не сами операнды, а информация об их расположении (адреса ячеек памяти и регистры, где они находятся).

Общая структура команды имеет следующий вид:

![]() ,т.е.

операционная и адресная части.

,т.е.

операционная и адресная части.

Операционная часть содержит код операции, кот. задает вид операции (сложение, умножение, передача и т.п.),т.е. это двоичный код, который однозначно указывает процессору на выполнение конкретных действий(сложение, пересылка) и определяющий при этом форму задания адресов операндов.

Адресная часть содержит информацию об адресах операндов и результата операции, а иногда и адрес следующей команды, это тоже двоичное число!

В свою очередь, эти части, что особенно характерно для адресной части, могут состоять из нескольких полей.

Структура команды определяется составом, назначением и расположением полей в коде.

Форматом команды называется заранее оговоренная структура полей ее кода с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием числа разрядов (бит) в определенных полях, позволяющая ЭВМ распознавать составные части кода.

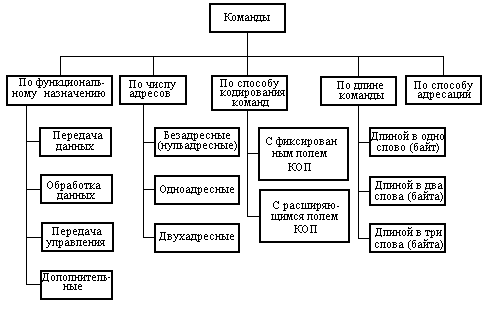

Классификация команд по основным признакам:

Первую классификацию можно представить след. образом:

¨ команды арифметических операций для чисел с фиксированной или плавающей запятой;

¨ команды десятичной арифметики;

¨ команды передачи данных (MOV AX, 0FFFh);

¨ команды операций ввода/вывода (IN, OUT);

¨ команды логических операций (AND, OR, NOT);

¨ команды передачи управления (управление циклом — LOOP, условные переходы — JAE, JB);

¨ команды задания режима работы машины и др.

По адресности (количеству адресов в адресном поле) команды подразделяются на:

1) Трехадресные – А1, А2 – адреса операндов, А3 – адрес результата,

ОЗУ[А3]:=ОЗУ[А1]*ОЗУ[А2] - справедливо для прямой адресации

Т.е.первый и второй адреса указывают адрес ячейки памяти, в которых расположены операнды, а третий определяет ячейку, в которую размещается результат операции.

2) двухадресные – А1 является адресом первого операнда, А2 – адресом второго операнда, результат записывается либо по одному из адресов, либо остается в аккумуляторе:

ОЗУ[А1]:=ОЗУ[А1]*ОЗУ[А2] - результат записывается по одному из адресов,

АКК:=ОЗУ[А1]*ОЗУ[А2] - результат остается в аккумуляторе,

3) одноадресные. Здесь подразумеваемые адреса имеют и результат операции и один из операндов. Один из операндов указывается адресом в команде, в качестве второго используется содержимое регистра процессора, называемого в таком случае регистром результата или аккумулятором. Результат операции записывается в тот же регистр.

АКК:=ОЗУ[А1]*<АКК>, где * - арифметическая или логическая операция,

В некоторых случаях возможно использование безадресных команд, когда подразумеваются адреса обоих операндов и результаты операции, например при работе со стековой памятью.

Для программиста наиболее естественны и удобны трехадресные команды. Однако из-за необходимости иметь большое число разрядов для представления адресов и кода операции длина трехадресной команды становится недопустимо большой, и ее не удается разместить в машинном слове. Следует отметить, что очень часто в качестве операндов исп-ся результаты операций, хранимые в регистрах машины. В этом случае выполняемые команды носят 1 и 2-х адресный характер, поэтому 3-х адресные - редко.

Обычно в ЭВМ используется несколько форматов команд разной длины. В действительности же адресные поля команд большей частью содержат не сами адреса, а только информацию, позволяющую определить действительные (исполнительные) адреса операндов в соответствии с используемыми в командах способами адресации.

Для того, чтобы команда содержала в явном виде всю необходимую информацию о задаваемой операции, она должна содержать поле кода операции и четыре адреса для указания ячеек памяти, содержащих два операнда, участвующих в операции, ячейки, в которую помещается результат операции, и ячейки, содержащей следующую команд. Что делать с адресами операндов, мы уже рассмотрели. Порядок выборки команд, когда в ней содержится сразу адрес следующей команды, называется принудительным. Он использовался в некоторых первых моделях ЭВМ и в настоящее время не применяется.

Можно установить, как это принято для большинства машин, что после выполнения данной команды, расположенной по адресу К (и занимающей L ячеек), выполняется команда из (K+L)-й ячейки. Такой порядок выборки команд называется естественным. Он нарушается только специальными командами. В таком случае отпадает необходимость указывать в команде в явной форме адрес следующей команды.

Особенности состава команд Intel.

Почти во всех форматах команд первые биты отводятся для кода операции, но далее форматы команд разных ЭВМ сильно отличаются друг от друга. Остальные биты должны определять операнды или их адреса, и поэтому они используются для комбинации режимов, адресов регистров, адресов памяти, относительных адресов и непосредственных операндов. Обычно длина команды варьируется от 1 до 3 и даже 6 байт.

По форматам команд можно судить о возможностях ЭВМ.

Процессоры Intel основаны на CISC архитектуре (формально все х86-процессоры).

CISC (англ. Complex instruction set computing, или англ. complex instruction set computer — компьютер с комплексным набором команд) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

нефиксированное значение длины команды;

арифметические действия кодируются в одной команде;

небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Наиболее распространённая архитектура современных настольных, серверных и мобильных процессоров построена по архитектуре Intel x86 (или х86-64 в случае 64-разрядных процессоров). Формально, все х86-процессоры являлись CISC-процессорами, однако новые процессоры, начиная с Intel Pentium Pro, являются CISC-процессорами с RISC-ядром (RISC (англ. restricted (reduced) instruction set computer — компьютер с сокращённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — короче). Они непосредственно перед исполнением преобразуют CISC-инструкции процессоров x86 в более простой набор внутренних инструкций RISC.

В микропроцессор встраивается аппаратный транслятор, превращающий команды x86 в команды внутреннего RISC-процессора. При этом одна команда x86 может порождать несколько RISC-команд (в случае процессоров типа P6 — до четырёх RISC-команд в большинстве случаев). Исполнение команд происходит на суперскалярном конвейере одновременно по несколько штук.

Это потребовалось для увеличения скорости обработки CISC-команд, так как известно, что любой CISC-процессор уступает RISC-процессорам по количеству выполняемых операций в секунду. В итоге, такой подход и позволил поднять производительность CPU.

Микропроцессор Intel-8086 (К1810ВМ80) имеет двухадресную систему команд. Ее особенностью является отсутствие команд, использующих оба операнда из оперативной памяти. Исключение составляют лишь команды пересылки и сравнения цепочек байт или слов, которые в данном пособии рассматриваться не будут. Таким образом, в командах допустимы следующие сочетания операндов: RR, RS, RI, SI. Здесь R обозначает операнд, находящийся в одном из регистров регистровой памяти микропроцессора, S - операнд, находящийся в оперативной памяти, адрес которого формируется по одному из допустимых способов адресации, I - непосредственный операнд, закодированный в адресном поле самой команды. Формат команды во многом определяется способом адресации операнда, находящего в оперативной памяти, длиной используемого непосредственного операнда, а также наличием и длиной смещения, используемого при относительных режимах адресации.

Ввод-вывод: программный, по прерываниям и ПДП.

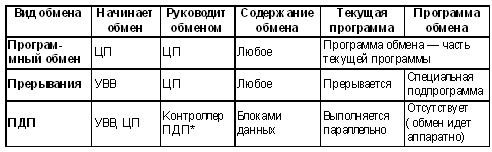

три режима обмена данными ВВ(ввода - вывода):

программный ВВ (называемый также программно - управляемым или нефорсированным ВВ) - только программный режим;

ВВ по прерываниям (форсированный ВВ) - комбинированный программно-аппаратный режим;

прямой доступ к памяти - только аппаратный режим.

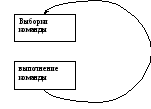

Принцип Фон Неймана:

ПК работает по программе, хранимой в памяти, в той, что и данные, в виде, не отличимом от данных с целью выяснения дальнейшего порядка выполнения операторов.

Информация:

-несет что-то новое

-передается в виде не отличимом от данных

-она должна быть понятна.

Программа состоит из операторов 2-х типов:

-преобразующих данные

-анализирующих данные

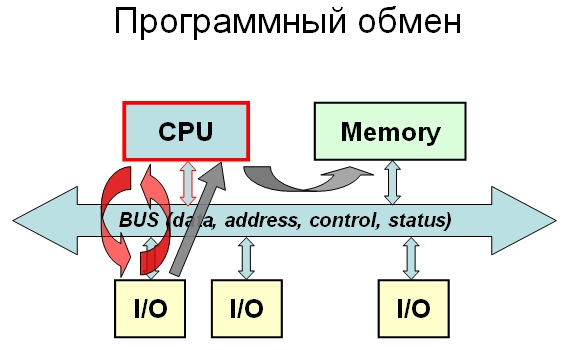

Программно-управляемыйобмен характеризуется тем, что все действия по вводу или выводу предусмотрены непосредственно в теле программы. Процессор полностью руководит ходом обмена, включая ожидание готовности периферийного устройства и прочие временные задержки, связанные с процессами ввода/вывода.

Процессор выполняет все стадии обмена:

– опрос готовности устройства, – собственно, передачу данных.

Производительность системы в целом падает из-за простоев (ожиданий) процессора.

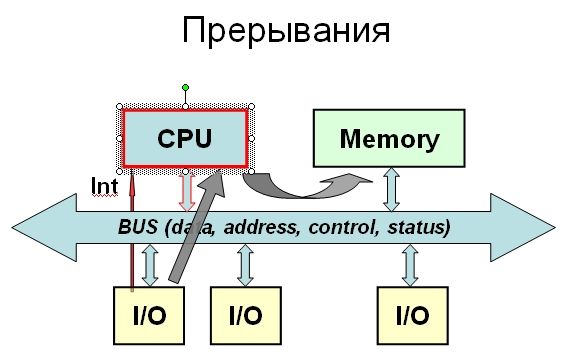

Суть обмена по прерываниямзаключается в том, что УВВ сами требуют внимания процессора в том случае, когда оно необходимо. Например, клавиатура оповещает процессор, если была нажата или отпущена клавиша; все остальное время процессор выполняет программу, “не отвлекаясь” на клавиатуру.

Процессор выполняет только передачу данных.

Опрос готовности устройства заменен системой прерываний, которая передает сигнал о готовности и помогает определить его источник.

Производительность системы в целом возрастает из-за отсутствия простоев (ожиданий) процессора.

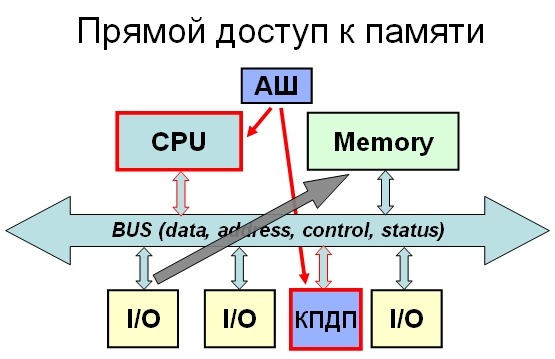

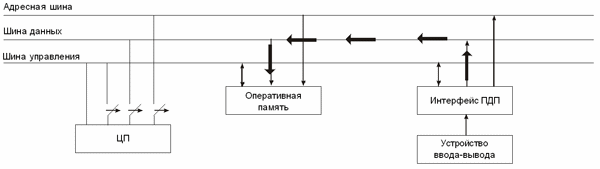

В обоих описанных выше видах обмена руководство осуществлял ЦП. Чтобы улучшить эффективность использования вычислительной системы и увеличить скорость транспортировки крупных блоковданных от устройств в память и обратно, в современных компьютерах разработан так называемыйпрямой доступ к памяти(по-английски DMA —Direct Memory Access). Принципиальное отличие ПДП заключается в том, что в этом режиме процессор непроизводитобмен, а толькоподготавливаетего, программируя контроллера ПДП.

Процессор не выполняет передачу данных. Этим управляет контроллер ПДП, получив управление шиной.

На управление шиной теперь претендуют два (или более) устройства. Над ними появляется Арбитр шины.

Производительность возрастает т.к. шина используется интенсивнее, обмен выполняется параллельно.