-

Выбор основных компонентов

-

Выбор микроконтроллера

Контроллер I8085a, выполненный по К-МОП технологии. Существует, советский аналог К1821ВМ85А который представляет тот же контроллер.

Рис. 2 Функциональная схема МП I8085A

МП имеет 16-разрядный счётчик команд и защёлку адреса, которая загружает специализированную адресную (А15–А18) и мультиплексированную (AD7 – AD0) шины. Параллельные данные входят в МП и покидают его через (AD7 – AD0). Эта шина передаёт адрес, когда линия управления ALE получает Н-сигнал, и данные – когда L-сигнал.

По 8-разрядной внутренней шине входящие и выходящие данные вводятся внутрь устройства. Они могут поступать с внутренней шины данных в следующие части МП :

– 8-разрядный аккумулятор;

– регистр временного хранения;

– индикаторы;

– регистр команд;

– устройство управления;

– какой-либо из регистров общего назначения (B, C, D, E, H, L);

– 16-разрядный указатель стека;

– 16-разрядный счётчик команд;

– 8-разрядный буфер адреса/данных.

Арифметико-логическое устройство загружается двумя 8-разрядными регистрами (аккумулятором и регистром временного хранения), как в типовом МП. Регистр состояний содержит пять индикаторов состояния вместо двух, как это было в типовом МП. Регистр команд связан с дешифратором, который

определяет текущую команду, требуемую микропрограмму или следующий машинный цикл, а затем информирует схему управления и синхронизации о последовательности действий.

Счетчик команд PC используется для указания на адрес следующей выполняемой команды. Содержимое PC может быть изменено командами переходов, вызова подпрограмм и возврата из них.

Указатель стека SP предназначен для адресации особым образом организованной области памяти, называемой стеком. Он всегда указывает на вершину стека, содержащую последний введенный в него элемент. Стек заполняется в сторону младших адресов, что считается стандартным для МС.

Регистр состояния (флагов или индикаторов) RF использует 5 битов (флажков) хранения информации о состоянии МП. Флажки имеют следующее назначение:

CY - признак переноса из старшего разряда АЛУ;

Р - признак четного числа единиц в результате операции;

АС - признак дополнительного переноса из младших четырех разрядов АЛУ;

Z - признак нулевого результата;

М - знак результата.

Автоматическая установка битов в единицу происходит в результате выполнения арифметических и логических операций при условии наступления соответствующего назначению бита события, в противном случае содержимое битов сбрасывается в нуль. Эти биты используются командами условных переходов, вызова подпрограмм и возврата из них.

Кодирование команд и адресация данных

Команды ВМ85А требуют для кодирования от 1 до 3 байт. Первый байт всегда содержит код операции. Второй и при необходимости третий байты отводятся под непосредственные данные, адрес порта или ячейки памяти (рис. 3).

Рис. 3. Формат команд МП ВМ85А: а- однобайтовый, б- двухбайтовый, в- трехбайтовый

Поля dst и src предназначены для кодирования операндов в одно- и двухбайтовых командах МП согласно правилу

![]()

где фиктивный регистр М задает в качестве операнда ячейку памяти, косвенно адресуемую через регистровую пару HL.

Команды МП содержат именную часть команды или код операции, а также адресную часть, содержащую сведения об адресах операндов. Источниками и приемниками операндов могут служить: регистры МП, ячейки памяти, а также порты ВВ. Сведения о месторасположении операндов могут задаваться в двух формах: явной и неявной. Неявная форма обеспечивает передачу адресной информации через код операции, для чего используются поля dst и src на (рис. 3). Достоинства такого подхода - в малой длине машинных команд, требующих меньшего времени для своего выполнения.

Большей гибкостью обладают команды, использующие явную форму задания адресной информации, что позволяет связывать с одной командой множество адресов, повышая ее эффективность. Однако при этом возрастает длина машинной команды и соответственно снижается эффективность объектного кода. На практике часто встречаются и комбинированные формы адресации, содержащие явную и неявную части.

Примеры команд, использующих явную адресацию: LXIrp,datal6 ; LHLD addr ADI data8

Примеры команд с неявной адресацией: MOV R1,R2 ; LDAX D ADDR

Метод задания адресов операндов в памяти называется способом адресации. Для повышения эффективности программного кода (т. е. минимизации длины программы или времени ее выполнения) разработан ряд способов адресации, каждый из которых наиболее эффективен для своей конкретной ситуации. Правильное использование всего набора позволяет обеспечить эффективный доступ к структурированным данным (массивы, стеки), сократить длину программного кода и число обращений к магистрали.

МП ВМ85А имеет следующие способы адресации: прямую, регистровую, непосредственную, косвенную регистровую. В случае регистровой адресации операнд находится в одном из внутренних регистров МП. Примеры команд с регистровой адресацией: MOV R1,R2. ADDR.

Поскольку для ссылки на регистр требуется всего лишь несколько бит, включаемых в код операции, команды данного типа имеют наименьшую длину и не требуют циклов обращения к магистрали. Все это обеспечивает командам регистровой адресации наибольшую эффективность.

Команды с прямым способом адресации используют для задания места расположения данных в памяти второй и третий байты команды. Прямая адресация позволяет явно выбрать любую ячейку памяти или порт ВВ во всем адресном пространстве МП. Примеры команд данного типа: IN, port ; LHLD addr

В случае непосредственной адресации источником данных служит сама команда, второй и, если необходимо, третий байт которой служат для задания констант. Например: LXI В,1234 ; MVI D, 5.

Основной недостаток непосредственной адресации заключается в невозможности манипуляции данными без изменения программного кода, что привело к созданию способов с вычисляемым адресом, к простейшим из которых относится косвенная регистровая адресация. В командах с косвенной адресацией указывается не прямой адрес ячейки памяти, а регистровая пара МП, содержащая адрес операнда. К командам, использующим косвенный способ адресации, в частности, относятся: MOV A, M;LDAX B.

-

Сопряжение ВМ85А с шинами микропроцессорной системы

В ряде применений однокристальные МП не могут быть непосредственно соединены с шинами МС по причине недостаточной нагрузочной способности их выходов. Для организации сопряжения МП с системными шинами в этом случае находят применение буферные регистры и шинные формирователи. Ниже рассмотрены некоторые типичные представители данных классов микросхем.

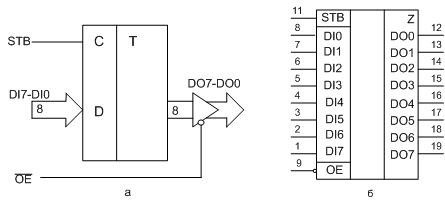

Буферный регистр КР580ИР82/ИР83 представляет собой 8-разрядный регистр-защелку, обеспечивающий выходной ток до 32 мА ,и емкость нагрузки до 300 пФ и используемый в качестве фиксатора или буфера. На (рис. 4) приведены схема и условное графическое обозначение регистра КР580ИР82, в отличие от которого КР580ИР83 имеет инверсные выходные сигналы.

Рис. 4. Буферный регистр КР580ИР82: а- структурная схема; б- условное графическое обозначение

Основой схемы является 8-разрядный регистр со статическим управляющим входом STB, разрешающим запись при высоком уровне сигнала и хранение при низком уровне. Регистр содержит трехстабильный выходной буфер, управляемый сигналом ОЕ. При активном уровне этого сигнала (ОЕ=0) данные передаются на выход микросхемы, в ином случае буфер закрыт и находится в высокоомном состоянии. Временные диаграммы работы регистра представлены на (рис. 5).

Рис. 5. Временные диаграммы работы регистров КР580ИР82/ИР83

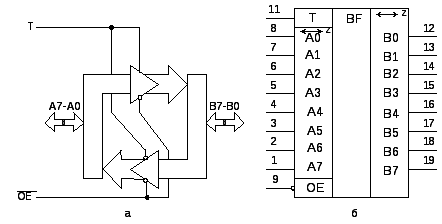

Шинный формирователь КР580ВА86/ВА87 предназначен для реализации 8-разрядных одно- и двунаправленных буферных схем с тремя состояниями на выходе. На рис. 6 приведены схема и условное графическое обозначение БИС КР580ВА86, в отличие от которого КР580ИР83 имеет инверсные выходные сигналы.

Рис. 6. Шинный формирователь КР580ВА86: а- структурная схема; б- условное графическое обозначение