-

Анализ технического задания

Проанализируем каждый пункт по техническому заданию.

-

Intel8085 в DIP-корпусе с 40 выводами не требует дополнительных выводов для обеспечения всех входов и выходов; по этой причине выводы с 12 по 19 использованы как равноценные линии шины адреса/данных (AD0 – AD7). Поэтому этот микропроцессор называется устройством с мультиплексированной шиной данных/адреса. Адресные шины восьми младших разрядов разделяют выводы с линиями шины данных.

Необходимо отметить, что выводы мультиплексированной шины двунаправлены или могут быть в положении трёх состояний. Вывод управления ALE является выходным. МП Intel 8085 (как и типовой процессор) имеет 16 адресных линий. Восемь старших разрядов выведены на выводы А8–А15.. Как и в случае типового МП, подсоединение к шинам прямое. Эти выводы являются выходами или могут быть в состоянии высокого сопротивления (в третьем состоянии). Другие выводы, идентичные выводам типового МП, являются выводами питания VCC и VSS , подсоединёнными к источнику + 5 В.

-

Выберем АЦП по следующим требованиям:

- диапазон входного напряжения 0 В до +10 В;

- частотный спектр – 100 до 10000 Гц;

- соотношение сигнал/шум – 70 дБ.

Рассчитаем разрядность АЦП исходя из соотношения сигнал/шум по формуле:

с/ш=6,02n+1,76, следовательно n=11.336≈12 разрядов.

Найдем частоту дискретизации по теореме Котельникова.

Согласно теореме Котельникова частота дискретизации аналогового сигнала должна быть в два раза больше верхней граничной частоты данного сигнала. f≥2fc.

f=2fc=20000 Гц – частота дискретизации.

Для данной частоты дискретизации, допустимое время преобразования будет равно:

.

.

3) Число разрядов АЦП-12

4) С помощью АЦП можно преобразовывать аналоговый сигнал в цифровой и записывать данные об этом сигнале в ОЗУ. В моем варианте объем ОЗУ равно 2К. Блок ОЗУ предназначен для кратковременного или длительного хранения информации, которая в ходе работы устройства отображается на индикаторе.

5) Для контролирования микропроцессорной системы используются 4 кнопки управления.

6) ССИ. Алфавитно-цифровые ССИ-модули представляют собой недорогое и удобное решение, позволяющее сэкономить время и ресурсы при разработке новых изделий, при этом обеспечивают отображение информации при хорошей различимости и низком энергопотреблении.

7) Количество индикаторов - 4.

8) Тип последовательного канала – USB.

-

Разработка структурной схемы

Структурная схема представляет собой соединение и модификация типовой микропроцессорной системы с учетом особенностей конкретных элементов этой структуры.

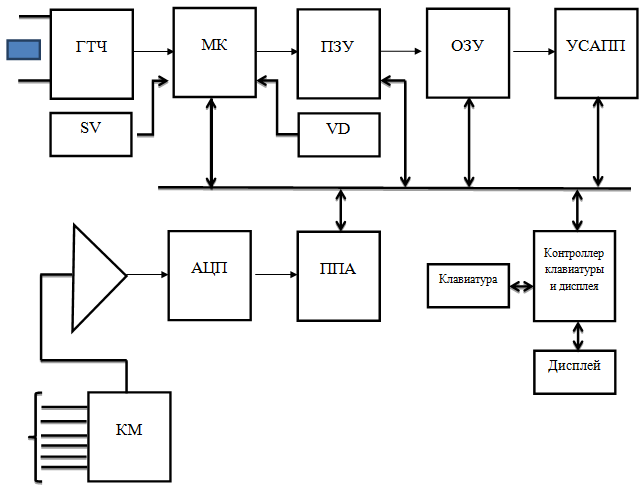

Рис. 1 – Структурная схема микропроцессорной системы

По техническому заданию необходимо использовать К 1821ВМ85, схема которого показана на рисунке 1. Она состоит из следующих основных блоков: центрального микропроцессора, ПЗУ, ОЗУ, последовательный порт, контроллер клавиатуры и дисплея, предназначенный для ввода данных с клавиатуры и вывода информации на дисплей, коммутатор, согласующее устройство, АЦП, программируемый параллельный адаптер, сторожевой таймер, кварцевый резонатор.

Возможно подключение рассмотренных устройств к системной шине МК или к свободным портам ввода/вывода. Подключение к портам ввода/вывода обеспечивает гибкость в управлении устройством, но усложняет программное обеспечение.

Подключение к системной шине требует согласования временных характеристик подключаемых устройств и системной шины.

При таком подключении упрощается программирование МК при работе с данными устройствами. Для проведения арбитража на системной шине необходимо введение дешифраторов. При магистральном подключении возможно расширение микропроцессорной системы, подключая дополнительные компоненты.