- •1,320 Способы включения транзисторов в схему усилителя

- •Разновидности цепей обратной связи

- •1,6 Влияние оос на свойства усилителей

- •Схемы оу

- •Применение оу

- •Схемы оу

- •1,20 Аналого – цифровые преобразователи

- •17.5.1Резисторные логические элементы (рл)

- •17.5.2. Диодные логические элементы (дл)

- •2,5 Логическое сложение

- •.Классификация зу

- •18.2.3. Устройства типа ерrом и еерrом

17.5.1Резисторные логические элементы (рл)

Предположим, что в приведенной схеме (Рис.66,а) R1=R2=R3=R и на входах А,В,С, действуют напряжения 0В или 1В. В результате Uвых. принимать значения :

1) Uвых1= 0,5В,если напряжение 1В действует только на одном входе;

2) Uвых2= 1,0В, если напряжение 1В действует на двух входах одновременно;

3) Uвых3= 1,5В, если напряжение 1В действует на трёх входах одновременно.

Если к выходу резистивной схемы подключить триггер и напряжением Есмещ. выбрать порог опрокидывания триггераUоткр..= 0,5В, то полученная схема работает как схема ИЛИ.

Если порог опрокидывания триггера установить равным Uоткр.= 1,5В, то мы имеем схему И.

Рассмотренные логические элементы имеют ряд существенных недостатков. Наиболее существенные из них:

• взаимное влияние между входами, т. к. выходной резистор R является общим для всех входов;

• необходимость в отдельном источнике смещения, что усложняет систему питания устройства.

17.5.2. Диодные логические элементы (дл)

Принцип построения схем диодных логических элементов не отличается от принципа построения логических схем на резисторах (Рис.66,б).

Применение диодов вместо резисторов обеспечивает более чёткое срабатывание схемы из – за односторонней проводимости диодов. Схемы на диодах позволяют получить положительную и отрицательную логику. Это зависит от способа включения диодов. Таблицы истинности для схем ИЛИ и И такие же как и у резистивных схем.

Логические элементы с использованием транзисторов (Рис.66 в и г)

Логические элементы с использованием транзисторов подразделяются на следующие типы схем:

• резисторно – транзисторные (РТЛ);

• диодно – транзисторные (ДТЛ);

• транзисторно – транзисторные (ТТЛ);

• на МОП – транзисторах (металл-окисел-полупроводник);

• на МДП (металл-диэлектрик-полупроводник) - полевых транзисторах.

В настоящее время широко применяются семейства логических элементов на основе ТТЛ, где широко используют биполярные и полевые транзисторы типа МДП и КМОП. В больших интегральных микросхемах преобладают МОП-структуры и сверхбыстродействующая логика, в которой основными являются элементы с эмиттерными связями (ЭСЛ).

Схемы

РЛ не применяются в логических устройствах

без дополнительных преобразователей

уровня выходного напряжения. В качестве

преобразователя служит транзисторный

ключ. На рис.66,в показана основная схема

РТЛ элемента на транзисторе р-п-р-типа.

Если к любому из входов А,В,С приложен

отпирающий сигнал (отрицательный уровень

напряжения), то транзистор отпирается

и появившийся коллекторный ток вызывает

падение напряжения на Rкол.,

в результате чего уровень выходного

напряжения будет Uвых.=

- Екол.+ Iкол.∙ Rкол..

При токе базы, большем граничного

значения ,

где β -

коэффициент усиления по току. Выходное

напряжение равно Uвых.0 = Uк.э.0.=

- Eк + Iк.нас Rк .

Пока транзистор насыщен, выходное напряжение поддерживается относительно постоянным, практически не зависящим от управляющего тока базы. В этих условиях подача отпирающего сигнала на другие входы приводит только к увеличению степени насыщения транзистора, а уровень выходного напряжения изменяется незначительно.

При отрицательной логике Uвых.0 = Uк.э.0 можно принять за уровень логического нуля. Зона разброса Uвых.0незначительная и слабо зависит от температуры.

Если

на все входы одновременно подать сигнал

логического нуля, то эмиттерный переход

транзистора смещается в прямом направлении

напряжением Uк.э.0. Однако,

поскольку напряжение между коллектором

и эмиттером насыщенного транзистора

достаточно мало (для кремниевых

транзисторов Uк.э.0.=0,2-0,3В),

то этот уровень входного сигнала вызовет

незначительный коллекторный ток

закрытого транзистора Iк.э. В

результате выходное напряжение возрастает

и режиме ХХ будет равно .

Обычно выход логического элемента управляет определённым числом входов других логических элементов, т. е. черезRk , кроме тока Iк.зак., проходит ток нагрузки Iнагр., который снижает уровень выходного напряжения относительноUвых.хх до значения Uвых.нагр.= - Ек + (Iк.закр.+ Iнагр )Rк.

При отрицательной логике напряжение Uвых.нагр. = Uвых.1. принимается за уровень логической единицы. ВеличинаUвых.1 близка к значению Ек, но меньше его. Часто для стабилизации уровня Uвых.1.и повышения быстродействия транзисторных схем применяют фиксирующие диоды. На рис.66, г показана схема, в которой коллектор транзистора соединён с катодом диода VD. Потенциал анода определяется напряжением смещения Ед. см., величина которого меньше Еk..Таким образом, потенциал коллектора закрытого транзистора устанавливается приблизительно равным – Ед.смещ., независимо от нагрузки.

Источник смещения Есм. и резистор Rб.2. в цепи базы обеспечивают надёжное запирание транзистора, когда на выходы А,В,С подаётся напряжение логического нуля (Uк.э.0). Кроме того, наличие цепи смещения Есм. ─ Rб.2 создаёт запирающий ток и тем самым уменьшает длительность времени запирания транзистора.

2,2 В группу пассивных элементов входят: резисторные логические элементы (РЛ) и диодные логические элементы (ДЛ).

2 ,3-4 58 В цифровых устройствах и в ЭВМ взаимодействие элементов и узлов, формирование и передача информации осуществляется, как правило, с помощью сигналов, принимающих только два значения: значение близкое к напряжению питания элемента схемы или близкое к нулевому значению напряжения.

Таким образом работу цифровой системы можно описать с помощью двузначных функций, которые так же как и их аргументы принимают только два значения 0 или 1.

Такие функции называются переключательными или булевыми по имени ирландца Джорджа Буля, разработавшего для таких переменных и функций дискретную алгебру, названную булевой.

Для реализации основных логических функций и осуществления передачи информации между запоминающими устройствами применяются различные типы логических схем. Система логических элементов, применяемых в цифровых устройствах, должна удовлетворять двум основным требованиям:

элементы системы должны обеспечивать выполнение основных логических функций, образующих логически полную систему;

соединение между элементами должно осуществляться наиболее простым способом, позволяя создавать схемы, в которых возможно непосредственное соединение элементов между собой.

Все логические элементы цифровых устройств можно разделить на пассивные и активные.

В группу пассивных элементов входят: резисторные логические элементы (РЛ) и диодные логические элементы (ДЛ).

Группа активных логических элементов включает:

- резисторно – транзисторные логические элементы (РТЛ);

- диодно – транзисторные логические элементы (ДТЛ);

- транзисторные элементы с непосредственной связью (НСТЛ);

- транзисторно – транзисторные логические элементы (ТТЛ);

В цифровых устройствах в зависимости от типа устройств применяется система положительных и отрицательных логических уровней.

При положительной системе логических уровней высокий уровень сигнала соответствует логической единице (1), а низкий уровень - логическому нулю (0). Эту систему обычно называют положительной логикой.

При отрицательной системе логических уровней высокий уровень сигнала соответствует логическому нулю (0), а низкий – логической единице (1).

Эта система условно называется отрицательной логикой.

К основным характеристикам логического элемента, определяющим его логические возможности, относятся коэффициенты разветвления по выходу и объединения по входу и быстродействие.

Коэффициент разветвления по выходу (m) показывает, какое число логических входов может быть присоединено к выходу данного логического элемента, а коэффициент объединения по входу (n) показывает, какое число логических входов может иметь данный элемент.

Под быстродействием логического элемента понимают среднее время задержки распространения сигнала, определяемое формулой:

, где tз.ф.-

время задержки фронта импульса; tз.с.-

время задержки спада выходного импульса

относительно спада входного импульса.

, где tз.ф.-

время задержки фронта импульса; tз.с.-

время задержки спада выходного импульса

относительно спада входного импульса.

Характеристикой, наиболее полно описывающей свойства логического элемента, является его характеристика передачи Uвых= f(Uвх). Реальные характеристики передачи логических элементов имеют пороговые зоны входного напряжения и соответствующие им зоны логической единицы и логического нуля.

Для обеспечения надёжной работы цифровых устройств обычно задают уровни максимального нуля Uo.max и минимальный уровень единицы U1.min.

2,4

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис. 1. Таблица истинности — в таблице 1.

Рис.1

Таблица 1.

|

x |

y |

x?y |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением q = x*y

(читается как "x и y").

Операция конъюнкции на функциональных схемах обозначается знаком “&”.

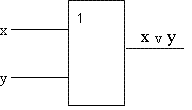

Схема ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение схемы ИЛИ представлено на рис. 2. Знак “1” на схеме — от устаревшего обозначения дизъюнкции как ">). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y

|

x |

y |

x v y |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Инверсия

или логическое

отрицание

переменной х

обозначается как

.

Значение логической переменной q

противоположно значению переменной х.

.

Значение логической переменной q

противоположно значению переменной х.

Любую логическую функцию можно представить в виде таблицы истинности. Для инверсии таблица истинности имеет следующий вид:

|

x |

|

|

0 1 |

1 0 |

Для инверсии

справедливы соотношения:

.

.

Результат двойного отрицания логической переменной равен самой логической переменной.