- •1,320 Способы включения транзисторов в схему усилителя

- •Разновидности цепей обратной связи

- •1,6 Влияние оос на свойства усилителей

- •Схемы оу

- •Применение оу

- •Схемы оу

- •1,20 Аналого – цифровые преобразователи

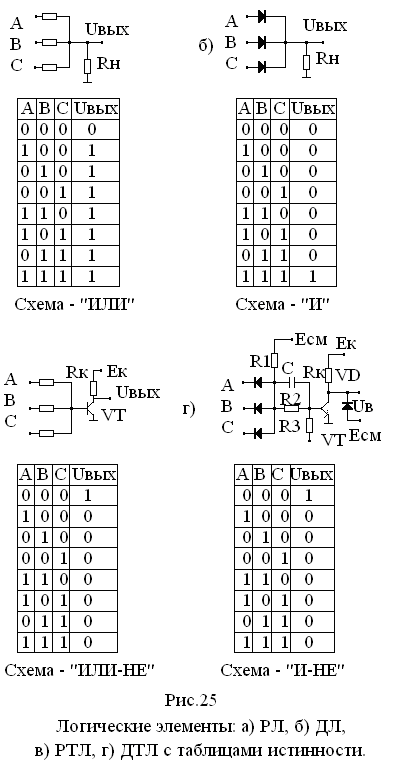

- •17.5.1Резисторные логические элементы (рл)

- •17.5.2. Диодные логические элементы (дл)

- •2,5 Логическое сложение

- •.Классификация зу

- •18.2.3. Устройства типа ерrом и еерrом

2,5 Логическое сложение

Логическое сложение, называемое функцией ИЛИ или дизъюнкцией, также имеет дело с двумя логическими переменными:

q = x + y

Таблица истинности функции ИЛИ имеет вид:

|

x |

y |

x+y |

|

0 0 1 1 |

0 1 0 1 |

0 1 1 1 |

Для функции ИЛИ справедливы соотношения:

x + 0 =x, x*x = x, x + 1 = 1,

x +

= 1

= 1

Логическое умножение

Логическое умножение, также называемое функцией И или конъюнкцией, объединяет две логические переменные:

q = x*y

Таблица истинности функции И имеет вид:

|

x |

y |

x*y |

|

0 0 1 1 |

0 1 0 1 |

0 0 0 1 |

В таблице истинности рассматриваются все четыре возможные комбинации значений двух логических переменных.

Для функции И справедливы соотношения:

x*0

= 0, x*x

= x,

x*1

= x,

.

.

2,7

ДТЛ элементы представляют собой дальнейшее развитие ДЛ и РТЛ элементовВ диодных элементах имеет место потеря напряжения, которая возрастает по мере увеличения числа ступеней ДЛ элементов. Поэтому включение транзисторного усилительного каскада на выходе каждого ДЛ элемента является естественным. Этим обеспечивается электрическая развязка входа от выхода, увеличение коэффициента управления и формирование необходимой величины уровня выходного напряжения. Обычно для этих целей применяется транзисторный усилитель – инвертор, реализующий функцию «И – НЕ» и «ИЛИ – НЕ».

На рис.20,г показана схема ДТЛ элементов. Резисторы R1, R2, R3 образуют делитель напряжения. Для схемы ДТЛ элемента «ИЛИ – НЕ» сопротивления резисторов выбираются так, чтобы при подаче на один или более входов А,В или С отпирающего (низкого) уровня сигнала, соответствующего логической единице , транзистор был открыт , а при подаче одновременно на все входы А,В и С запирающего (высокого) уровня сигнала, соответствующего логическому нулю, транзистор был закрыт. В ряде устройств R3 можно исключить.

Сопротивления резисторов R1, R2, R3 для схемы ДТЛ элемента «И – НЕ» выбирается так, чтобы , когда на все входы одновременно подаётся сигнал логической единицы (при отрицательной логике логической единице соответствует низкий уровень напряжения), на базе транзистора устанавливается потенциал, достаточный для его насыщения.

Если на любой из входов подать напряжение логического нуля (высокий уровень напряжения), то диод этого входа окажется открытым , а остальные диоды закрыты, и со входа на базу транзистора пройдёт положительный сигнал, который вызовет его запирание. Коллекторный потенциал закрытого транзистора понизится до уровня –Ед.см., после чего откроется фиксирующий диод и снижение потенциала коллектора прекратится.

Уровень –Ед.см. соответствует логической единице. Конденсатор С в схеме рис.25,г выполняет роль ускоряющего элемента. Благодаря наличию этого конденсатора ток базы в первый момент после коммутации имеет выброс , что и ускоряет процесс переключения транзистора. Однако, при выборе номинала ёмкости конденсатора необходимо учитывать, что увеличение отпирающего тока базы сопровождается увеличением накопленного на базе заряда и, следовательно, приводит к увеличению длительности задержки при выключении транзистора.

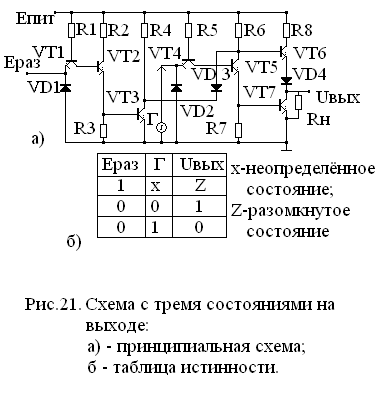

Входным элементом схемы ТТЛ (Рис.21) является многоэмиттерный транзистор, который представляет собой интегральный элемент, объединяющий преимущества диодных логических схем и транзисторного усилителя. Когда эмиттеры с обычной базой представляются в виде нескольких диодов и переход К-Б представляется также диодом.

При высоком пороговом уровне напряжения (лог.1) на эмиттерах А,В происходит закрывание диодов Б-К транзистора VT1. При этом VT2 управляется через переход Б-К VT1 и R1, и находится в открытом состоянии. В результате: VT4 также управляется по базе, а VT3 – запирается. Выходное напряжение этой ТТЛ-схемы при полностью открытом VT4 и закрытом VT3 соответствует низкому уровню (лог.0). Таким образом, когда на все входы А и В подано высокое пороговое напряжение (лог.1), то на выходе схемы появляется напряжение низкого уровня (лог.0). Схема работает как логический элемент И-НЕ.

Если на входы А и

В транзистора VT1

подать низкий уровень напряжения

(лог.0), то входные диоды Б – К открываются

и потенциал коллектора VT1

уменьшится (VT1-откроется),

при этом уменьшается потенциал базы

VT2

также уменьшится и он закрывается. При

этом потенциал базы VT3

возрастает и транзистор открывается.

Одновременно, при закрытом VT2,

уменьшается потенциал базы VT4

и он закрывается. Потенциал на выходе

схемы возрастает, т. е. появляется

логическая единица (лог.1), схема работает

как логический элемент ИЛИ – НЕ

2,8

|

Базовый логический элемент ТТЛШ. В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29,а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29,6. Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. Транзистор VT4 — обычный биполярный транзистор. |

|

Если оба входных напряжения Uвх1 и Uвх2 имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня.

2,9 Получается структура, состоящая из металла, диэлектрика и полупроводника. Поэтому полевые транзисторы с изолированным затвором часто называют МДП-транзисторами. Полевые транзисторы с МДП- структурой наиболее перспективны для БИС и СБИС. Различают МДП-транзисторы с каналами двух типов проводимости: р-типа и п-типа. МДП-транзисторы р-типа открываются при отрицательном смещении затвора относительно истока, а МДП-транзисторы n-типа открываются при положительном смещении затвора относительно истока.

Логические схемы на основе МДП-транзисторов р-типа с заземлённым истоком требуют отрицательного напряжения питания (схемы отрицательной логики), а МДП- транзисторы n-типа – положительного напряжения питания (положительная логика). Для создания схем как положительной, так и отрицательной логики используют дополняющие МДП-транзисторы с каналами p- и n- типов (МДПДТ). Для схем на дополняющих МДП-транзисторах полярность логики зависит от последовательности включения р- и n- транзисторов. Если транзистор n-типа непосредственно подключён к земле, а транзистор р-типа – к источнику питания , то схема работает в режиме положительной логики («1» - +Е, «0» - 0). При непосредственном подключении к земле транзистора р-типа , а транзистора n-типа – к источнику питания, схема работает в режиме отрицательной логики («1» - -Е, «0» - 0).

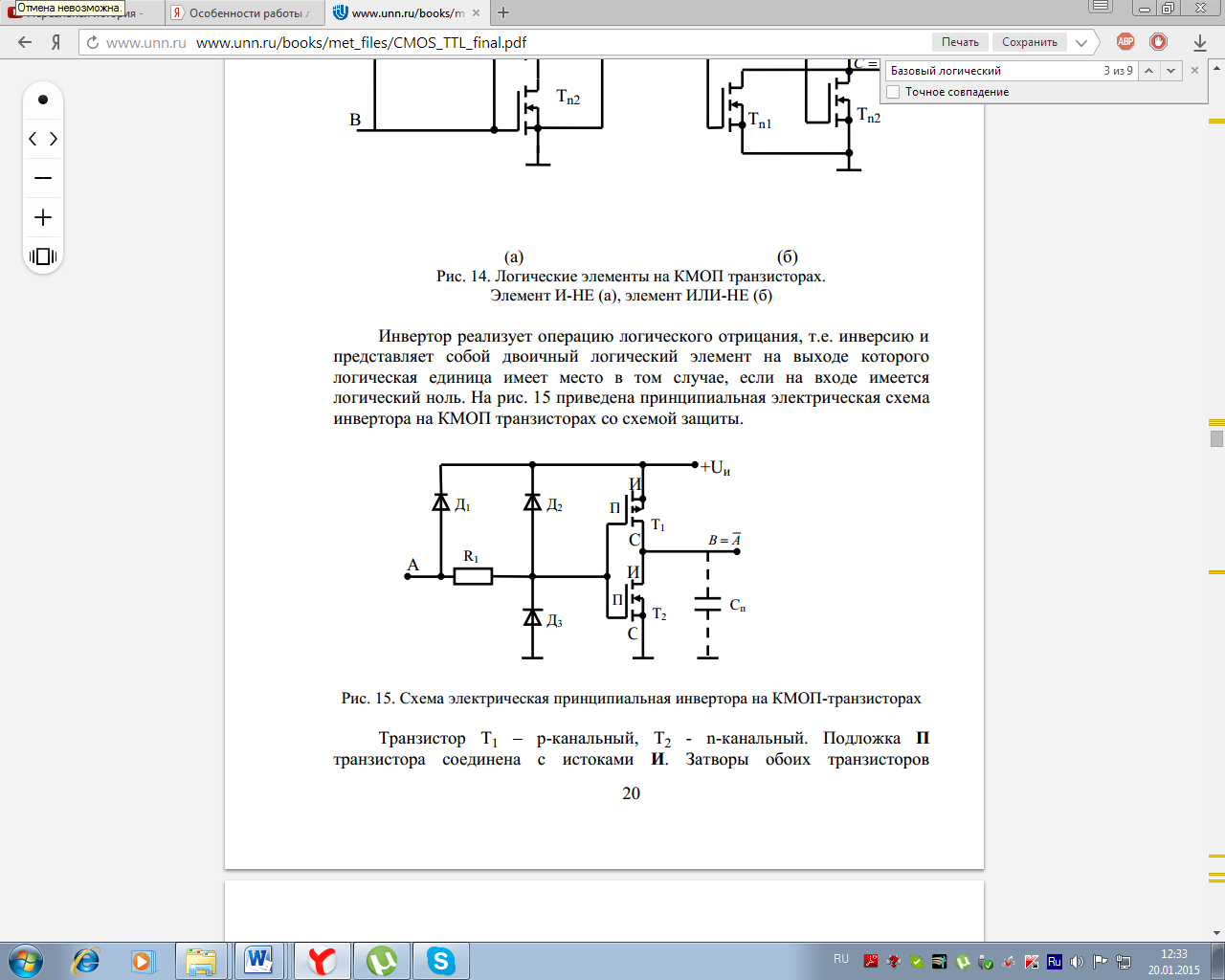

2,10Базовый логический элемент на КМОП-транзисторах. Устройство и принцип действия Цифровые интегральные микросхемы на КМОП (комплементарная пара МОП-транизисторов) транзисторах считаются наиболее перспективными, поскольку мощность, потребляемая в статическом, режиме у них составляет десятки нановатт при высоком быстродействии. Среди цифровых ИМС на МОП транзисторах интегральные микросхемы на КМОП транзисторах обладают наибольшей помехоустойчивостью и высокой эффективностью использования источника питания. Основными логическими элементами серий на КМОП транзисторах являются элементы И-НЕ; ИЛИ-НЕ (рис.14 а, б), а базовым логическим элементом, на основе которого реализованы указанные элементы, является инвертор (элемент НЕ) на КМОП транзисторах.20 (а) (б

Рис. 14. Логические элементы на КМОП транзисторах. Элемент И-НЕ (а), элемент ИЛИ-НЕ (б) Инвертор реализует операцию логического отрицания, т.е. инверсию и представляет собой двоичный логический элемент на выходе которого логическая единица имеет место в том случае, если на входе имеется логический ноль. На рис. 15 приведена принципиальная электрическая схема инвертора на КМОП транзисторах со схемой защиты. Рис. 15. Схема электрическая принципиальная инвертора на КМОП-транзисторах Транзистор Τ1 – p-канальный, Τ2 - n-канальный. Подложка П транзистора соединена с истоками И. Выходной сигнал снимается с объединенных стоков транзисторов.

2,15

S – вход для установки ( Set – установка ) триггера в состояние «1» т.е. Q = 1;

R – вход сброса ( Reset – сброс, возврат ) триггера в состояние «0» т. е. Q =0;

D – вход для установки триггера в состояние «1» при D = 1, или в состояние «0» при D = 0 c задержкой ( Delay – задержка ) переключения входов

по отношению ко входуD;

по отношению ко входуD;Т – вход переключения ( Toggle – релаксатор ) триггера в противоположное состояние анологично счёту по модулю 2, поэтому вход Т называют счётным;

J, K – входы для установки ( Jerk – включение ) и сброса ( Kill - отключение ) триггера в состояния соответственно «1» и «0» аналогично входам S и R ; отличие состоит в том, что одновременное возбуждение входов S и R обусловливает неопределённость перехода триггера в одно из двух возможных состояний, а одновременное возбуждение входов J и К вызывает однозначно смену состояния триггера аналогично входу Т;

С – вход синхронизации ( Clock – часы ) для точного задания моментов переключения состояний триггера;

V – вход для разрешений или запрета реагирования триггера на соответствующие управляющие входы.

Обычно триггеры содержат лишь часть из перечисленных типов входов, причём некоторые из них являются кратными, По совокупности управляющих входов различают:

RS – триггеры с раздельными входами установки в состояние «0» и «1»;

RS – триггеры бывают асинхронные и синхронные, если кроме S и R имеется вход С;

D – триггеры с записью информации по одному входу D в моменты времени , определяемые синхроимпульсами С;

Т – триггеры со счётным входом;

JK – триггеры – универсальные триггеры , в которых входы J и K в отдельности реализуют раздельное управление, а совместно – счётный режим.

Кроме названных типов существует много разновидностей типов триггеров с комбинированным управлением, названными типами входов, с синхронизацией и без неё, с блокировкой каких – либо информационных входов или без неё. Триггеры, синхронизируемые уровнем синхроимпульса, могут в течение действия синхроимпульса многократно переключаться управляющими сигналами. В паузе между синхроимпульсами их состояния не изменяются независимо от управляющих сигналов.

80 RS – триггеры. В микромодульном исполнении такие триггеры могут быть выполнены на 2-х логических элементах ИЛИ-НЕ с использованием цепей обратной связи.

81 JK – триггеры. Универсальный JK-триггер – это последовательное регенеративное бистабильное устройство с 2-мя информационными входами J и K, которые в случае входной комбинации J=K=1 переключают триггер в противоположное состояние подобно Т-триггеру (Рис.25,б). При любых других комбинациях импульсов на входах J и K триггер работает как RS-триггер, у которого роль входов S и R выполняют соответственно входы J и K.

Триггер может работать в асинхронном режиме, когда смена состояния триггера происходит строго под влиянием установочных сигналов, и в синхронном режиме, когда смена значений установочных сигналов произошла, но смена состояний выхода триггера происходит в строго определённые моменты прихода импульсов синхронизации.

Для обеспечения счётного режима работы JK-триггер по аналогии с Т-триггером должен содержать ЛЗ, или быть собранным по 2-х тактной схеме.

Приведенная схема JK-триггера имеет ограничение на длительность синхроимпульсов. Это сужает область применения однотактных JK-триггеров. Двухтактный JK-триггер не критичен к длительности управляющих и синхронизирующих импульсов.

Данный вариант JK-триггера отличается от Т-триггера тем, что элементы DD1 и DD2 имеют дополнительные входы J и K, а их общий вход используется для синхронизации.

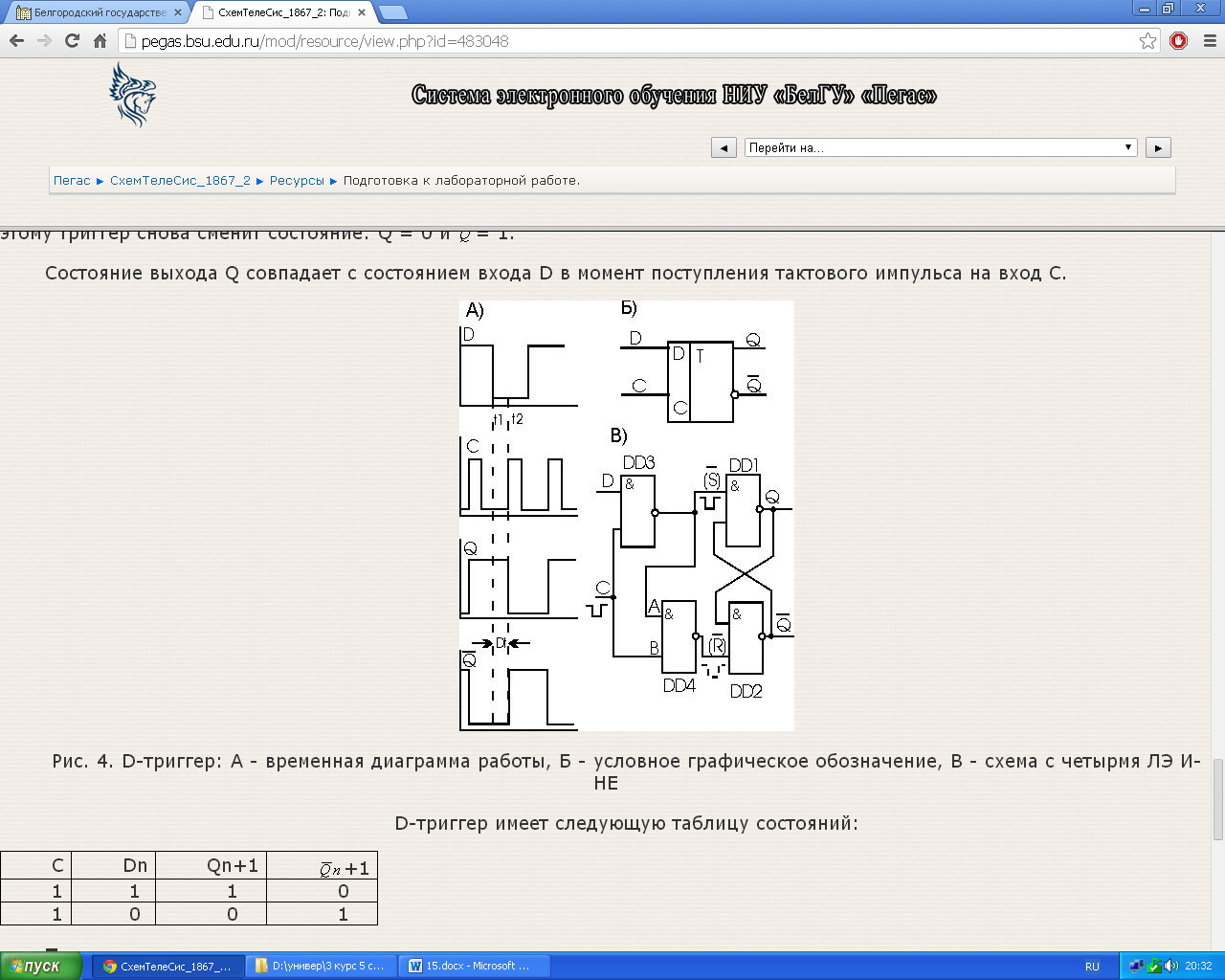

Триггер типа D - это устройство с двумя устойчивыми выходными состояниями. Сменой состояния управляют сигналы на информационном входе D (рис. 4), но переключение происходит не сразу, а с приходом тактового импульса на второй вход С. Важнейшее свойство D-триггеров в том, что, как только на вход С поступает импульс, на выходе Q устанавливается тот же уровень напряжения, который в этот момент действует на входе D, т. е. переброс триггера происходит с некоторым отставанием dt относительно смены сигнала на входе D. Поэтому D-триггеры еще называют триггерами задержки.

Триггер,

схема которого показана на рис. 4,B,

содержит четыре ЛЭ И-НЕ. Здесь DD1 и DD2

образуют знакомый -триггер.

Дополнительные элементы DD3 и DD4 превращают

его в D-триггер. Действует D-триггер

следующим образом. Если D = 1, то при

наличии тактового импульса на выходе

DD3 формируется сигнал, вид которого

показан на рис. 4,B.

Сигнал действует на

-триггер

подобно сигналу

,

и на выходе Q устанавливается напряжение

высокого уровня (Q = 1,

a

=

0). При этом на выходе DD4 напряжение

высокого уровня, так как в отсутствие

тактовых импульсов (С = 0) на входе А

действует напряжение высокого и на

входе В - низкого уровня, а с приходом

тактового импульса (С = 1) на входе A

возникает напряжение низкого, а на входе

В - высокого уровня.

Если

на вход D подано напряжение низкого

уровня, на выходе DD3 будет напряжение

высокого уровня, а тактовый импульс,

инвертированный элементом DD4, как

показано на рис, 4,B штрихами,

действует подобно сигналу .

Благодаря этому триггер снова сменит

состояние: Q = 0 и

=

1.

Состояние выхода Q совпадает с состоянием входа D в момент поступления тактового импульса на вход С.

Рис. 4. D-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырмя ЛЭ И-НЕ

D-триггер имеет следующую таблицу состояний:

|

C |

Dn |

Qn+1 |

|

|

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

2,16 может и не то Компараторы – это ОУ специального назначения, предназначенные для сравнения по уровню 2-х своих входных напряжений и скачкообразного изменения своего Uвых в тех случаях, когда одно из сравниваемых напряжений превышает другое. В качестве компаратора можно использовать любой ОУ, но на практике предпочтение отдаётся специально созданным компараторам.

ОУ очень удобны для создания компараторов, так как имеют по два входа.

Компараторы – это ОУ специального назначения, предназначенные для сравнения по уровню двух своих входных напряжений и скачкообразного изменения своего выходного напряжения в тех случаях, когда одно из сравниваемых напряжений превышает другое. В качестве компаратора в принципе может быть использован любой ОУ, но на практике предпочтение отдается специально созданным компараторам (обычно в твердотельном и гибридном исполнении).

У компаратора должны быть небольшими напряжения сдвига, дрейф напряжения сдвига и значение тока смещения. Он должен устойчиво работать без самовозбуждения.

Компараторы могут работать как от одного, так и от биполярного источника питания.

Принцип работы компаратора можно пояснить рисунком 3.19,а,б, на котором изображены компаратор в виде ОУ с одним источником питания и временные диаграммы напряжений на его входах и выходе.

На один вход компаратора подается входной сигнал uвх, на другой - опорное напряжение uоп. В зависимости от соотношения уровней uвх и uоп компаратор меняет свое состояние и уровень выходного напряжения. При uвх > uоп выходное напряжение будет малым (см. на рис.3.19,б,в интервалы времени от 0 до t1, от t2 до t3 и после t4), а при uвх < uоп– большим (см. на рис.3.19,б,в интервалы времени от t1 до t2 и t3 до t4), поскольку uвх подается на инвертирующий вход (отметим, что для получения большого uвых при uвх > uоп, нужно подавать uвх на неинвертирующий вход, а uоп на инвертирующий вход).

Результат сравнения

двух напряжений может быть обеспечен

с высокой точностью. Это можно показать

на примере. Пусть, например, перепад

выходного напряжения будет 10 В, а

коэффициент усиления ОУ ![]() раз.

Тогда период между uвх и

uоп,

вызывающий изменение выходного

напряжения, составим

раз.

Тогда период между uвх и

uоп,

вызывающий изменение выходного

напряжения, составим ![]() В

= 1мВ. При опорном напряжении, например,

10 В, относительная погрешность компаратора

будет

В

= 1мВ. При опорном напряжении, например,

10 В, относительная погрешность компаратора

будет

![]()

Здесь разность (uвх - uоп) умножается на два, потому что изменение выходного напряжения происходит тогда, когда входной сигнал больше или меньше uоп на 1 мВ.

При питании компаратора от биполярного источника питания уровни выходного напряжения изменяются от отрицательного наибольшего значения до положительного наибольшего значения (например, в триггерах).

В заключение этой главы отметим, что рассмотренные в ней многочисленные примеры применения ОУ являются лишь очень малой частью возможных схем применения ОУ, приведенных в специальной литературе по ОУ. Все эти применения ОУ свидетельствуют о том, что ОУ является универсальными, многофункциональными усилителями, основой элементной базы современной аналоговой электроники.

Компараторы (схемы сравнения) предназначены для сравнения 2-х чисел А и В с выработкой выходных сигналов, соответствующих случаям когда А=В или А ≠ В (Рис.26). Для одного разряда числа функция, реализуемая схемой сравнения, задаётся таблицей истинности, которая определяет функцию равнозначности (ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией) и реализуется, например, элементом И-ИЛИ-НЕ.

Если на схему подать сигналы А и С одного уровня, то один из входов элемента ИЛИ-НЕ получает сигналы высокого уровня. Если А и С различны, то на оба входа элемента ИЛИ-НЕ подаётся сигнал низкого уровня. Т. к. элемент ИЛИ-НЕ по отношению к сигналу низкого уровня реализует функцию И-НЕ, то уровень сигнала на выходе низкий.

Схема сравнения представляет собой соединение схем ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, каждая из которых сравнивает содержимое двух разрядов.

Имеется несколько вариантов сравнения кодов. Наиболее простой способ основан на применении сумматора сравниваемых кодов А и С. На сумматоре выполняется операция вычитания А – С и анализируется результат.

2,17 Регистром называется устройство, предназначенное для кратковременного запоминания слова и выполнения над словом некоторых логических действий (Рис.27). Регистр представляет собой совокупность триггеров, число которых соответствует количеству разрядов в слове, и вспомогательных схем, которые обеспечивают:

установку регистра в ноль (сброс);

приём слова из другого устройства (регистра, сумматора, ЗУ и т. д.);

передачу слова в другое устройство;

преобразование кода числа (из прямого в обратный и наоборот);

сдвиг слова влево или вправо на требуемое число разрядов;

преобразование последовательного кода в параллельный и наоборот;

логическое сложение и умножение;

поразрядное сложение.

Регистры выпускаются не только в виде однословных триггеров, но и в виде сгруппированных многоразрядных блоков – в виде регистровых файлов.

Различают синхронные и асинхронные регистры. Отдельную группу регистров составляют сдвиговые регистры, в которых осуществляется сдвиг содержимого разрядов регистра. В таком регистре содержимое разрядов под действием тактирующих сдвигающих импульсов может сдвигаться в сторону старших или младших разрядов.

По характеру приёма и передачи информации сдвиговые регистры делятся на:

регистр с последовательным входом и последовательным выходом, при этом данные на вход и с выхода регистра поступают последовательно бит за битом;

регистр с последовательным входом и параллельным выходом, при этом регистр загружается последовательно бит за битом, а результат, хранящийся во всех триггерах считывается одновременно;

регистр с параллельным входом и последовательным выходом, при этом все триггеры загружаются одновременно, а результат, хранящихся в регистре данных, в необходимое время считывается последовательно бит за битом под действием тактовых импульсов;

регистры с параллельным входом и параллельным выходом, при этом все триггеры в регистре загружаются одновременно и все данные, записанные в регистр, считываются одновременно.

Сдвиговые регистры выполняются на синхронных D-триггерах и RS, JK-триггерах в режиме D-триггера.

2,18 Счётчики импульсов

Счётчиком называется последовательная схема, выполняющая функции подсчёта количества единичных сигналов, поступивших на её вход, а также функции формирования и запоминания некоторого кода, соответствующего этому количеству сигналов (Рис.28). Счётчики можно классифицировать по функциональному признаку и по способу записи информации в счётчик..

Простые счётчики могут вести счёт только в одном направлении, или прибавлять входные сигналы к коду, сформированному в счётчике, или вычитать входные сигналы из этого кода.

Реверсивные ведут счёт и в прямом и обратном направлениях.

Счётчики, переключение которых происходит в строго заданные моменты времени от синхроимпульсов называются синхронными.

Счётчики, для переключения которых достаточно передавать лишь входные сигналы в произвольные моменты времени называются асинхронными.

Счётчики, модуль которых М равен целой степени числа 2, являются двоичными счётчиками.

Счётчики с модулем пересчёта не равным 2(М=10 в десятичной системе, М=60, 24 в часах) относятся к пересчётным схемам.

Основными характеристиками счётчиков являются:

Модуль М пересчёта счётчика, характеризующий предельное число импульсов, которое может быть сосчитано счётчиком.

Быстродействие счётчика, которое характеризуется временем регистрации счётчика – интервалом времени между моментом поступления входного сигнала и окончанием самого длинного переходного процесса (моментом установившегося значения слова на выходе счётчика) tреч.

Разрешающая способность счётчика – это минимально допустимый период следования входных сигналов, при котором счётчик работает без сбоев tсчёта..

Разрешающая способность зависит от динамических свойств триггера в раз-ряде с самым малым весом. Время регистрации определяется типом используемых триггеров и организацией межразрядных связей.

Связи между триггерами, обеспечивающие их переключение и влияющие на быстродействие работы счётчика, бывают непосредственные, последовательного (сквозного) переноса, параллельного и параллельно – группового переноса.

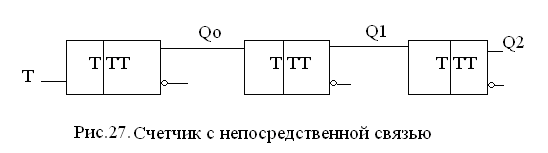

Простейшие двоичные счётчики с непосредственной связью строят чаще всего на основе Т-триггеров, каждый из которых является счётчиком с модулем М = 2 (делитель частоты на 2).

Двоичный n- разрядный счётчик содержит n Т-триггеров и его модуль М = 2n. В счётчике с непосредственной связью выход предыдущего триггера является входом последующего. В таком n- разрядном счётчике переключение происходит последовательно триггер за триггером и задержка распространения в счётчике для самого худшего случая, смены всех единиц на все нули, в n- раз больше задержки распространения сигнала в одном Т - триггере. Такие счётчики бывают только асинхронными, т. к. осуществить смену состояния всех триггеров в один момент времени невозможно. Примером счётчика с непосредственными связями является микросхема 155ИЕ(7493).

2, 19

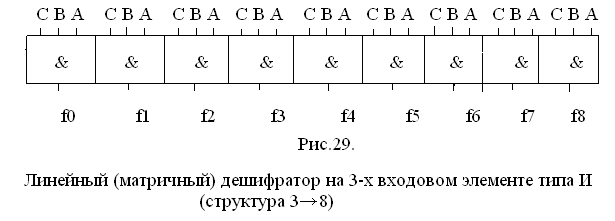

Шифратором называется логическая схема, осуществляющая преобразование распределительного (унитарного) двоичного в позиционный двоичный код (Рис.29). Шифратор выполняет функцию, обратную дешифратору. Шифратор имеет т входов и n выходов, связанных соотношением т = 2n (восьмиразрядному распределительному коду т = 8 соответствует трёхразрядный позиционный двоичный код n = 3). Сигнал поступает строго на один из входов шифратора, на выходе которого при этом формируется двоичный код, соответствующий номеру входа, на который подан входной сигнал.

Для того, чтобы допустить возможность появления нескольких сигналов на входе шифратора входные сигналы пропускают через схему выделения старшей единицы. Эта схема пропускает все старшие нули и старшую единицу входного кода на свой выход (вход шифратора) без изменения, а все разряды более младшие, чем разряд старшей единицы обнуляются. Для трёхразрядного кода ( а2 , а1 , а0 , где а2 – старший разряд) возможна схема

Шифратор с такой схемой на входе называется приоритетным шифратором. Примером такого шифратора является микросхема ИМС555ИВ1.

Дешифраторы

Дешифратором называется кодирующее устройство, преобразующее входной позиционный двоичный код в выходной распределительный (унитарный) код, имеющий активный уровень только в одном разряде (на одном выходе), а именно в том, номер которого в двоичном счислении равен входному двоичному числу (Рис.30).

Дешифраторы служат для преобразования кода слова, находящегося в регистре (счётчике) в управляющий сигнал на одном из выходов, число которых равно 2 п. Дешифратор имеет п прямых и п инверсных входов.

Схемы дешифраторов строят различным способом в зависимости от формата дешифруемого слова и особенностей применяемой системы элементов. По способам построения дешифраторы подразделяют на линейные, прямоугольные и пирамидальные. Схемы дешифраторов сравнивают по быстродействию и аппаратным затратам. Быстродействие определяется величиной, обратной времени задержки в логическом элементе на число каскадов k дешифратора.

Для линейного однокаскадного дешифратора (k = 1) число вентилей И равно 2 п. Каскадное включение вентилей И можно осуществить двумя способами, которые и делят дешифраторы на прямоугольные и пирамидальные.

В прямоугольном дешифраторе формат входного слова разбивается на слога и для каждого слога на линейном дешифраторе образуются все выходные значения, которые называются частичными. Группа линейных дешифраторов, равная числу слогов, представляет первый каскад прямоугольного дешифратора. В любом последующем каскаде выполняется операция конъюнкции (логическое умножение) частичных выходных значений, образованных линейными дешифраторами предыдущего каскада.

Схема пирамидального дешифратора в каждом своём каскаде образует частичные выходные значения как конъюнкции частичных выходных значений и цифры одного из разрядов, не участвовавших в образовании предыдущих значений, Число каскадов равно разрядности входного слова: п = k.

Выбор того или иного типа дешифратора определяется конкретным требованием к нему и особенностями системы элементов, на которых строится дешифратор. Если система элементов содержит только стандартный элемент И-НЕ, то количество элементов в дешифраторе увеличивается вследствие необходимости дополнительной инверсии на выходах каждого каскада. Полный дешифратор с п входами имеет т выходов, где т = 2п - число возможных сочетаний из п переменных

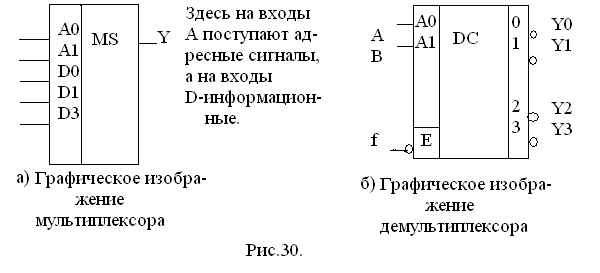

2,20 Мультиплексоры демультиплексоры

Мультиплексор – это кодирующее устройство, осуществляющее подключение (коммутацию) одного из нескольких входов данных Di к выходу (Рис.31,а). Номер выбранного входа соответствует коду, поданному на адресные входы Аi мультиплексора. Определённый канал (источник данных) выбирается заданием двоичного числа на адресных входах. В большинстве случаев вводят дополнительный стробирующий вход, который разрешает передачу данных в момент выборки.

Механическим аналогом мультиплексора является многополюсный переключатель, ось которого устанавливается в требуемую позицию ручкой.

Мультиплексоры 4 → 1 (четыре входа в один выход), 8 → 1, 16 → 1 выпускаются в составе многих серий и имеют код КП (например К155КП7).

Мультиплексор позволяет осуществлять передачу цифровых сигналов от нескольких источников в единственный последовательный канал передачи сигналов, пропускать на выход прямой или обратный код двоичного числа, коммутировать прямые и инверсные выходы счётчика для формирования реверсивного счёта импульсов.

Демультиплексоры

Демультиплексоры выполняют операцию обратную мультиплексированию, т. е. они распределяют порции данных, поступающих в последовательные моменты времени по своим приёмным каналам (Рис.31,б).

В роли демультиплексора может выступать дешифратор, имеющий вход разрешения. Если к этому входу подключить мультиплексированную магистраль, а приёмники к выходам дешифратора и в заданные моменты времени подавать соответствующие выходам (приёмникам) адресные коды, то на выходах дешифратора будет проходить информация, адресованная приёмникам сигналов

2,21 Классификация запоминающих устройств, их разновидности.

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими частями микропроцессорных систем.

Каждое ЗУ характеризуется набором адресов и содержимым ячеек памяти. Обратившись к ЗУ по тому ли иному адресу, узнают содержание соответствующей ячейки памяти, которая может содержать либо единственный бит, либо несколько бит информации.

По функциональному назначению ЗУ подразделяются на внешние, буферные и внутренние. Внешние ЗУ служат для хранения больших объёмов информации и программного обеспечения системы. Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью. Внутренние ЗУ по выполняемым функциям делятся на оперативные и постоянные. Оперативные ЗУ (ОЗУ) выполняют запись, хранение и считывание произвольной двоичной информации, обеспечивают хранение программ для текущей обработки информации и массивов обрабатываемых данных. Постоянные ЗУ (ПЗУ) осуществляют хранение и выдачу постоянно записанной информации, содержание которой не изменяется во время работы системы. Это используемые в процессе работы стандартные подпрограммы и микропрограммы, табличные значения различных функций, константы и др.

По способу хранения информации ОЗУ делят на статические и динамические. Запоминающие элементы (ЗЭ) статических ЗУ представляют собой бистабильные элементы и обеспечивают считывание информации без её разрушения. В динамических ЗУ для хранения информации используются инерционные свойства конденсаторов, что требует периодического восстановления (регенерации) состояния ЗЭ памяти в процессе хранения информации. При регенерации производится перезапись каждого хранимого в ЗУ бита либо в тот же ЗЭ, либо в соседний; в последнем случае информация циклически сдвигается на один разряд с каждым циклом регенерации.

Основными параметрами ЗУ являются: информационная ёмкость М и быстродействие. Информационная ёмкость характеризует количество информации, которая может храниться в ЗЭ на кристалле, и определяется в битах или количеством слов N с указанием их разрядности п; М = п*N, где п – разрядность слова (п = 0,1,2,3,***); N = 2m (m = 4,5,6,***) – количество слов.

Быстродействие характеризуется временем выборки и циклом записи. Время выборки tв - интервал времени между моментом подачи сигнала выборки и появлением информации на выходе микросхемы ЗУ. Цикл записи tц.з.- минимально допустимое время между моментом подачи сигнала выборки при записи и моментом начала последующей операции считывания (записи).