- •«Теория дискретных устройств автоматики и телемеханики»

- •Синтез логического автомата

- •Исходные данные

- •Задание

- •Оформление курсовой работы

- •1. Краткие теоретические сведения

- •1.1. Основные логические операции

- •1.2. Способы записи функций алгебры логики (фал)

- •1.3. Логические элементы

- •1.4. Принцип двойственности

- •1.5. Теоремы алгебры логики

- •1.6. Комбинационные логические устройства (логические автоматы)

- •1.7. Минимизация фал методом карт Вейча-Карно

- •1.8. Построение схемы логического автомата на электромагнитных реле

- •1.9. Построение схемы логического автомата на диодной матрице

- •1.10. Построение схемы логического автомата на микросхемах заданной серии

- •2. Порядок выполнения курсовоЙ работы

- •Вопросы для защиты курсовой работы

- •Библиографический список

1.10. Построение схемы логического автомата на микросхемах заданной серии

При построении схемы логического автомата на микросхемах заданной серии необходимо определить количество корпусов микросхем, указать, к каким выводам («ножкам») корпусов подключаются входные переменные, и с каких выводов снимаются выходные сигналы.

М икросхемы

логики И-НЕ, ИЛИ-НЕ выполнены в стандартном

корпусе с 14-ю выводами. Вид корпуса

представлен на рис. 14.

икросхемы

логики И-НЕ, ИЛИ-НЕ выполнены в стандартном

корпусе с 14-ю выводами. Вид корпуса

представлен на рис. 14.

Рис. 14. Внешний вид стандартного корпуса логических микросхем

На вывод 14 подаётся питание +U, вывод 7 – общий провод питания (минус). Таким образом, для логических элементов остаётся 12 выводов. На 12 выводах могут разместиться 4 элемента 2И-НЕ (2ИЛИ-НЕ), 3 элемента 3И-НЕ (3ИЛИ-НЕ), 2 элемента 4И-НЕ (4ИЛИ-НЕ) или 1 элемент 8И-НЕ.

При использовании реальных микросхем может возникнуть одна из двух ситуаций:

-число входов логического элемента больше числа переменных, входящих в уравнение ФАЛ;

-число входов логического элемента меньше числа переменных, входящих в уравнение ФАЛ.

В первом случае «лишние» входы устраняются

объединением входов. Пример объединения

представлен на рис. 15.

первом случае «лишние» входы устраняются

объединением входов. Пример объединения

представлен на рис. 15.

Рис. 15. Пример объединения входов логического элемента для согласования их числа с числом входных переменных и для преобразования логического элемента в инвертор

Аналогичные объединения входов можно делать и для элементов ИЛИ-НЕ.

В о

втором случае придётся преобразовывать

схему, чтобы сохранить порядок действий

в уравнении ФАЛ. Рассмотрим случай

преобразования схемы для получения на

элементах 2И-НЕ схем 3И-НЕ и 4И-НЕ.

о

втором случае придётся преобразовывать

схему, чтобы сохранить порядок действий

в уравнении ФАЛ. Рассмотрим случай

преобразования схемы для получения на

элементах 2И-НЕ схем 3И-НЕ и 4И-НЕ.

Рис. 16. Схема для образования действия 3И-НЕ на элементах 2И-НЕ

В

схеме сначала выполняется действие над

переменными Х2 и Х1. На выходе элемента

2И-НЕ получается инверсия произведения

![]() .

Этот сигнал инвертируется на втором

элементе 2И-НЕ, превращённом в инвертор

объединением входов. На третьем элементе

2И-НЕ полученное логическое произведение

дополнительно умножается на Х0. В итоге

получается

.

Этот сигнал инвертируется на втором

элементе 2И-НЕ, превращённом в инвертор

объединением входов. На третьем элементе

2И-НЕ полученное логическое произведение

дополнительно умножается на Х0. В итоге

получается![]() к

к ак

на элементе 3И-НЕ.

ак

на элементе 3И-НЕ.

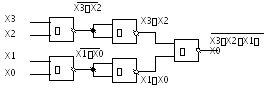

Рис. 17. Схема для образования действия 4И-НЕ на элементах 2И-НЕ

В

схеме сначала выполняются действия над

переменными Х3 и Х2, Х1и Х0. На выходе

первого элемента 2И-НЕ получается

инверсия произведения

![]() ,

а второго -

,

а второго -![]() .

Эти сигналы инвертируются на третьем

и четвёртом элементах 2И-НЕ, превращённых

в инверторы объединением входов. На

пятом элементе 2И-НЕ полученные логические

произведения дополнительно перемножаются.

В итоге получается

.

Эти сигналы инвертируются на третьем

и четвёртом элементах 2И-НЕ, превращённых

в инверторы объединением входов. На

пятом элементе 2И-НЕ полученные логические

произведения дополнительно перемножаются.

В итоге получается![]() как на элементе 4И-НЕ.

как на элементе 4И-НЕ.

Аналогичные схемы можно построить для элементов 2ИЛИ-НЕ, чтобы получить действия 3ИЛИ-НЕ и 4ИЛИ-НЕ.

Для пояснения процесса построения схемы логического автомата на заданных типах микросхем рассмотрим пример ФАЛ выражения (1.4):

![]() .

.

Составим структурную схему логического автомата (рис. 18).

На

схеме соблюдается принятый порядок

действий. Сначала производится инверсия

входных переменных Х3, Х2, Х1 и Х0. В

результате формируются вертикальные

шины переменных

![]() и

и![]() (всего 8 шин), к которым подключаются

логические элементы.

(всего 8 шин), к которым подключаются

логические элементы.

Теперь выполняются действия в скобках – во втором слагаемом уравнения в скобках производится сложение, в третьем – сначала умножение, а потом сложение.

Затем производится умножение в первом элементарном логическом произведении, а также во втором и третьем результаты действий в скобках логически перемножаются с переменными, стоящими вне скобок.

Производится логическое сложение полученных выражений, что даёт результат Y.

По структурной схеме логического автомата легко можно получить схему на заданных типах микросхем. Предположим, что заданы микросхемы К155ЛА3 (4 элемента 2И-НЕ) и К155ЛЕ4 (3 элемента 3ИЛИ-НЕ).

Принципиальная электрическая схема логического автомата на микросхемах К155ЛА3 представлена на рис. 19.

Построение

схемы начинается с формирования шин

входных переменных

![]() и

и![]() ,

для чего элементы 2И-НЕ превращаются в

инверторы. Всего потребуется четыре

инвертора, следовательно, один корпус

будет использован полностью.

,

для чего элементы 2И-НЕ превращаются в

инверторы. Всего потребуется четыре

инвертора, следовательно, один корпус

будет использован полностью.

Р ис.

18. Структурная схема логического автомата

по уравнению ФАЛ (1.4)

ис.

18. Структурная схема логического автомата

по уравнению ФАЛ (1.4)

Обозначение элементов, входящих в схему логического автомата (DD1.1), состоит изDD– микросхема дискретных сигналов, 1 – номер корпуса, 1 – номер элемента в корпусе. Для инверторов, образующих шины входных переменных, используются элементыDD1.1…DD1.4.

Первое

элементарное логическое произведение

![]() содержит три сомножителя, следовательно,

для реализации этого действия на

элементах 2И-НЕ следует применить схему

по рис. 16 (элементыDD2.1 –DD1.3).

содержит три сомножителя, следовательно,

для реализации этого действия на

элементах 2И-НЕ следует применить схему

по рис. 16 (элементыDD2.1 –DD1.3).

Втрое

слагаемое в уравнении ФАЛ

![]() требует выполнения нескольких действий.

Во-первых, сложение в скобках. Сложение

на элементах 2И-НЕ можно осуществить по

принципу двойственности (теорема

Де-Моргана, рис. 4). Для этого на входы

элемента 2И-НЕ следует подать инверсные

сигналы

требует выполнения нескольких действий.

Во-первых, сложение в скобках. Сложение

на элементах 2И-НЕ можно осуществить по

принципу двойственности (теорема

Де-Моргана, рис. 4). Для этого на входы

элемента 2И-НЕ следует подать инверсные

сигналы![]() и

и![]() ,

которые следует взять с соответствующих

шин входных переменных. На выходе

элементаDD2.4 получим

результат

,

которые следует взять с соответствующих

шин входных переменных. На выходе

элементаDD2.4 получим

результат![]() .

Во – вторых, логическое перемножение.

В этом действии участвуют три сомножителя,

поэтому следует воспользоваться схемой

по рис. 16 (элементыDD3.1 –DD3.3).

.

Во – вторых, логическое перемножение.

В этом действии участвуют три сомножителя,

поэтому следует воспользоваться схемой

по рис. 16 (элементыDD3.1 –DD3.3).

Третье

слагаемое в уравнении ФАЛ

![]() также требует выполнения нескольких

действий. Во-первых, умножение в скобках.

В каждом умножении в скобках участвуют

по два сомножителя, следовательно,

элементы 2И-НЕDD4.1,DD4.3

реализуют эти операции. Во – вторых,

сложение в скобках. На выходах элементов

после умножения получаются инверсные

сигналы

также требует выполнения нескольких

действий. Во-первых, умножение в скобках.

В каждом умножении в скобках участвуют

по два сомножителя, следовательно,

элементы 2И-НЕDD4.1,DD4.3

реализуют эти операции. Во – вторых,

сложение в скобках. На выходах элементов

после умножения получаются инверсные

сигналы![]() и

и![]() .

Такие сигналы по принципу двойственности

на элементе 2И-НЕ будут логически

складываться, т.е. второе действие в

скобках – логическое сложение –

выполняется на элементеDD4.4.

В – третьих, логическое перемножение.

В этом действии участвуют три сомножителя,

поэтому также следует воспользоваться

схемой по рис. 16 (элементыDD5.1

–DD5.3).

.

Такие сигналы по принципу двойственности

на элементе 2И-НЕ будут логически

складываться, т.е. второе действие в

скобках – логическое сложение –

выполняется на элементеDD4.4.

В – третьих, логическое перемножение.

В этом действии участвуют три сомножителя,

поэтому также следует воспользоваться

схемой по рис. 16 (элементыDD5.1

–DD5.3).

Р ис.

19. Принципиальная электрическая схема

логического автомата на микросхемах

К155ЛА3

ис.

19. Принципиальная электрическая схема

логического автомата на микросхемах

К155ЛА3

Осталось

произвести логическое сложение трёх

слагаемых ФАЛ. На выходах элементов

DD2.3,DD3.3 иDD5.3 присутствуют инверсные

сигналы![]() ,

,![]() и

и![]() соответственно. Такие сигналы по принципу

двойственности на элементе 2И-НЕ будут

логически складываться, но сигналов

три , а входов элемента только два.

Поэтому логическое сложение придётся

делать в два этапа. Сначала складываются

сигналы с выходов элементовDD2.3,DD3.3 на элементеDD3.4.

На выходе элементаDD3.4

получается прямой сигнал

соответственно. Такие сигналы по принципу

двойственности на элементе 2И-НЕ будут

логически складываться, но сигналов

три , а входов элемента только два.

Поэтому логическое сложение придётся

делать в два этапа. Сначала складываются

сигналы с выходов элементовDD2.3,DD3.3 на элементеDD3.4.

На выходе элементаDD3.4

получается прямой сигнал![]() +

+![]() ,

который для сложения надо проинвертировать.

На выходе инвертораDD4.2

получается инверсный сигнал

,

который для сложения надо проинвертировать.

На выходе инвертораDD4.2

получается инверсный сигнал![]() ,

который на элементеDD5.4

складывается с третьим слагаемым. На

выходе элементаDD5.4

получается результатY(прямой сигнал).

,

который на элементеDD5.4

складывается с третьим слагаемым. На

выходе элементаDD5.4

получается результатY(прямой сигнал).

Теперь построим схему логического автомата на элементах 3ИЛИ-НЕ.

Принципиальная электрическая схема логического автомата на микросхемах К155ЛЕ4 представлена на рис. 20.

Построение

схемы также начинается с формирования

шин входных переменных

![]() и

и![]() ,

для чего элементы 3ИЛИ-НЕ превращаются

в инверторы объединением всех трёх

входов. Всего потребуется четыре

инвертора, следовательно, один корпус

будет использован полностью, и ещё один

элемент будет взят из второго корпуса.

,

для чего элементы 3ИЛИ-НЕ превращаются

в инверторы объединением всех трёх

входов. Всего потребуется четыре

инвертора, следовательно, один корпус

будет использован полностью, и ещё один

элемент будет взят из второго корпуса.

Р ис.

20. Принципиальная электрическая схема

логического автомата на микросхемах

К155ЛЕ4

ис.

20. Принципиальная электрическая схема

логического автомата на микросхемах

К155ЛЕ4

Для инверторов, образующих шины входных переменных, используются элементы DD1.1…DD1.3 иDD2.1.

Первое

элементарное логическое произведение

![]() содержит три сомножителя, следовательно,

для реализации этого действия на элементе

3ИЛИ-НЕ (DD2.2) следует

применить принцип двойственности, т.е.

использовать инверсные сигналы

содержит три сомножителя, следовательно,

для реализации этого действия на элементе

3ИЛИ-НЕ (DD2.2) следует

применить принцип двойственности, т.е.

использовать инверсные сигналы![]() ,

,![]() и

и![]() ,

взяв их с соответствующих шин входных

переменных. На выходе элементаDD2.2

получим результат

,

взяв их с соответствующих шин входных

переменных. На выходе элементаDD2.2

получим результат![]() .

.

Втрое

слагаемое в уравнении ФАЛ

![]() требует выполнения нескольких действий.

Во-первых, сложение в скобках. Сложение

двух переменных на элементе 3ИЛИ-НЕ

можно осуществить, объединив два из

трёх входов элемента, получив, таким

образом, двухвходовый (см. рис. 15). На

входы элементаDD2.3 следует

подать прямые сигналы

требует выполнения нескольких действий.

Во-первых, сложение в скобках. Сложение

двух переменных на элементе 3ИЛИ-НЕ

можно осуществить, объединив два из

трёх входов элемента, получив, таким

образом, двухвходовый (см. рис. 15). На

входы элементаDD2.3 следует

подать прямые сигналы![]() и

и![]() .

На выходе элементаDD2.3

получим инверсный сигнал

.

На выходе элементаDD2.3

получим инверсный сигнал![]() .

Во – вторых, логическое перемножение.

По принципу двойственности на элемент

3ИЛИ-НЕ (DD3.1) следует подать

инверсные сигналы. Один такой сигнал

уже сформирован на выходе элементаDD2.3, инверсные сигналы

.

Во – вторых, логическое перемножение.

По принципу двойственности на элемент

3ИЛИ-НЕ (DD3.1) следует подать

инверсные сигналы. Один такой сигнал

уже сформирован на выходе элементаDD2.3, инверсные сигналы![]() и

и![]() берут с соответствующих шин входных

переменных. На выходе элементаDD3.1

получим результат

берут с соответствующих шин входных

переменных. На выходе элементаDD3.1

получим результат![]() .

.

Третье

слагаемое в уравнении ФАЛ

![]() также требует выполнения нескольких

действий. Во-первых, умножение в скобках.

В каждом умножении в скобках участвуют

по два сомножителя, следовательно,

элементы 3ИЛИ-НЕDD3.2 иDD3.3 реализуют эти операции

по принципу двойственности, если на их

входы подать инверсные сигналы. Во –

вторых, сложение в скобках. На выходах

элементов после умножения получаются

прямые сигналы

также требует выполнения нескольких

действий. Во-первых, умножение в скобках.

В каждом умножении в скобках участвуют

по два сомножителя, следовательно,

элементы 3ИЛИ-НЕDD3.2 иDD3.3 реализуют эти операции

по принципу двойственности, если на их

входы подать инверсные сигналы. Во –

вторых, сложение в скобках. На выходах

элементов после умножения получаются

прямые сигналы![]() и

и![]() .

Такие сигналы на элементе 3ИЛИ-НЕ будут

логически складываться, т.е. второе

действие в скобках – логическое сложение

– выполняется на элементеDD4.1,

на выходе которого получается инверсный

сигнал

.

Такие сигналы на элементе 3ИЛИ-НЕ будут

логически складываться, т.е. второе

действие в скобках – логическое сложение

– выполняется на элементеDD4.1,

на выходе которого получается инверсный

сигнал![]() .

В – третьих, логическое перемножение.

По принципу двойственности на элемент

3ИЛИ-НЕ (DD4.2) следует подать

инверсные сигналы. Один такой сигнал

уже сформирован на выходе элементаDD4.1, инверсные сигналы

.

В – третьих, логическое перемножение.

По принципу двойственности на элемент

3ИЛИ-НЕ (DD4.2) следует подать

инверсные сигналы. Один такой сигнал

уже сформирован на выходе элементаDD4.1, инверсные сигналы![]() и

и![]() берут с соответствующих шин входных

переменных. На выходе элементаDD3.1

получим результат

берут с соответствующих шин входных

переменных. На выходе элементаDD3.1

получим результат![]() .

.

Осталось

произвести логическое сложение трёх

слагаемых ФАЛ. На выходах элементов

DD2.2,DD3.1 иDD4.2 присутствуют прямые

сигналы, поэтому они подаются на входы

элементаDD4.3, на выходе

которого получается инверсный сигнал![]() .

Для получения прямого сигнала следует

добавить ещё один инверторDD5.1.

На его выходе будет требуемый результатY.

.

Для получения прямого сигнала следует

добавить ещё один инверторDD5.1.

На его выходе будет требуемый результатY.