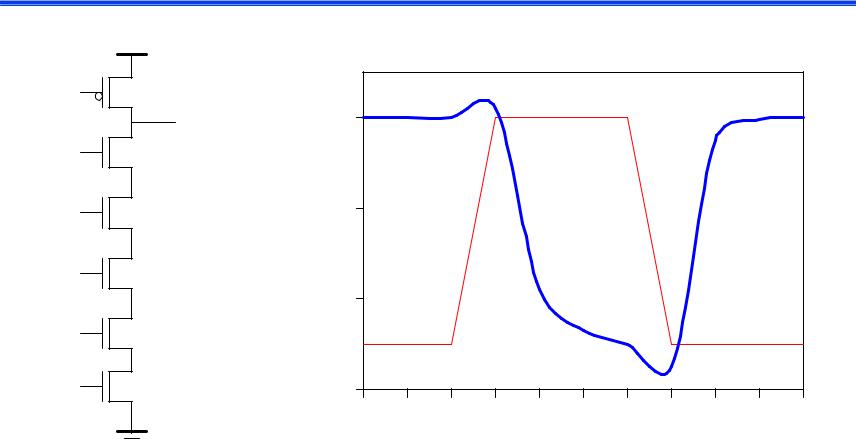

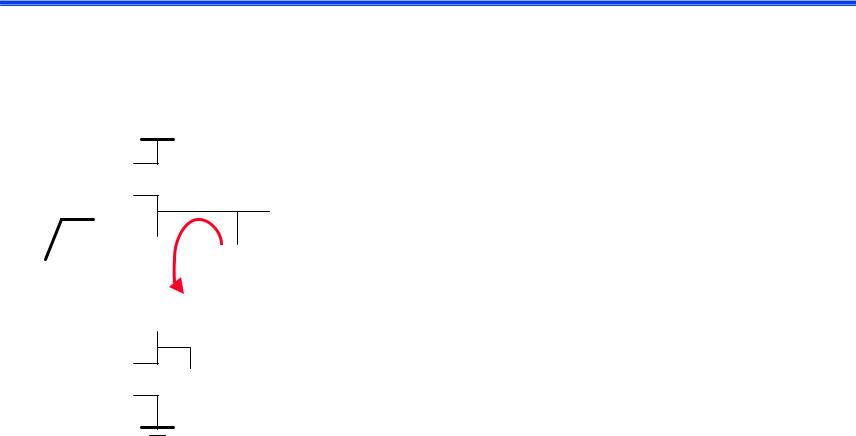

Dynamic Behavior |

|

|

|

||

CLK |

|

2.5 |

|

|

|

Out |

|

|

Evaluate |

|

|

|

|

|

|

||

In1 |

|

|

|

|

|

In2 |

Voltage |

1.5 |

|

|

|

In3 |

0.5 |

In & |

|

|

|

|

|

|

|

||

In4 |

|

|

CLK |

Out |

Precharge |

CLK |

|

|

|

||

|

-0.5 |

|

|

|

|

|

|

0 |

|

0.5 |

1 |

Time, ns

#Trns |

VOH |

VOL |

VM |

NMH |

NML |

tpHL |

tpLH |

tp |

6 |

2.5V |

0V |

VTn |

2.5-VTn |

VTn |

110ps |

0ns |

83ps |

CSE477 L# topic.11 |

Irwin&Vijay, PSU, 2001 |

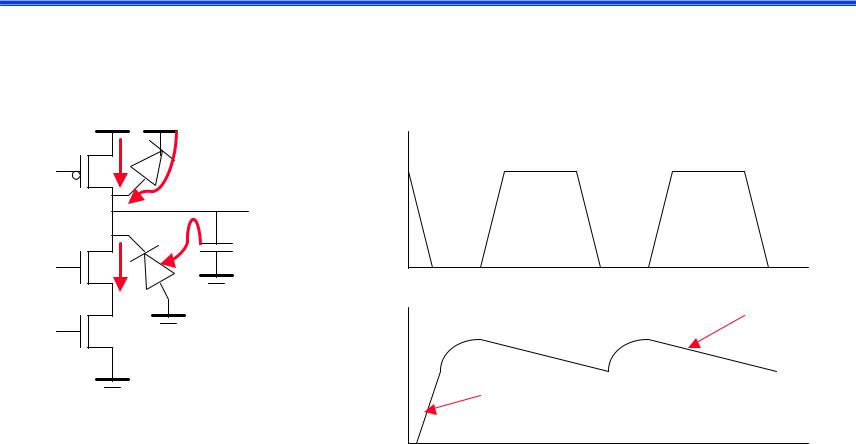

Power Consumption of Dynamic Gate

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

Mp |

|||||||||||||

|

|

|

|

|

|||||||||||||||

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

In1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CL |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

In2 |

|

|

|

|

|

PDN |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

In3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

Me |

|||||||||||||

|

|

|

|

|

|||||||||||||||

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power only dissipated when previous Out = 0

CSE477 L# topic.12 |

Irwin&Vijay, PSU, 2001 |

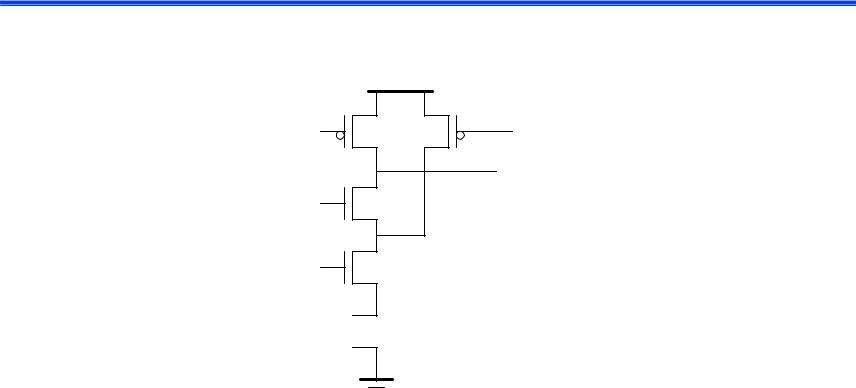

Dynamic Power Consumption is Data Dependent

Dynamic 2-input NOR Gate

|

|

|

Assume signal probabilities |

||

A |

B |

Out |

PA=1 = 1/2 |

|

|

|

|

|

|

||

0 |

0 |

1 |

PB=1 = 1/2 |

|

|

0 |

1 |

0 |

Then transition probability |

||

|

|

|

|||

1 |

0 |

0 |

|||

P0→1 = Pout=0 |

x Pout=1 |

||||

|

|

|

|||

1 |

1 |

0 |

|||

|

|

||||

|

|

|

= 3/4 x |

1 = 3/4 |

|

|

|

|

|||

Switching activity always higher in dynamic gates!

P0→1 = Pout=0

CSE477 L# topic.13 |

Irwin&Vijay, PSU, 2001 |

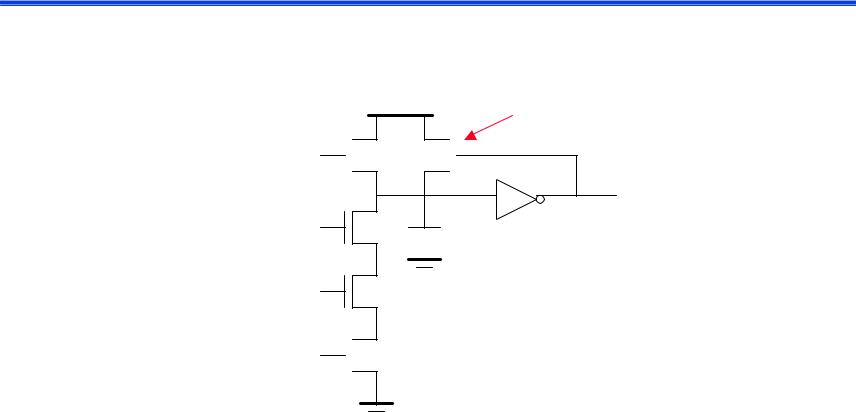

Issues in Dynamic Design 1: Charge Leakage

CLK

|

4 |

CLK |

3 |

Mp |

Out

|

1 |

|

A |

CL |

|

|

2 |

Evaluate |

CLK |

VOut |

|

Me |

|

|

|

|

Precharge |

Leakage sources |

|

|

Minimum clock rate of a few kHz

CSE477 L# topic.14 |

Irwin&Vijay, PSU, 2001 |

Solution to Charge Leakage

Keeper

CLK

Mp Mkp

Mp Mkp

A

!Out

CL

CL

B

CLK

Me

Me

Same approach as level restorer for pass transistor logic

CSE477 L# topic.15 |

Irwin&Vijay, PSU, 2001 |

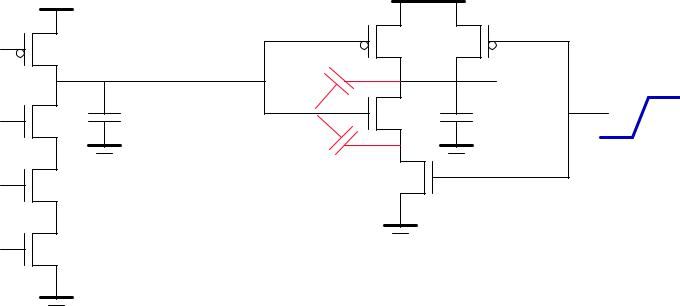

Issues in Dynamic Design 2: Charge Sharing

CLK

Mp

Mp

Out

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

CL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

B=0 |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

CA |

|||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|||||||||||

CLK

Me

Me  CB

CB

Charge stored originally on CL is redistributed (shared) over CL and CA leading to static power consumption by downstream gates and possible circuit malfunction.

CSE477 L# topic.16 |

Irwin&Vijay, PSU, 2001 |

Charge Sharing Example

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Out |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

!A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CL=50fF |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ca=15fF |

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

!B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

!B |

|

|

|

|

|

|

|

|

|

|

|

Cb=15fF |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cc=10fF |

|

|

|

|

|

|

!C |

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cd=10fF |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vout = - VDD (Ca / (Ca + CL ))

CSE477 L# topic.17 |

Irwin&Vijay, PSU, 2001 |

Solution to Charge Redistribution

CLK Mp Mkp |

CLK |

A |

Out |

|

B

CLK

Me

Me

Precharge internal nodes using a clockdriven transistor (at the cost of increased area and power)

CSE477 L# topic.18 |

Irwin&Vijay, PSU, 2001 |

Issues in Dynamic Design 3: Backgate Coupling

CLK |

Mp |

Out1 =1 |

Out2 =0 |

|

|

|

|

A=0 |

|

CL1 |

In |

|

CL2 |

||

B=0 |

|

|

|

CLK |

Me |

|

|

Dynamic NAND |

Static NAND |

CSE477 L# topic.19 |

Irwin&Vijay, PSU, 2001 |

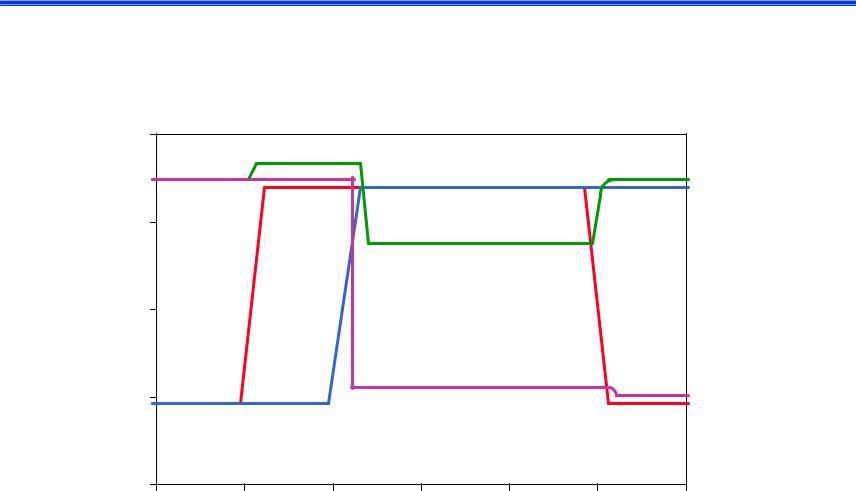

Backgate Coupling Effect

|

|

3 |

|

|

|

|

|

|

2 |

|

|

|

|

|

Voltage |

|

|

Out1 |

|

|

|

1 |

CLK |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

0 |

In |

Out2 |

|

|

|

|

|

|

|

||

|

|

-1 |

|

|

|

|

|

|

0 |

2 |

Time, ns |

4 |

6 |

CSE477 |

L# topic.20 |

|

|

|

|

Irwin&Vijay, PSU, 2001 |