- •Встроенные микропроцессорные системы

- •Оглавление

- •2. Программное обеспечение встроенных систем ……….

- •Введение

- •Модуль 1

- •Аппаратные средства встроенных систем

- •1.2. Элементы архитектуры процессоров встроенных систем

- •1.2.1. Множество команд

- •1.2.3.1. Адресное пространство

- •1.2.3.2. Порядок байт

- •1. 2.3.3. Когерентность памяти

- •1. 2.3.4. Защита памяти

- •1. 2. 4. Модель прерываний

- •1.2. 5.Модель управления памятью

- •1.2.5.1. Страничная организация памяти

- •1.2.5.2. Сегментация памяти

- •1.3. Типы процессоров

- •1.4. Формы параллелизма в процессорах

- •1.4.1. Конвейеризация

- •1.4.2. Параллелизм уровня команд

- •1.5.Технологии памяти

- •1.5.1. Оперативная память

- •1.5.1. 1. Статическое озу

- •1.5.2. Постоянное запоминающее устройство (rom)

- •1.6. Иерархия памяти

- •1.6.1. Распределение или карта памяти

- •1.6.2. Блокнотная и кэш память

- •1.6.2.1. Кэш-память прямого отображения

- •1.6.2.2. Ассоциативная по множеству кэш-память

- •1.6.2.3. Обновление кэш-памяти.

- •1.6.2.4. Протокол когерентности кэширования с обратной записью

- •1.7. Магистраль микропроцессорной системы

- •1.8. Базовые устройства ввода-вывода встроенных систем

- •1.8.1. Порты ввода-вывода общего назначения

- •1.7.2. Таймер-счетчик

- •1.8.3. Импульсно-кодовая модуляция.

- •1.8.4. Многоканальный аналого-цифровой преобразователь

- •1.9. Базовые последовательные интерфейсы ввода-вывода

- •1.9.2. Последовательный интерфейс spi

- •1.9.4.1. Введение в usb

- •1.9.4.2. Интерфейс Open Host Controller для usb

- •Вопросы для самоконтроля

- •Модуль 2

- •1.10. Язык проектирования аппаратуры vhdl

- •1.10.2. Введение в vhdl

- •1.10.2.1. Программирование на vhdl для моделирования и синтеза [19]

- •1.10.2.2. Entity и architecture

- •1.10.2.3. Операторы присваивание и process [19]

- •1.10.2.4. Цикл моделирования vhdl

- •1.10.2.5. Многозначная логика и стандарт ieee 1164

- •1.11. Проектирование устройств ввода-вывода и контроллеров

- •1.12. Интегрированная среда разработки аппаратных средств

- •Вопросы для самоконтроля

- •Модуль 3

- •2. Программное обеспечение встроенных систем

- •2.1 Модель вычислений

- •2.2 Автомат с конечным числом состояний

- •2.3. Асинхронный язык проектирования sdl

- •2.4. Синхронный язык проектирования Lustre

- •2.5. Многозадачность.

- •2.5.1. Язык программирования Си

- •2.5.2. Потоки

- •2.5.2.1. Реализация потоков

- •2.5.2.2. Взаимное исключение

- •2.5.2.3. Взаимная блокировка

- •2.5.2.4. Модели непротиворечивости памяти

- •2.5.2.5. Проблемы с потоками

- •2.5.3. Процессы и передача сообщений

- •2.6. Интегрированная среда разработки прикладного программного

- •2.6.2. Комплект программ Telelogic Tau sdl Suite

- •2.6.3. Средства разработки программного обеспечения

- •2.7.1. Моделирование, эмуляция и макетирование

- •2.7.2. Формальная верификация

- •2.7.3. Оценка производительности

- •2.7.3.1. Оценка wcet

- •2.7.3.2. Исчисление реального времени

- •1 2 3 E

- •2.7.4. Модели энергии и мощности

- •2.7.5. Тепловая модель

- •Вопросы для самоконтроля

- •Заключение

- •Задания

- •1. Конвейеризация

- •2. Иерархия памяти

- •3. Базовые устройства ввода-вывода встроенных систем

- •5. Многозадачность

- •6. Валидация и оценка проекта

- •Библиографический список

- •Встроенные микропроцессорные системы

1.10.2.4. Цикл моделирования vhdl

В соответствии со стандартом [20] выполнение модели в VHDL описывается следующим образом.

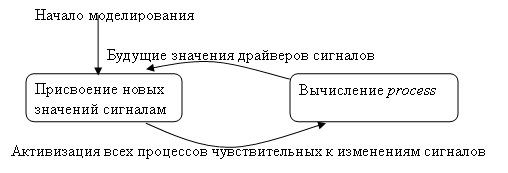

Выполнение модели состоит из фазы инициализации с последующим повторяющимся выполнением операторов process и параллельных операторов присвоения, описанных в модели. Каждое такое повторение называется циклом моделирования. В каждом цикле вычисляются значения сигналов, присутствующих в описании. Если в результате вычисления данный сигнал меняет свое значение, то оператор process чувствительный к этому сигналу будет выполнен как часть цикла моделирования.

В фазе инициализации, оговоренные начальные значения присваиваются сигналам, текущему модельному времени Tc присваивается значение 0 и однократно выполняется каждый оператор process.

Каждый цикл моделирования начинается с установки текущего времени в следующий момент времени, на который назначены изменения значений сигналов. Это время Tn было вычислено во время инициализации или последнего выполнения цикла моделирования. Моделирование прекращается, когда текущее время достигнет установленного максимума.

Каждый цикл моделирования содержит следующие шаги:

а) Tc присваивается Tn.

б) Каждый сигнал явно заданный в модели обновляется (в результате могут появиться события, если сигналы меняют свое значение).

В цикле, предшествовавшем текущему циклу, были вычислены новые будущие значения. Если Tc соответствует времени, в которое эти значения становятся действительными, то они и присваиваются сигналам. Новые значения никогда сразу не присваиваются в выполняемом цикле моделирования. Сигналы, которые изменяют свое значение, генерируют события, которые в свою очередь могут запустить выполнение операторов process, чувствительных к этим сигналам.

в) Для каждого process P, если P чувствителен к сигналу S и если событие имеет место для сигнала S в этом цикле моделирования, тогда P выполняется.

г) Каждый process, который получил разрешение на выполнение в текущем цикле выполняется до момента простановки.

д) Время следующего цикла Tn определяется установкой его в наиболее раннее из значений:

1) TIME’HIGH – время окончания моделирования.

2) Время, когда драйвер сигнала становится активным (задержка формирования значения сигнала).

3) Время, в которое разрешается выполняться оператору process (это время определяется операторами wait for.

Если Tn = Tc, то следующий цикл моделирования будет δ-циклом.

На рис.53 иллюстрирует итеративную природу цикла моделирования.

Итак, принцип продвижения модельного времени системой моделирования формулируется следующим образом: от момента события до следующего момента модельного времени, в котором происходит хотя бы одно событие, пропуская промежуточные моменты, в которые не происходит никаких событий. В системах моделирования это называют событийным моделированием.

Рис.53. Цикл моделирования VHDL

Транзакция. В реализации сигналов, изменяемых в модельном времени, основным становится планирование в этом времени изменений сигналов. При выполнении операторов присваивания значения сигналу, системой моделирования формируется специальная структура данных, пара: значение сигнала/момент модельного времени, когда сигнал примет это значение. Такая пара в VHDL называется транзакцией. Транзакция – это внутренняя инструкция системы моделирования по изменению указанного сигнала в заданный момент модельного времени.

В реализации языка VHDL запланированная источником временная диаграмма сигнала представляется упорядоченным списком транзакций, формирующих моменты изменения сигнала на временной диаграмме. Часто в описании VHDL именно этот список, связанный с одним источником сигнала называют драйвером.