- •Встроенные микропроцессорные системы

- •Оглавление

- •2. Программное обеспечение встроенных систем ……….

- •Введение

- •Модуль 1

- •Аппаратные средства встроенных систем

- •1.2. Элементы архитектуры процессоров встроенных систем

- •1.2.1. Множество команд

- •1.2.3.1. Адресное пространство

- •1.2.3.2. Порядок байт

- •1. 2.3.3. Когерентность памяти

- •1. 2.3.4. Защита памяти

- •1. 2. 4. Модель прерываний

- •1.2. 5.Модель управления памятью

- •1.2.5.1. Страничная организация памяти

- •1.2.5.2. Сегментация памяти

- •1.3. Типы процессоров

- •1.4. Формы параллелизма в процессорах

- •1.4.1. Конвейеризация

- •1.4.2. Параллелизм уровня команд

- •1.5.Технологии памяти

- •1.5.1. Оперативная память

- •1.5.1. 1. Статическое озу

- •1.5.2. Постоянное запоминающее устройство (rom)

- •1.6. Иерархия памяти

- •1.6.1. Распределение или карта памяти

- •1.6.2. Блокнотная и кэш память

- •1.6.2.1. Кэш-память прямого отображения

- •1.6.2.2. Ассоциативная по множеству кэш-память

- •1.6.2.3. Обновление кэш-памяти.

- •1.6.2.4. Протокол когерентности кэширования с обратной записью

- •1.7. Магистраль микропроцессорной системы

- •1.8. Базовые устройства ввода-вывода встроенных систем

- •1.8.1. Порты ввода-вывода общего назначения

- •1.7.2. Таймер-счетчик

- •1.8.3. Импульсно-кодовая модуляция.

- •1.8.4. Многоканальный аналого-цифровой преобразователь

- •1.9. Базовые последовательные интерфейсы ввода-вывода

- •1.9.2. Последовательный интерфейс spi

- •1.9.4.1. Введение в usb

- •1.9.4.2. Интерфейс Open Host Controller для usb

- •Вопросы для самоконтроля

- •Модуль 2

- •1.10. Язык проектирования аппаратуры vhdl

- •1.10.2. Введение в vhdl

- •1.10.2.1. Программирование на vhdl для моделирования и синтеза [19]

- •1.10.2.2. Entity и architecture

- •1.10.2.3. Операторы присваивание и process [19]

- •1.10.2.4. Цикл моделирования vhdl

- •1.10.2.5. Многозначная логика и стандарт ieee 1164

- •1.11. Проектирование устройств ввода-вывода и контроллеров

- •1.12. Интегрированная среда разработки аппаратных средств

- •Вопросы для самоконтроля

- •Модуль 3

- •2. Программное обеспечение встроенных систем

- •2.1 Модель вычислений

- •2.2 Автомат с конечным числом состояний

- •2.3. Асинхронный язык проектирования sdl

- •2.4. Синхронный язык проектирования Lustre

- •2.5. Многозадачность.

- •2.5.1. Язык программирования Си

- •2.5.2. Потоки

- •2.5.2.1. Реализация потоков

- •2.5.2.2. Взаимное исключение

- •2.5.2.3. Взаимная блокировка

- •2.5.2.4. Модели непротиворечивости памяти

- •2.5.2.5. Проблемы с потоками

- •2.5.3. Процессы и передача сообщений

- •2.6. Интегрированная среда разработки прикладного программного

- •2.6.2. Комплект программ Telelogic Tau sdl Suite

- •2.6.3. Средства разработки программного обеспечения

- •2.7.1. Моделирование, эмуляция и макетирование

- •2.7.2. Формальная верификация

- •2.7.3. Оценка производительности

- •2.7.3.1. Оценка wcet

- •2.7.3.2. Исчисление реального времени

- •1 2 3 E

- •2.7.4. Модели энергии и мощности

- •2.7.5. Тепловая модель

- •Вопросы для самоконтроля

- •Заключение

- •Задания

- •1. Конвейеризация

- •2. Иерархия памяти

- •3. Базовые устройства ввода-вывода встроенных систем

- •5. Многозадачность

- •6. Валидация и оценка проекта

- •Библиографический список

- •Встроенные микропроцессорные системы

1.5.Технологии памяти

Выбор технологии памяти имеет важное последствие для разработчика встроенной системы. Например, программиста беспокоит изменяться или нет данные после выключения питания или вхождения в режим энергосбережения. Память, содержимое которой теряется после пропадания питания, называют энергозависимой памятью (volatile memory). Обычно с ней ассоциируют оперативную память или память с произвольным доступом (RAM).

Встроенные системы без исключения нуждаются в сохранении данных даже при выключенном питании. Для этого существует несколько опций. Резервное батарейное питание является одной из них при котором энергия не исчезает. Батареи, однако, срабатываются, следовательно, требуется более совершенная опция в собирательном смысле известная как энергонезависимая память (non-volatile memory).Обычно с ней ассоциируют постоянную память (ROM).

1.5.1. Оперативная память

RAM (Random Access Memory) – память, в которой единицы данных (байты или слова) могут быть записаны и считаны относительно быстро. Статическая память SRAM (Static RAM) работает быстрее динамической памяти DRAM (Dynamic RAM), но больше по размеру (каждый бит занимает большую площадь на кристалле).

1.5.1. 1. Статическое озу

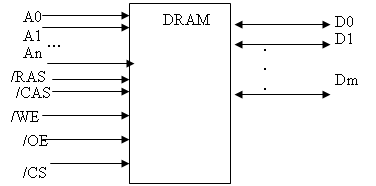

SRAM конструируется с использованием D-триггеров. В лучшем случае требуется 6 МОП транзисторов на триггер, что препятствует созданию больших массивов ячеек на кристалле (обычно до нескольких миллионов байт). Информация сохраняется на протяжении всего времени, пока на SRAM подано питание. SRAM работает очень быстро. Обычно время доступа составляет несколько наносекунд. Поэтому SRAM часто используют в качестве кэш-памяти второго уровня. На рис.9 приведен интерфейс с SRAM.

MPS может содержать несколько микросхем SRAM. Поэтому в интерфейс нужен сигнал для выбора одной из них, такой чтобы только нужная микросхема реагировала на обращение. Сигнал /CS (Chip Select – выбор кристалла) используется для этой цели. “/” означает, что активное значение сигнала равно 0.

По сигнал /WE (Write Enable – разрешение записи) выбранная микросхема SRAM записывает данные с линий D0 … Dm в ячейку, двоичный адрес которой установлен на линиях A0 … An.

Рис.9. Интерфейс микросхемы статического ОЗУ

По сигналу /OE (Output Enable – разрешение выдачи данных) выбранная микросхема SRAM выставляет данные на линии D0 … Dm из ячейки, двоичный адрес которой установлен на линиях A0 … An.

На рис. 10 приведена временная диаграмма цикла записи SRAM. Время установки (setup time) определяет минимальное время для подачи сигнала /WE после установки линий адреса (время необходимое для дешифрации адреса ячейки).

Время сохранения (hold time) определяет минимальное время до очередного изменения адресных линий после снятия сигнала /WE (время необходимое для предотвращения перезаписи данных в другую ячейку).

На рис. 11 приведена временная диаграмма цикла чтения статического ОЗУ.

Рис. 10 . Временная диаграмма цикла записи статического ОЗУ

Рис. 11. Временная диаграмма цикла чтения статического ОЗУ

1.5.1. 2. Динамическое ОЗУ

В динамическом ОЗУ (DRAM) в качестве запоминающего элемента используется паразитная емкость pn-перехода, которая через МОП транзистор может быть подключена к схемам чтения или записи. На рис.12 приведена модель динамического ОЗУ, организованного в виде матрицы.

Рис.12. Модель динамического ОЗУ

Конденсатор С может быть заряжен или разряжен, что позволяет говорить о хранении 0 или 1. Электрический заряд конденсатора стекает за несколько десятков миллисекунд, поэтому каждый бит информации должен обновляться (регенерировать) для предотвращения разрушения данных.

Во время выборки строки все соответствующие транзисторы открываются, и конденсаторы строки разряжаются. Токи разряда поступают на входы запоминающих усилителей считывания, формируя на их выходах соответствующие напряжения 0 или 1. Таким образом, и при обращении к строке данные разрушаются. Поэтому перед выборкой следующей строки, данные должны быть перезаписаны из запоминающих усилителей считывания в ранее выбранную строку.

В динамическое ОЗУ на каждый бит требуется один конденсатор и один транзистор, поэтому такое ОЗУ имеет высокую плотность данных. Поэтому MM во многих MPS строится на основе динамического ОЗУ. Однако динамическое ОЗУ работает значительно медленнее. Таким образом, сочетание кэш-памяти на основе статического ОЗУ и MM на основе динамического ОЗУ соединяет в себе преимущества обоих устройств.

Существует несколько типов динамических ОЗУ. Самый старый называется FPM (Fast Page Mode – быстрый страничный режим). Под страницей динамического ОЗУ понимают все множество ячеек памяти, принадлежащих одной строке. На смену FPM пришла EDO (Extended Data Output – память с расширенными возможностями выходов данных) с конвейеризацией адресов и данных, что увеличило пропускную способность памяти.

Оба эти типа динамических ОЗУ являются асинхронными. На рис.13 приведен интерфейс микросхем асинхронных динамических ОЗУ. Первой выбирается строка. Для этого номер строки помещается на адресные выводы А0…Аn. Затем устанавливается сигнал /RAS (Row Address Strob – строб адреса строки). После этого на адресные выводы подается номер столбца и устанавливается сигнал /CAS (Colum Address Strob). И, наконец, сигналы /OE или /WE.

Рис.13. Интерфейс микросхемы асинхронного динамического ОЗУ

Регенерация всех ячеек строки выполняется установкой ее номера на адресных линиях и сигналов /RAS и /CAS (алгоритм CBR – Cas Befor Ras, т.е. /CAS устанавливается чуть раньше /RAS). В течении нескольких миллисекунд необходимо перебрать все строки и вся память будет регенерирована.

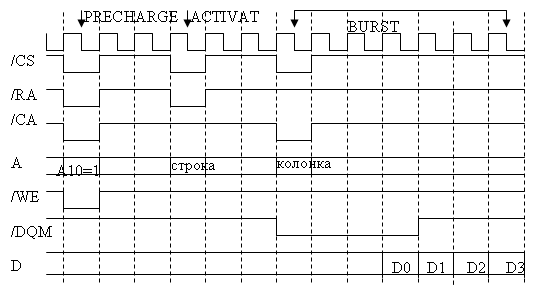

На смену асинхронным пришли синхронные динамическим ОЗУ (SDRAM), все действия в которых происходят по фронту или срезу синхронизирующего сигнала CLK. С целью совмещения операций ячейки сгруппированы в несколько банков (обычно 4) – расслоение или чередование (interleaving) памяти. Это дает возможность повысить производительность памяти. На рис.14 приведен интерфейс микросхем SDRAM.

Рассмотрим взаимодействие с SDRAM стандарта JDEC. Ниже приведены

интерфейсные команды этого стандарта.

BANK-ACTIVATE: запоминание адреса строки. Содержимое строки (страница) считывается в запоминающие усилители считывания. Такую стра ницу называют открытой.

MODE-SET: установка параметров SDRAM (передаются через адресныелинии). Скрытый период после сигнала CAS (CAS latency - CL) – задержка выдачи данных после сигнала CAS (1,2,3, … такта). Блочный режим передачи (burst) и длина блока – последовательная передача соседних данных. Длина блока (BL) может быть 1,2,4,8 слов или страница. На рис.15 приведен формат слова параметров. Слово параметров SDRAM устанавливается на линиях адреса и сопровождается установкой сигналов /RAS, /CAS и /WE.

PRECHARGE (SINGLEBANK/ALLBANKS): перезапись данных из усилителей считывания в соответствующую строку. Эта команда должна выполняться всякий раз после записи или чтения, если адрес строки изменяется при следующем доступе. Выполнение команды PRECHARGE при А10=1 приводит к перезаписи выбранной строки во всех банках.

Рис.14. Интерфейс микросхемы синхронного динамического ОЗУ

Рис.15. Формат слова параметров SDRAM

READ: запоминание адреса колонки и передача данных из выбранных усилителей считывания в выходной буфер. В конце блочной передачи выбранная страница остается открытой.

REFRESH: чтение строки во всех банках. Номер строки определяется внутренним регенерационным счетчиком адреса строки. После начала чтения строка автоматически перезаписывается. Все банки перед регенерацией должны быть в состояние PRECHARGE.

Регенерация очередной страницы запускается установкой сигналов /RAS и /CAS (алгоритм CBR).

WRITE: запоминание адреса колонки и передача данных с линий D

в выбранные усилители считывания. Во время каждого последующего тактового импульса при блочной передаче данные запоминаются без дополнительной операции WRITE. В конце блочной передачи выбранная страница остается открытой.

SDRAM поддерживает плотный (back-to-back) страничный режим доступа. Это означает, что страница остается открытой пока доступ вплотную осуществляется к ячейкам в пределах открытой страницы или пока магистраль не начнет выполнять холостые циклы.

SDRAM поддерживает конвейеризацию. Это означает, что доступ к следующим данным может происходить минимум через 0 тактов.

SDRAM поддерживает расслоение банков. Это означает, что если происходит обращение к другой странице в другом банке, то сначала выдается команда BANK-ACTIVATE для новой страницы, а затем PRECHARGE для старой страницы. Это уменьшает накладные расходы, связанные с де активизацией старой страницы.

Существует два варианта перекрытия внутренних банков SDRAM. Первый называют перекрытием страниц. В этом случае адрес ячейки памяти структурируется следующим образом (слева старшая часть адреса):

номер строки – номер банка – номер колонки.

В случае варианта с перекрытием банков адрес ячейки памяти структурируется следующим образом:

номер банка - номер строки – номер колонки.

Первый вариант обеспечивает большую производительность. На рис.16 приведена временная диаграмма чтения блока данных (BL=4, CL=3) при промахе страницы. Сначала де активизируется ранее выбранная страница, затем активизируется новая страница. Установка сигналов /CAS и /DQM запускают чтение четырех рядом расположенных слов.

SDRAM выполняет блочную передачу для каждой транзакции. При чтении, если требуется данных меньше чем длина блока, то инициатор транзакции игнорирует ненужные прочитанные данные. При записи, если требуется записать меньше данных, чем длина блока, инициатор транзакции подавляет запись лишних данных сбросом линий /DQM. На рис.17 приведена временная диаграмма конвейеризованных транзакций чтения после записи к открытой странице

.

Рис.16. Временная диаграмма чтения блока данных (BL=4,CL=3)

Рис.17. Временная диаграмма конвейеризованных транзакций чтения после записи к открытой странице